CY7C1512 查看數據表(PDF) - Cypress Semiconductor

零件编号

产品描述 (功能)

生产厂家

CY7C1512 Datasheet PDF : 8 Pages

| |||

PRELIMINARY

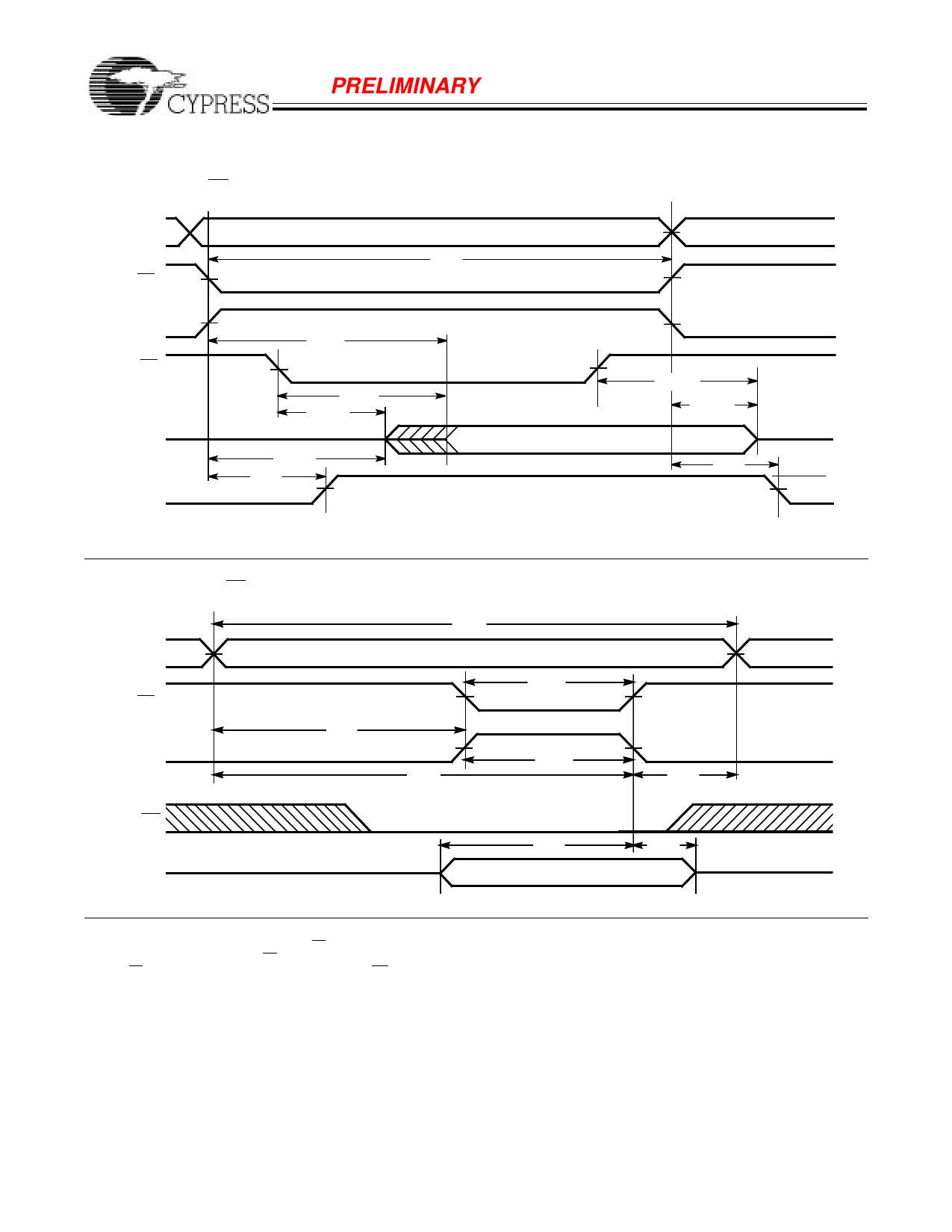

Switching Waveforms (continued)

Read Cycle No. 2 (OE Controlled) [11, 12]

ADDRESS

CE1

CE2

OE

DATA OUT

VCC

SUPPLY

CURRENT

tRC

tACE

tDOE

tLZOE

HIGH IMPEDANCE

tLZCE

tPU

50%

CY7C1512

DATA VALID

tHZOE

tHZCE

HIGH

IMPEDANCE

tPD

50%

ICC

ISB

1512-6

Write Cycle No. 1 (CE1 or CE2 Controlled) [13, 14]

tWC

ADDRESS

CE1

CE2

WE

tSA

tAW

DATA I/O

tSCE

tSCE

tSD

DATA VALID

tHA

tHD

Notes:

12. Address valid prior to or coincident with CE1 transition LOW and CE2 transition HIGH.

13. Data I/O is high impedance if OE = VIH.

14. If CE1 goes HIGH or CE2 goes LOW simultaneously with WE going HIGH, the output remains in a high-impedance state.

1512-7

5