CA3310(2001) 查看數據表(PDF) - Intersil

零件编号

产品描述 (功能)

生产厂家

CA3310 Datasheet PDF : 16 Pages

| |||

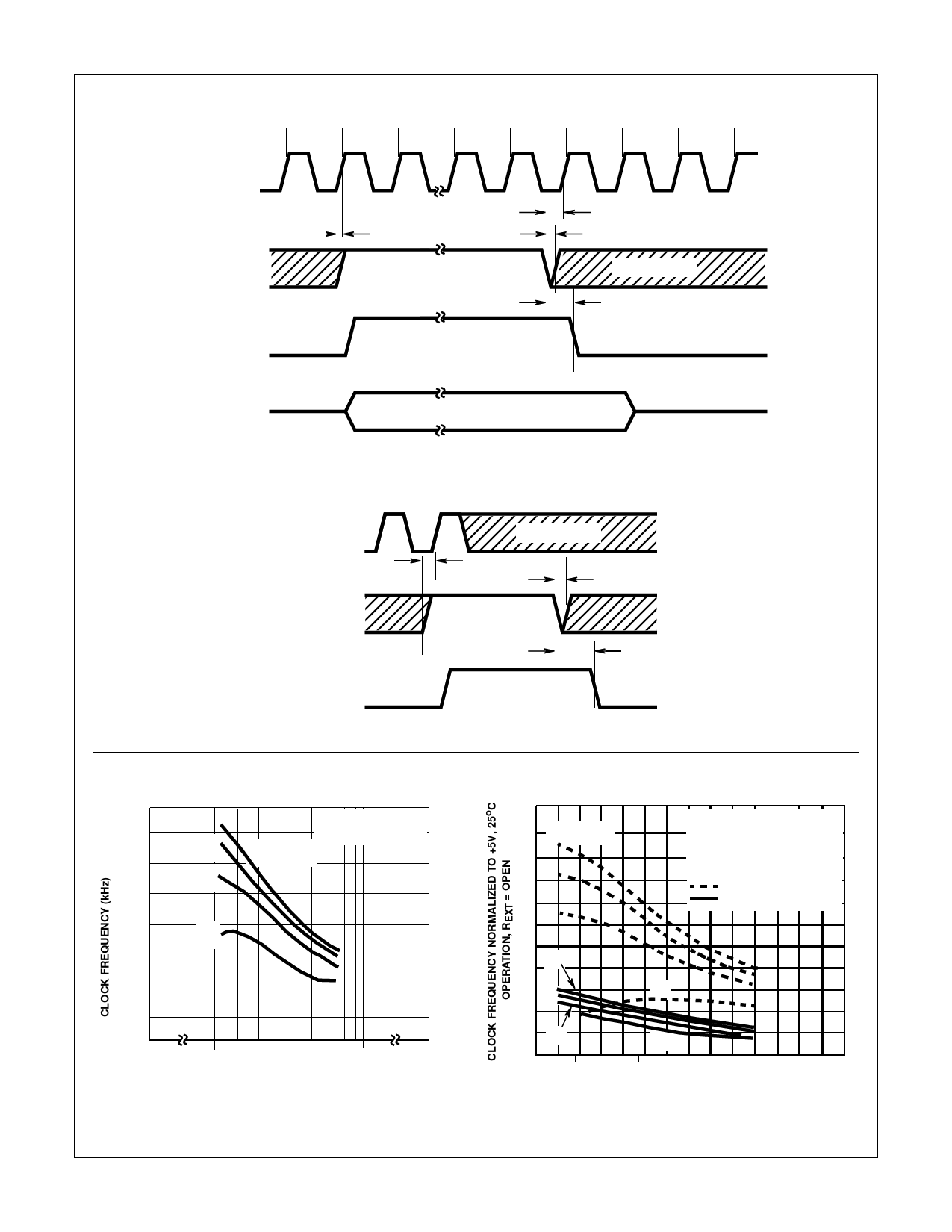

Timing Diagrams (Continued)

13

CLK

(EXTERNAL)

STRT

DRDY

CA3310, CA3310A

1

2

2

2

3

4

5

tR STRT

tSU STRT

tW STRT

DON’T CARE

tD3 DRDY

INPUT

HOLD

TRACK

HOLD

FIGURE 4. STRT PULSED LOW, DRST TIED HIGH, EXTERNAL CLOCK

13

CLK

(INTERNAL

OR

EXTERNAL)

DRST

1

DON’T CARE

tR DRST

tW DRST

DRDY

tD4

DRDY

FIGURE 5. DRST PULSED LOW, STRT TIED HIGH

Typical Performances Curves

800

700

VDD = 3V - 6V = VAA+

5V

VDD = 6V

600

4V

500

400

3V

300

200

100

0

SHORT

10

100

1000

EXTERNAL RESISTANCE (kΩ)

OPEN

FIGURE 6. INTERNAL CLOCK FREQUENCY vs EXTERNAL

RESISTANCE

5

VDD = 6V

4 5V

4V

3

VDD = VAA+ = 3V - 6V

INTERNAL CLOCK MAY NOT

WORK AT VDD < 4V FOR

TEMPERATURE < -40oC

REXT = SHORTED

REXT = OPEN

6V

2

5V

3V

1

4V

0

-55 -40

3V

0 25

85

125

TEMPERATURE (oC)

FIGURE 7. INTERNAL CLOCK FREQUENCY vs

TEMPERATURE AND SUPPLY VOLTAGE

7