N74F842N(2004) 查看數據表(PDF) - Philips Electronics

零件编号

产品描述 (功能)

生产厂家

N74F842N

(Rev.:2004)

(Rev.:2004)

Philips Electronics

N74F842N Datasheet PDF : 12 Pages

| |||

Philips Semiconductors

10-bit bus interface latches, non-inverting/inverting

(3-State)

Product data

74F841/74F842

FEATURES

• High speed parallel latches

• Extra data width for wide address/data paths or buses carrying

parity

• High impedance NPN base input structure minimizes bus loading

• IIL is 20 µA for minimum bus loading

• Buffered control inputs to reduce AC effects

• Ideal where high speed, light loading, or increased fan-in are

required as with MOS microprocessors

• Positive and negative over-shoots are clamped to ground

• 3-State outputs glitch free during power-up and power-down

• 48 mA sink current

• Slim dual in-line 300 mil package

• Broadside pinout

DESCRIPTION

The 74F841 and 74F842 bus interface latches are designed to

provide extra data width for wider address/data paths of buses

carrying parity.

The 74F841 consists of ten D-type latches with 3-State outputs.

The flip-flops appear transparent to the data when Latch Enable

(LE) is HIGH. This allows asynchronous operation, as the output

transition follows the data in transition. On the LE HIGH-to-LOW

transition, the data that meets the set-up and hold time is latched.

Data appears on the bus when the Output Enable (OE) is LOW.

When OE is HIGH the output is in the high-impedance state.

The 74F842 is the inverted output version of the 74F841.

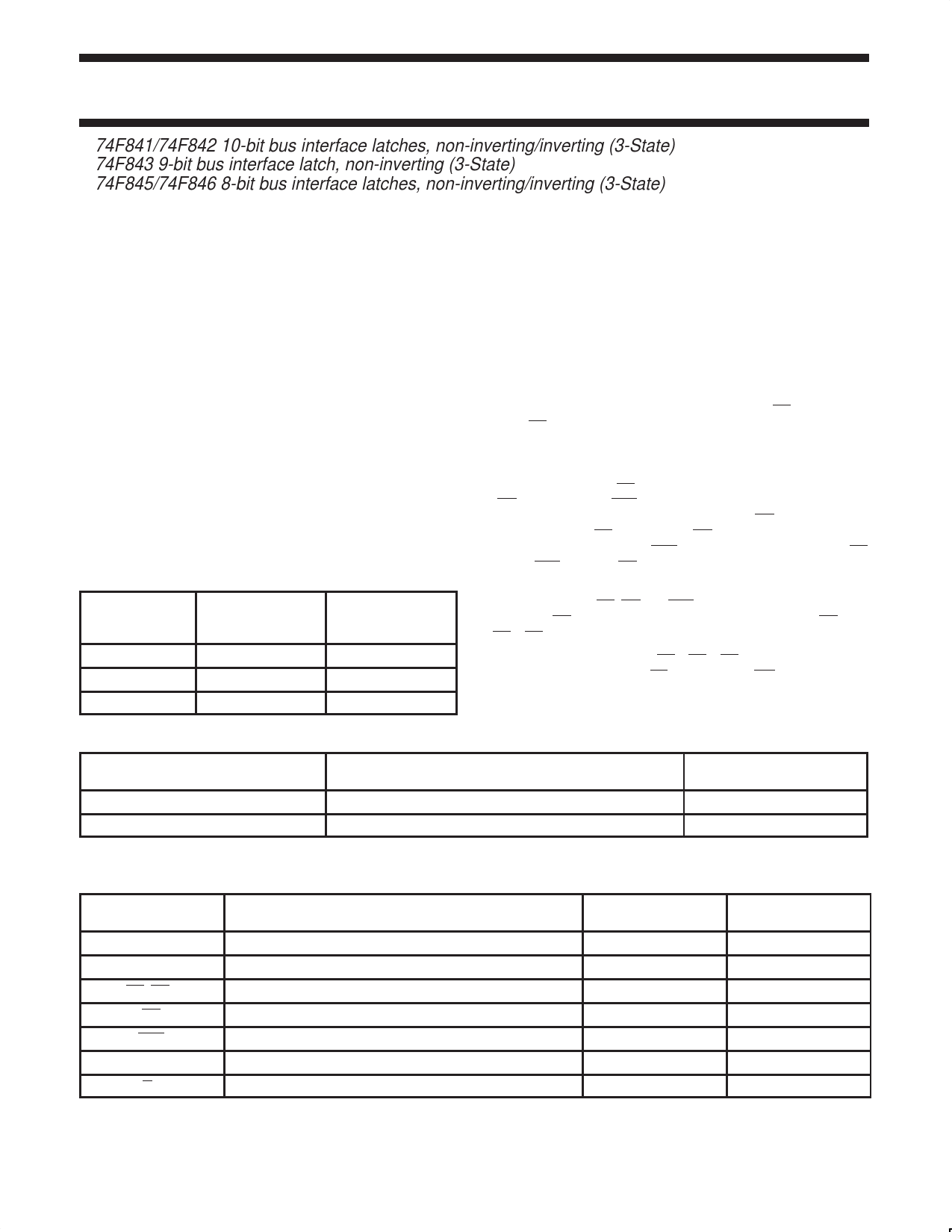

TYPE

74F841, 74F842

TYPICAL

PROPAGATION

DELAY

5.5 ns

TYPICAL

SUPPLY CURRENT

(TOTAL)

60 mA

ORDERING INFORMATION

COMMERCIAL RANGE: VCC = 5 V ± 10%; Tamb = 0 °C to +70 °C

Type number

Package

Name

Description

N74F841N, N74F842N

DIP24

plastic dual in-line package; 24 leads (300 mil)

N74F841D, N74F842D

SO24

plastic small outline package; 24 leads; body width 7.5 mm

Version

SOT222-1

SOT137-1

INPUT AND OUTPUT LOADING AND FAN-OUT TABLE

PINS

DESCRIPTION

74F(U.L.)

HIGH/LOW

Dn

Data inputs

1.0/0.033

LE

Latch Enable input

1.0/0.033

OE

Output Enable input (active-LOW)

1.0/0.033

Qn

Data outputs

1200/80

Qn

Data outputs

1200/80

NOTE: One (1.0) FAST Unit Load is defined as: 20 µA in the HIGH state and 0.6 mA in the LOW state.

LOAD VALUE

HIGH/LOW

20 µA / 20 µA

20 µA / 20 µA

20 µA / 20 µA

24 mA / 48 mA

24 mA / 48 mA

2004 Jan 23

2