XRT8001 查看數據表(PDF) - Exar Corporation

零件编号

产品描述 (功能)

生产厂家

XRT8001 Datasheet PDF : 48 Pages

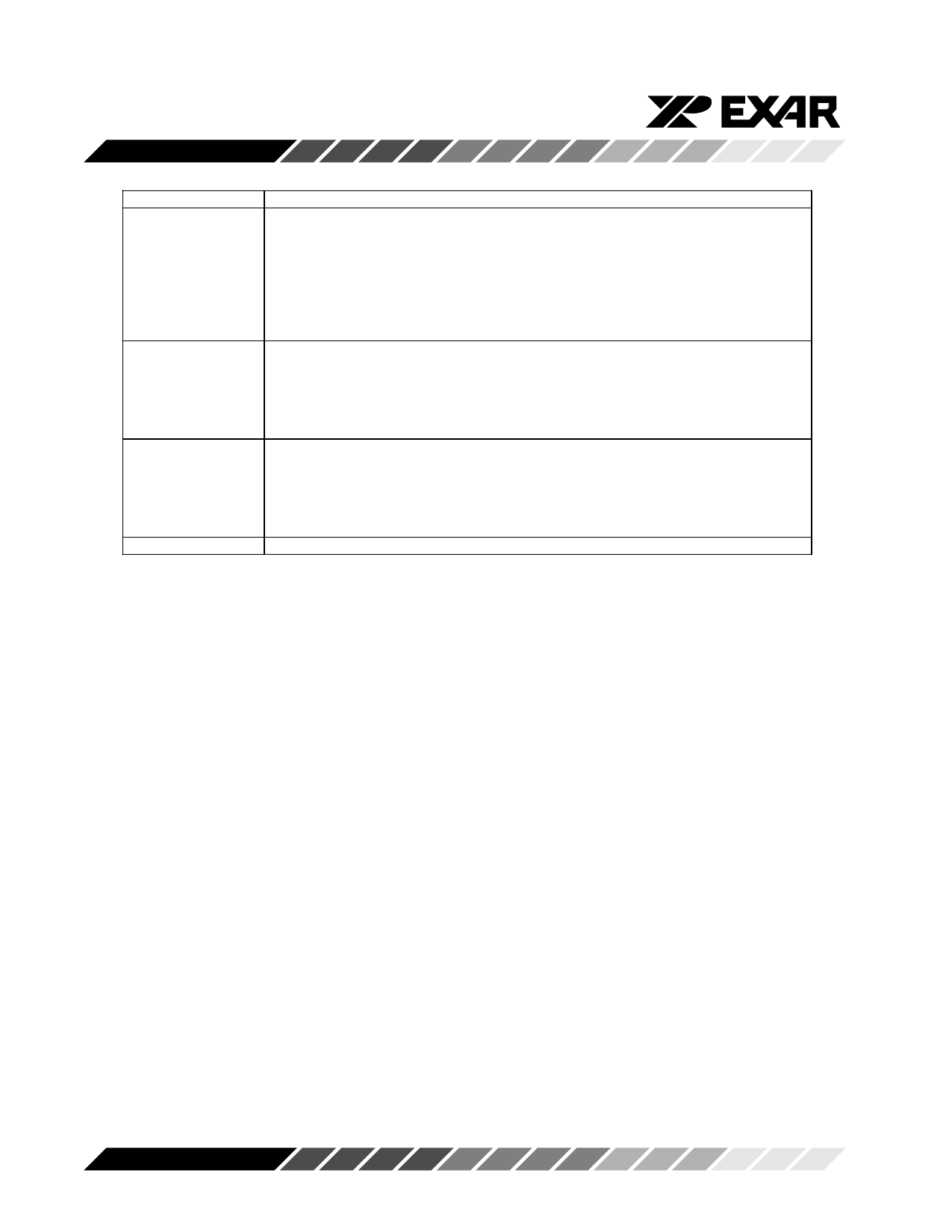

| |||

XRT8001

LDETDIS[2:1]

00

Signal output via the LOCKDET Signal

The LOCK Condition of PLL1 AND PLL2

With this selection, the LOCKDET output pin will be “high” if either one of the

following conditions are true.

a. If both PLL1 and PLL2 are in the “LOCK” condition, (applies if both PLL1 and

PLL2 are enabled) or

b. If the only enabled PLL is in the “LOCK” condition (applies only if one of the

PLLs are enabled).

01

The LOCK Condition of PLL2 Only

With this selection, only the “LOCK” state of PLL2 will be reflected in the LOCKDET

output pin.

LOCKDET = “high” if PLL2 is in “LOCK”.

LOCKDET = “low” if PLL2 is out of “LOCK”.

10

The LOCK Condition of PLL1 Only

With this selection, only the “LOCK” state of PLL1 will be reflected in the LOCKDET

output pin.

LOCKDET = “high” if PLL1 is in “LOCK”.

LOCKDET = “low” if PLL1 is out of “LOCK”.

11

LOCKDET will be unconditionally pulled to “LOW”

Table 3. Relationship Between the Values of the LDETDIS[2:1]

Bit-Fields and the Meaning of the LOCKDET Output Signal

4.0 Instructions for Configuring the XRT8001 WAN

Clock

As mentioned earlier, the XRT8001 WAN Clock can be

configured to operate in the following modes:

• The “Forward/Master” Mode

• The “Reverse/Master” Mode

• The “Fractional T1/E1 Reverse/Master” Mode

• The “E1 to T1 – Forward/Master” Mode

• The “High Speed – Reverse” Mode

• The “Forward/Slave” Mode

A detailed description of the operation and the configu-

ration steps for each of these configurations follows.

4.1 The “Forward/Master” Mode.

When the XRT8001 WAN Clock has been configured to

operate in the “Forward/Master” Mode, then it will

accept an “N x 1.544MHz” or an “N x 2.048MHz” clock

signal via the “Reference Clock” input at FIN (pin 3);

where “N” can range anywhere between 1 and 16. In

response to this clock signal, the XRT8001 WAN Clock

will output either a “K x 56kHz” or a “K x 64kHz” clock

signal, via the Clock Output pins (CLK1 and/or CLK2).

A simple illustration of the XRT8001 WAN Clock,

operating in the “Forward/Master” Mode is shown in

figure 13.

Rev. 1.01

20