Fairchild Semiconductor

V320MTC Даташит - Fairchild Semiconductor

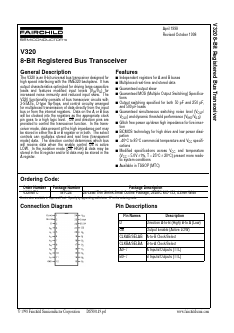

General Description

The V320 is an 8-bit universal bus transceiver designed for high speed interfacing with the VME320 backplane. It has output characteristics optimized for driving large capacitive loads and features modified input levels (VIH/VIL) for increased noise immunity and reduced input skew. The V320 functionality consists of bus transceiver circuits with 3-STATE, D-type flip-flops, and control circuitry arranged for multiplexed transmission of data directly from the input bus or from the internal registers. Data on the A or B bus will be clocked into the registers as the appropriate clock pin goes to a high logic level. OE and direction pins are provided to control the transceiver function. In the transceiver mode, data present at the high impedance port may be stored in either the A or B register or in both. The select controls can multiplex stored and real time (transparent mode) data. The direction control determines which bus will receive data when the enable control OE is active LOW. In the isolation mode (OE HIGH) A data may be stored in the B register and/or B data may be stored in the A register.

FEATUREs

■ Independent registers for A and B buses

■ Multiplexed real-time and stored data

■ Guaranteed output skew

■ Guaranteed MOS (Multiple Output Switching) Specifications

■ Output switching specified for both 50 pF and 250 pF,

and 500 pF loads

■ Guaranteed simultaneous switching noise level (VOLP/VOLV) and dynamic threshold performance (VIHD/VILD)

■ Glitch free power up/down high impedance for live insertion

■ BiCMOS technology for high drive and low power dissipation

■ −40°C to 85°C commercial temperature and VCC specifications

■ Modified specifications across VCC and temperature

(VCC = 5.0V ±1%, T = 25°C ± 20°C) present more realistic system conditions

■ Available in TSSOP (MTC)