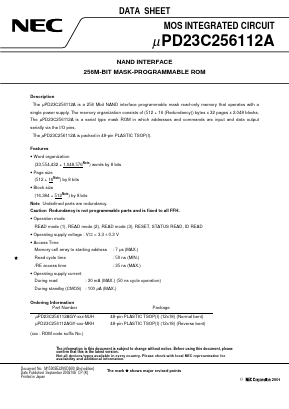

NEC => Renesas Technology

UPD23C256112A Даташит - NEC => Renesas Technology

Description

The µPD23C256112A is a 256 Mbit NAND interface programmable mask read-only memory that operates with a single power supply. The memory organization consists of (512 + 16 (Redundancy)) bytes x 32 pages x 2,048 blocks. The µPD23C256112A is a serial type mask ROM in which addresses and commands are input and data output serially via the I/O pins.

The µPD23C256112A is packed in 48-pin PLASTIC TSOP(I).

FEATUREs

• Word organization

(33,554,432 + 1,048,576Note) words by 8 bits

• Page size

(512 + 16Note) by 8 bits

• Block size

(16,384 + 512Note) by 8 bits

Note Underlined parts are redundancy.

Caution Redundancy is not programmable parts and is fixed to all FFH.

• Operation mode

READ mode (1), READ mode (2), READ mode (3), RESET, STATUS READ, ID READ

• Operating supply voltage : VCC = 3.3 ± 0.3 V

• Access Time

Memory cell array to starting address : 7 µs (MAX.)

Read cycle time : 50 ns (MIN.)

/RE access time : 35 ns (MAX.)

• Operating supply current

During read : 30 mA (MAX.) (50 ns cycle operation)

During standby (CMOS) : 100 µA (MAX.)