Micrel

SY89824LHCTR Даташит - Micrel

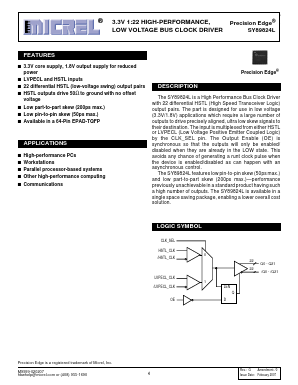

DESCRIPTION

The SY89824L is a High Performance Bus Clock Driver with 22 differential HSTL (High Speed Transceiver Logic) output pairs. The part is designed for use in low voltage (3.3V/1.8V) applications which require a large number of outputs to drive precisely aligned, ultra low skew signals to their destination. The input is multiplexed from either HSTL or LVPECL (Low Voltage Positive Emitter Coupled Logic) by the CLK_SEL pin. The Output Enable (OE) is synchronous so that the outputs will only be enabled/ disabled when they are already in the LOW state. This avoids any chance of generating a runt clock pulse when the device is enabled/disabled as can happen with an asynchronous control.

FEATURES

■ 3.3V core supply, 1.8V output supply for reduced power

■ LVPECL and HSTL inputs

■ 22 differential HSTL (low-voltage swing) output pairs

■ HSTL outputs drive 50Ω to ground with no offset voltage

■ Low part-to-part skew (200ps max.)

■ Low pin-to-pin skew (50ps max.)

■ Available in a 64-Pin EPAD-TQFP

APPLICATIONS

■ High-performance PCs

■ Workstations

■ Parallel processor-based systems

■ Other high-performance computing

■ Communications