Silicon Storage Technology

SST34HF1621C Даташит - Silicon Storage Technology

PRODUCT DESCRIPTION

The SST34HF16x1C ComboMemory devices integrate either a 1M x16 or 2M x8 CMOS flash memory bank with either a 128K x16 or 256K x16 CMOS SRAM memory bank in a multi-chip package (MCP). These devices are fabricated using SST’s proprietary, high-performance CMOS SuperFlash technology incorporating the split-gate cell design and thick-oxide tunneling injector to attain better reliability and manufacturability compared with alternate approaches. The SST34HF16x1C devices are ideal for applications such as cellular phones, GPS devices, PDAs, and other portable electronic devices in a low power and small form factor system.

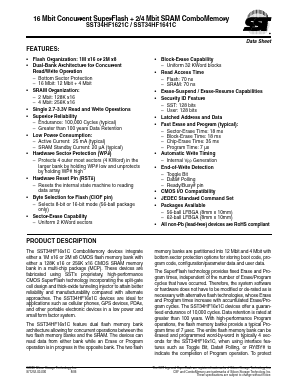

FEATURES:

• Flash Organization: 1M x16 or 2M x8

• Dual-Bank Architecture for Concurrent Read/Write Operation

– Bottom Sector Protection

– 16 Mbit: 12 Mbit + 4 Mbit

• SRAM Organization:

– 2 Mbit: 128K x16

– 4 Mbit: 256K x16

• Single 2.7-3.3V Read and Write Operations

• Superior Reliability

– Endurance: 100,000 Cycles (typical)

– Greater than 100 years Data Retention

• Low Power Consumption:

– Active Current: 25 mA (typical)

– SRAM Standby Current: 20 µA (typical)

• Hardware Sector Protection (WP#)

– Protects 4 outer most sectors (4 KWord) in the larger bank by holding WP# low and unprotects by holding WP# high

• Hardware Reset Pin (RST#)

– Resets the internal state machine to reading data array

• Byte Selection for Flash (CIOF pin)

– Selects 8-bit or 16-bit mode (56-ball package only)

• Sector-Erase Capability

– Uniform 2 KWord sectors

• Block-Erase Capability

– Uniform 32 KWord blocks

• Read Access Time

– Flash: 70 ns

– SRAM: 70 ns

• Erase-Suspend / Erase-Resume Capabilities

• Security ID Feature

– SST: 128 bits

– User: 128 bits

• Latched Address and Data

• Fast Erase and Program (typical):

– Sector-Erase Time: 18 ms

– Block-Erase Time: 18 ms

– Chip-Erase Time: 35 ms

– Program Time: 7 µs

• Automatic Write Timing

– Internal VPP Generation

• End-of-Write Detection

– Toggle Bit

– Data# Polling

– Ready/Busy# pin

• CMOS I/O Compatibility

• JEDEC Standard Command Set

• Packages Available

– 56-ball LFBGA (8mm x 10mm)

– 62-ball LFBGA (8mm x 10mm)

• All non-Pb (lead-free) devices are RoHS compliant