Infineon Technologies

Q67106-H5157 Даташит - Infineon Technologies

Functional Description

The CMOS circuit SDA 5649 is intended for use in video cassette recorders to retrieve control data of the PDC system from the data lines broadcast during the vertical blanking interval of a standard video signal.

FEATUREs

● Single-chip receiver for PDC data, broadcast either

– in Broadcast Data Service Packet (BDSP) 8/30/2 according to CCIR teletext system B, or

– in dedicated line no. 16 of the vertical blanking interval (VPS)

● Reception of Unified Date and Time (UDT), Network Identification code (NIC), and Short Program Label (SPL) broadcast in BDSP 8/30/1

● Reception of bytes no.38 through 45 of teletext header row containing clock time

● Low external components count

● On-chip data and sync slicer

● I2C-Bus interface for communication with external microcontroller

● Selection of PDC/VPS operating mode software controlled by I2C-Bus register

● Pin and software compatible to PDC/VPS Decoder SDA 5648

● Supply voltage: 5 V ± 10 %

● Video input signal level: 0.7 Vpp to 1.4 Vpp

● Technology: CMOS

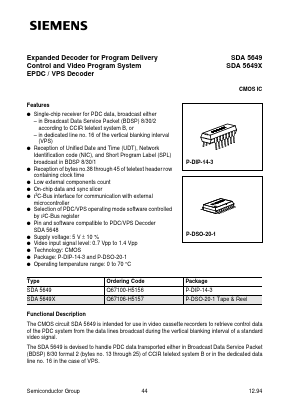

● Package: P-DIP-14-3 and P-DSO-20-1

● Operating temperature range: 0 to 70 °C