Japan Radio Corporation

NJU26157 Даташит - Japan Radio Corporation

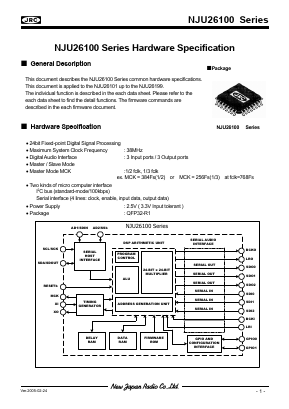

■ General Description

This document describes the NJU26100 Series common hardware specifications. This document is applied to the NJU26101 up to the NJU26199. The individual function is described in the each data sheet. Please refer to the each data sheet to find the detail functions. The firmware commands are described in the each firmware document.

■ Hardware Specification

•24bit Fixed-point Digital Signal Processing

•Maximum System Clock Frequency : 38MHz

•Digital Audio Interface : 3 Input ports / 3 Output ports

•Master / Slave Mode

•Master Mode MCK :1/2 fclk, 1/3 fclk

ex. MCK = 384Fs(1/2) or MCK = 256Fs(1/3) at fclk=768Fs

•Two kinds of micro computer interface

I2C bus (standard-mode/100kbps)

Serial interface (4 lines: clock, enable, input data, output data)

•Power Supply : 2.5V ( 3.3V Input tolerant )

•Package : QFP32-R1