Micron Technology

MT4LC4M16R6TG-6S Даташит - Micron Technology

GENERAL DESCRIPTION

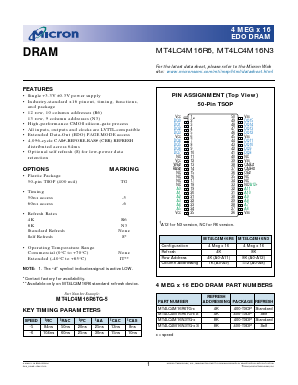

The 4 Meg x 16 DRAM is a high-speed CMOS, dynamic random-access memory device containing 67,108,864 bits and designed to operate from 3V to 3.6V. The device is functionally organized as 4,194,304 locations containing 16 bits each. The 4,194,304 memory locations are arranged in 4,096 rows by 1,024 columns on the MT4LC4M16R6 or 8,192 rows by 512 columns on the MT4LC4M16N3.

FEATURES

• Single +3.3V ±0.3V power supply

• Industry-standard x16 pinout, timing, functions, and package

• 12 row, 10 column addresses (R6) 13 row, 9 column addresses (N3)

• High-performance CMOS silicon-gate process

• All inputs, outputs and clocks are LVTTL-compatible

• Extended Data-Out (EDO) PAGE MODE access

• 4,096-cycle CAS#-BEFORE-RAS# (CBR) REFRESH distributed across 64ms

• Optional self refresh (S) for low-power data retention