ON Semiconductor

MC74HC175N Даташит - ON Semiconductor

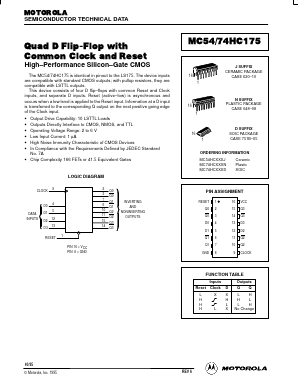

Quad D Flip-Flop With Common Clock & Reset High–Performance Silicon–Gate CMOS

The MC54/74HC175 is identical in pinout to the LS175. The device inputs are compatible with standard CMOS outputs; with pullup resistors, they are compatible with LSTTL outputs.

This device consists of four D flip–flops with common Reset and Clock inputs, and separate D inputs. Reset (active–low) is asynchronous and occurs when a low level is applied to the Reset input. Information at a D input is transferred to the corresponding Q output on the next positive going edge of the Clock input.

• Output Drive Capability: 10 LSTTL Loads

• Outputs Directly Interface to CMOS, NMOS, and TTL

• Operating Voltage Range: 2 to 6 V

• Low Input Current: 1 µA

• High Noise Immunity Characteristic of CMOS Devices

• In Compliance with the Requirements Defined by JEDEC Standard No. 7A

• Chip Complexity 166 FETs or 41.5 Equivalent Gates