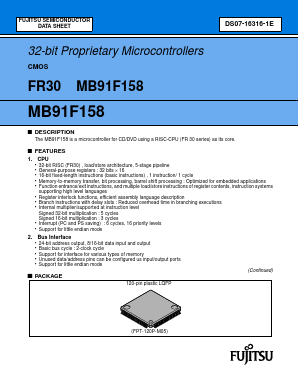

Fujitsu

MB91F158PFF-G Даташит - Fujitsu

■ DESCRIPTION

The MB91F158 is a microcontroller for CD/DVD using a RISC-CPU (FR 30 series) as its core.

■ FEATURES

1. CPU

• 32-bit RISC (FR30) , load/store architecture, 5-stage pipeline

• General-purpose registers : 32 bits × 16

• 16-bit fixed-length instructions (basic instructions) , 1 instruction/ 1 cycle

• Memory-to-memory transfer, bit processing, barrel shift processing : Optimized for embedded applications

• Function entrance/exit instructions, and multiple load/store instructions of register contents, instruction systems supporting high level languages

• Register interlock functions, efficient assembly language description

• Branch instructions with delay slots : Reduced overhead time in branching executions

• Internal multiplier/supported at instruction level

Signed 32-bit multiplication : 5 cycles

Signed 16-bit multiplication : 3 cycles

• Interrupt (PC and PS saving) : 6 cycles, 16 priority levels

• Support for little endian mode

2. Bus Interface

• 24-bit address output, 8/16-bit data input and output

• Basic bus cycle : 2-clock cycle

• Support for interface for various types of memory

• Unused data/address pins can be configured us input/output ports

• Support for little endian mode

3. Internal ROM

FLASH products : 510 Kbytes

4. Internal RAM

2 Kbytes

5. Internal Data RAM

6 Kbytes

6. Bit Search Module

Searches in one cycle for the position of the bit that changes from the MSB in one word to the initial I/O.

7. Timers

• 16-bit OCU × 4 channels, ICU × 4 channels, Free-run timer × 1 channel

• 8/16-bit up/down timer/counter (8-bit × 2 channels or 16-bit × 1 channel)

• 16-bit PPG timer × 4 channels. The output pulse cycle and duty can be varied as desired

• 16-bit reload timer × 2 channels

8. D/A Converter

• 8-bit × 3 channels

9. A/D Converter (Sequential Comparison Type)

• 10-bit × 8 channels

• Sequential conversion method (conversion time : 5.2 µs@32 MHz)

• Single conversion or scan conversion can be selected, and one-shot or continuous or stop conversion mode can be set respectively.

• Conversion starting function by hardware/software.

10. Serial I/O

• UART × 2 channels. Any of them is capable of serial transfer in sync with clock attached with the LSB/MSB switching function.

• Serial data output and serial clock output are selectable by push-pull/open drain software.

• A 16-bit timer (U-timer) is contained as a dedicated baud rate generator allowing any baud rate to be generated.

11. Clock Switching Function

• Gear function : Operating clock ratios to the basic clock can be set independently for the CPU and peripherals from four types, 1 : 1, 1 : 2, 1 : 4 or 1 : 8.

12. Interrupt Controller

External interrupt input (16 channels in total) :

• Allows the rising edge/falling edge/H level/L level to be set.

Internal interrupt factors :

• Interrupt by resources and delay interrupt

13. Others

• Reset cause : Power on reset/watchdog timer/software reset/external reset

• Low power consumption mode : Sleep/stop

• Package : 120-pin LQFP

• CMOS technology (0.35 µm)

• Power supply voltage : 3.2 V to 3.5 V

• Operation frequency upper limit

CPU : 32 MHz

Peripheral circuit : 32 MHz

External bus : 25 MHz