Fujitsu

MB91266PMC-G-XXXE1 Даташит - Fujitsu

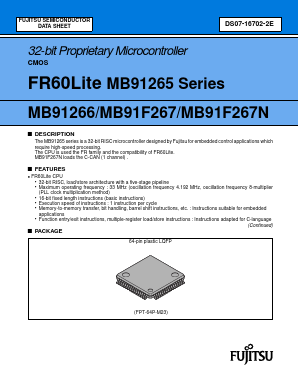

■ DESCRIPTION

The MB91265 series is a 32-bit RISC microcontroller designed by Fujitsu for embedded control applications which require high-speed processing.

The CPU is used the FR family and the compatibility of FR60Lite.

MB91F267N loads the C-CAN (1 channel) .

■ FEATURES

• FR60Lite CPU

• 32-bit RISC, load/store architecture with a five-stage pipeline

• Maximum operating frequency : 33 MHz (oscillation frequency 4.192 MHz, oscillation frequency 8-multiplier (PLL clock multiplication method)

• 16-bit fixed length instructions (basic instructions)

• Execution speed of instructions : 1 instruction per cycle

• Memory-to-memory transfer, bit handling, barrel shift instructions, etc. : Instructions suitable for embedded applications

• Function entry/exit instructions, multiple-register load/store instructions : Instructions adapted for C-language

• Register interlock function : Facilitates coding in assembler.

• Built-in multiplier with instruction-level support

• 32-bit multiplication with sign : 5 cycles

• 16-bit multiplication with sign : 3 cycles

• Interrupt (PC, PS save) : 6 cycles, 16 priority levels

• Harvard architecture allowing program access and data access to be executed simultaneously

• Instruction compatible with FR family

• Internal peripheral functions

• Capacity of internal ROM and ROM type

MASK ROM : 64 Kbytes (MB91266)

FLASH ROM : 128 Kbytes (MB91F267/MB91F267N)

• Capacity of internal RAM : 2 Kbytes (MASK product)/4 Kbytes (FLASH memory product)

• A/D converter (sequential comparison type)

Resolution : 8/10 bits : 4 channels × 1 unit, 7 channels × 1 unit

Conversion time : 1.2 µs (Minimum conversion time system clock at 33 MHz)

1.35 µs (Minimum conversion time system clock at 20 MHz)

• External interrupt input : 8 channels

• Bit search module (for REALOS)

Function for searching the MSB (upper bit) in each word for the first 1-to-0 inverted bit position

• C-CAN 32MSB : 1 channel (loaded in MB91F267N only)

• UART (Full-duplex double buffer) : 2 channels Selectable parity On/Off

Asynchronous (start-stop synchronized) or clock-synchronous communications selectable

Internal timer for dedicated baud rate (U-TIMER) on each channel

External clock can be used as transfer clock

Error detection function for parity, frame, and overrun errors

• 8/16-bit PPG timer : 8 channels (at 8-bit) / 4 channels (at 16-bit)

• Timing generator

• 16-bit reload timer : 3 channels (with cascade mode, without output of reload timer 0)

• 16-bit free-run timer : 3 channels

• 16-bit PWC timer : 1 channel

• Input capture : 4 channels (interface with free-run timer)

• Output compare : 6 channels (interface with free-run timer)

• Waveform generator

Various waveforms which are generated by using output compare, 16-bit PPG timer 0, and 16-bit dead timer

• SUM of products macro

RAM : instruction RAM (I-RAM) 256 × 16-bit

coefficient RAM (X-RAM) 64 × 16-bit

variable RAM (Y-RAM) 64 × 16-bit

Execution of 1 cycle MAC (16-bit × 16-bit + 40 bits)

Operation results are extracted rounded from 40 to 16 bits

• DMAC (DMA Controller) : 5 channels

Operation of transfer and activation by internal peripheral interrupts and software

• Watchdog timer

• Low-power consumption mode

Sleep/stop function

• Package : LQFP-64P

• Technology : CMOS 0.35 µm

• Power supply : 1-power supply (Vcc = 4.0 V to 5.5 V)