Motorola => Freescale

DSP56307UM/D Даташит - Motorola => Freescale

24-BIT DIGITAL SIGNAL PROCESSOR

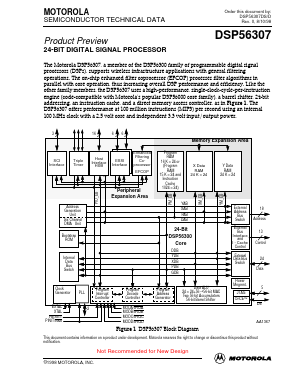

The Motorola DSP56307, a member of the DSP56300 family of programmable digital signal processors (DSPs), supports wireless infrastructure applications with general filtering operations. The on-chip enhanced filter coprocessor (EFCOP) processes filter algorithms in parallel with core operation, thus increasing overall DSP performance and efficiency. Like the other family members, the DSP56307 uses a high-performance, single-clock-cycle-per-instruction engine (code-compatible with Motorolas popular DSP56000 core family), a barrel shifter, 24-bit addressing, an instruction cache, and a direct memory access controller, as in Figure 1. The DSP56307 offers performance at 100 million instructions (MIPS) per second using an internal 100 MHz clock with a 2.5 volt core and independent 3.3 volt input/output power.

FEATURES

High-Performance DSP56300 Core

● 100 million instructions per second (MIPS) with a 100 MHz clock at 2.5 V core and 3.3 V I/O

● Object code compatible with the DSP56000 core

● Highly parallel instruction set

● Data arithmetic logic unit (ALU)

- Fully pipelined 24 x 24-bit parallel multiplier-accumulator

- 56-bit parallel barrel shifter (fast shift and normalization; bit stream generation and parsing)

- Conditional ALU instructions

- 24-bit or 16-bit arithmetic support under software control

● Program control unit (PCU)

- Position independent code (PIC) support

- Addressing modes optimized for DSP applications (including immediate offsets)

- On-chip instruction cache controller

- On-chip memory-expandable hardware stack

- Nested hardware DO loops

- Fast auto-return interrupts

● Direct memory access (DMA)

- Six DMA channels supporting internal and external accesses

- One-, two-, and three- dimensional transfers (including circular buffering)

- End-of-block-transfer interrupts

- Triggering from interrupt lines and all peripherals

● Phase-locked loop (PLL)

- Allows change of low power divide factor (DF) without loss of lock

- Output clock with skew elimination

● Hardware debugging support

- On-Chip Emulation (OnCE) module

- Joint test action group (JTAG) test access port (TAP)

- Address trace mode reflects internal Program RAM accesses at the external port