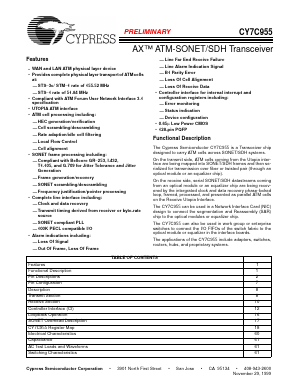

Cypress Semiconductor

CY7C955 Даташит - Cypress Semiconductor

Functional Description

The Cypress Semiconductor CY7C955 is a Transceiver chip designed to carry ATM cells across SONET/SDH systems.

FEATUREs

• WAN and LAN ATM physical layer device

• Provides complete physical layer transport of ATM cells at:

— STS−3c/ STM−1 rate of 155.52 MHz

— STS−1 rate of 51.84 MHz

• Compliant with ATM Forum User Network Interface 3.1 specification

• UTOPIA ATM interface

• ATM cell processing including:

— HEC generation/verification

— Cell scrambling/descrambling

— Rate adaption/idle cell filtering

— Local Flow Control

— Cell alignment

• SONET frame processing including:

— Compliant with Bellcore GR−253, I.432, T1.105, and G.709 for Jitter Tolerance and Jitter Generation

— Frame generation/recovery

— SONET scrambling/descrambling

— Frequency justification/pointer processing

• Complete line interface including:

— Clock and data recovery

— Transmit timing derived from receiver or byte-rate source

— SONET compliant PLL

— 100K PECL compatible I/O

• Alarm indications including:

— Loss Of Signal

— Out Of Frame, Loss Of Frame

— Line Far End Receive Failure

— Line Alarm Indication Signal

— B1 Parity Error

— Loss Of Cell Alignment

— Loss Of Receive Data

• Controller interface for internal interrupt and configuration registers including:

— Error monitoring

— Status indication

— Device configuration

• 0.65µ Low Power CMOS

• 128-pin PQFP