STMicroelectronics

CB45000 Даташит - STMicroelectronics

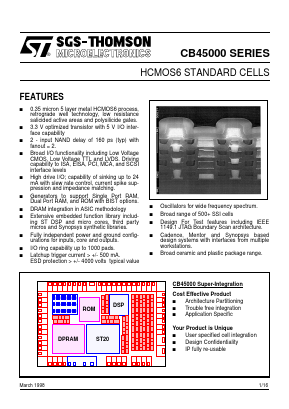

GENERAL DESCRIPTION

The CB45000 standard cell series uses a high performance, low voltage, 5 level metal, HCMOS6 0.35 micron process to achieve subnanosecond internal speeds while offering very low power dissipation and high noise immunity.

FEATURES

■ 0.35 micron 5 layer metal HCMOS6 process, retrograde well technology, low resistance salicided active areas and polysilicide gates.

■ 3.3 V optimized transistor with 5 V I/O interface capability

■ 2 - input NAND delay of 160 ps (typ) with fanout = 2.

■ Broad I/O functionality including Low Voltage CMOS, Low Voltage TTL and LVDS. Driving capability to ISA, EISA, PCI, MCA, and SCSI interface levels

■ High drive I/O; capability of sinking up to 24 mA with slew rate control, current spike suppression and impedance matching.

■ Generators to support Single Port RAM, Dual Port RAM, and ROM with BIST options.

■ DRAM integration in ASIC methodology

■ Extensive embedded function library including ST DSP and micro cores, third party micros and Synopsys synthetic libraries.

■ Fully independent power and ground configurations for inputs, core and outputs.

■ I/O ring capability up to 1000 pads.

■ Latchup trigger current > +/- 500 mA. ESD protection > +/- 4000 volts typical value

■ Oscillators for wide frequency spectrum.

■ Broad range of 500+ SSI cells

■ Design For Test features including IEEE 1149.1 JTAG Boundary Scan architecture.

■ Cadence, Mentor and Synopsys based design systems with interfaces from multiple workstations.

■ Broad ceramic and plastic package range.