Silicon Laboratories

C8051F006 Даташит - Silicon Laboratories

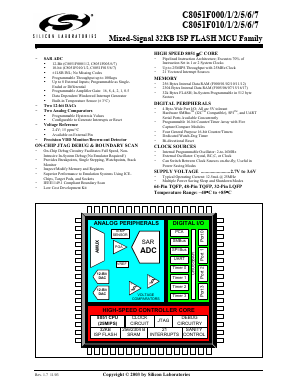

SYSTEM OVERVIEW

The C8051F000 family are fully integrated mixed-signal System on a Chip MCUs with a true 12-bit multi-channel ADC (F000/01/02/05/06/07), or a true 10-bit multi-channel ADC (F010/11/12/15/16/17). See the Product Selection Guide in Table 1.1 for a quick reference of each MCUs’ feature set. Each has a programmable gain pre-amplifier, two 12-bit DACs, two voltage comparators (except for the F002/07/12/17, which have one), a voltage reference, and an 8051-compatible microcontroller core with 32kbytes of FLASH memory. There are also I2C/SMBus, UART, and SPI serial interfaces implemented in hardware (not “bit-banged” in user software) as well as a Programmable Counter/Timer Array (PCA) with five capture/compare modules. There are also 4 general-purpose 16-bit timers and 4 byte-wide general-purpose digital Port I/O. The C8051F000/01/02/10/11/12 have 256 bytes of RAM and execute up to 20MIPS, while the C8051F005/06/07/15/16/17 have 2304 bytes of RAM and execute up to 25MIPS.

ANALOG PERIPHERALS

- SAR ADC

◾ 12-Bit (C8051F000/1/2, C8051F005/6/7)

◾ 10-bit (C8051F010/1/2, C8051F015/6/7)

◾ ±1LSB INL; No Missing Codes

◾ Programmable Throughput up to 100ksps

◾ Up to 8 External Inputs; Programmable as SingleEnded or Differential

◾ Programmable Amplifier Gain: 16, 8, 4, 2, 1, 0.5

◾ Data Dependent Windowed Interrupt Generator

◾ Built-in Temperature Sensor (± 3°C)

- Two 12-bit DACs

- Two Analog Comparators

◾ Programmable Hysteresis Values

◾ Configurable to Generate Interrupts or Reset

- Voltage Reference

◾ 2.4V; 15 ppm/°C

◾ Available on External Pin

- Precision VDD Monitor/Brown-out Detector

ON-CHIP JTAG DEBUG & BOUNDARY SCAN

- On-Chip Debug Circuitry Facilitates Full Speed, NonIntrusive In-System Debug (No Emulator Required!)

- Provides Breakpoints, Single Stepping, Watchpoints, Stack Monitor

- Inspect/Modify Memory and Registers

- Superior Performance to Emulation Systems Using ICEChips, Target Pods, and Sockets

- IEEE1149.1 Compliant Boundary Scan

- Low Cost Development Kit

HIGH SPEED 8051 μC CORE

- Pipelined Instruction Architecture; Executes 70% of Instruction Set in 1 or 2 System Clocks

- Up to 25MIPS Throughput with 25MHz Clock

- 21 Vectored Interrupt Sources

MEMORY

- 256 Bytes Internal Data RAM (F000/01/02/10/11/12)

- 2304 Bytes Internal Data RAM (F005/06/07/15/16/17)

- 32k Bytes FLASH; In-System Programmable in 512 byte Sectors

DIGITAL PERIPHERALS

- 4 Byte-Wide Port I/O; All are 5V tolerant

- Hardware SMBusTM (I2CTM Compatible), SPITM, and UART Serial Ports Available Concurrently

- Programmable 16-bit Counter/Timer Array with Five Capture/Compare Modules

- Four General Purpose 16-bit Counter/Timers

- Dedicated Watch-Dog Timer

- Bi-directional Reset

CLOCK SOURCES

- Internal Programmable Oscillator: 2-to-16MHz

- External Oscillator: Crystal, RC,C, or Clock

- Can Switch Between Clock Sources on-the-fly; Useful in Power Saving Modes

SUPPLY VOLTAGE ........................ 2.7V to 3.6V

- Typical Operating Current: 12.5mA @ 25MHz

- Multiple Power Saving Sleep and Shutdown Modes

64-Pin TQFP, 48-Pin TQFP, 32-Pin LQFP

Temperature Range: –40°C to +85°C