Integrated Circuit Systems

AV9172 Даташит - Integrated Circuit Systems

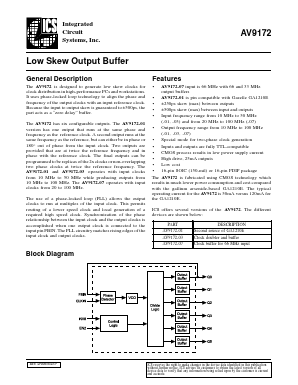

General Description

The AV9172 is designed to generate low skew clocks for clock distribution in high-performance PCs and workstations. It uses phase-locked loop technology to align the phase and frequency of the output clocks with an input reference clock. Because the input to output skew is guaranteed to ±500ps, the part acts as a “zero delay” buffer.

FEATUREs

• AV9172-07 input is 66 MHz with 66 and 33 MHz output buffers

• AV9172-01 is pin compatible with Gazelle GA1210E

• ±250ps skew (max) between outputs

• ±500ps skew (max) between input and outputs

• Input frequency range from 10 MHz to 50 MHz (-01, -03) and from 20 MHz to 100 MHz (-07)

• Output frequency range from 10 MHz to 100 MHz (-01, -03, -07)

• Special mode for two-phase clock generation

• Inputs and outputs are fully TTL-compatible

• CMOS process results in low power supply current

• High drive, 25mA outputs

• Low cost

• 16-pin SOIC (150-mil) or 16-pin PDIP package