Analog Devices

ADSP-21161NYCAZ110 Даташит - Analog Devices

GENERAL DESCRIPTION

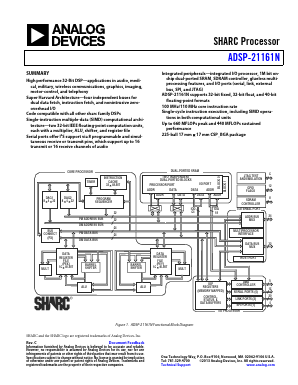

The ADSP-21161N SHARC® DSP is a low cost derivative of the ADSP-21160 featuring Analog Devices Super Harvard Architecture. Easing portability, the ADSP-21161N is source code compatible with the ADSP-21160 and with first generation ADSP-2106x SHARC processors in SISD (Single-Instruction, Single-Data) mode. Like other SHARC DSPs, the ADSP- 21161N is a 32-bit processor that is optimized for high performance DSP applications. The ADSP-21161N includes a 100 MHz or 110 MHz core, a dual-ported on-chip SRAM, an integrated I/O processor with multiprocessing support, and multiple internal buses to eliminate I/O bottlenecks.

SUMMARY

High performance 32-Bit DSP—applications in audio, medical,

military, wireless communications, graphics, imaging,

motor-control, and telephony

Super Harvard Architecture—four independent buses for

dual data fetch, instruction fetch, and nonintrusive zero-overhead I/O

Code compatible with all other sharc family DSPs

Single-instruction multiple-data (SIMD) computational

architecture—two 32-bit IEEE floating-point computation units,

each with a multiplier, ALU, shifter, and register file

Serial ports offer I2S support via 8 programmable and

simultaneous receive or transmit pins, which support up to 16

transmit or 16 receive channels of audio

Integrated peripherals—integrated I/O processor, 1M bit

on-chip dual-ported SRAM, SDRAM controller, glueless

multiprocessing features, and I/O ports (serial, link, external

bus, SPI, and JTAG)

ADSP-21161N supports 32-bit fixed, 32-bit float, and 40-bit

floating-point formats

100 MHz/110 MHz core instruction rate

Single-cycle instruction execution, including SIMD

operations in both computational units

Up to 660 MFLOPs peak and 440 MFLOPs sustained

performance

225-ball 17 mm x 17 mm CSP_BGA package