Analog Devices

AD9551BCPZ-REEL7 Даташит - Analog Devices

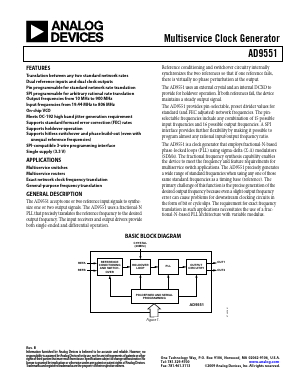

GENERAL DESCRIPTION

The AD9551 accepts one or two reference input signals to synthesize one or two output signals. The AD9551 uses a fractional-N PLL that precisely translates the reference frequency to the desired output frequency. The input receivers and output drivers provide both single-ended and differential operation.

FEATURES

Translation between any two standard network rates

Dual reference inputs and dual clock outputs

Pin programmable for standard network rate translation

SPI programmable for arbitrary rational rate translation

Output frequencies from 10 MHz to 900 MHz

Input frequencies from 19.44 MHz to 806 MHz

On-chip VCO

Meets OC-192 high band jitter generation requirement

Supports standard forward error correction (FEC) rates

Supports holdover operation

Supports hitless switchover and phase build-out (even with

unequal reference frequencies)

SPI-compatible 3-wire programming interface

Single supply (3.3 V)

APPLICATIONS

Multiservice switches

Multiservice routers

Exact network clock frequency translation

General-purpose frequency translation