Intel

80C251TP Даташит - Intel

INTRODUCTION

A member of the Intel family of 8-bit MCS 251 microcontrollers, the 8xC251TA/TB/TP/TQ is binary-code compatible with MCS 51 microcontrollers and pin compatible with 40-pin PDIP and 44-pin PLCC MCS 51 microcontrollers.

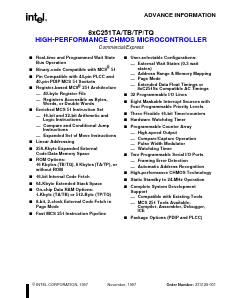

■ Real-time and Programmed Wait State Bus Operation

■ Binary-code Compatible with MCS® 51

■ Pin Compatible with 44-pin PLCC and 40-pin PDIP MCS 51 Sockets

■ Register-based MCS® 251 Architecture

— 40-byte Register File

— Registers Accessible as Bytes, Words, or Double Words

■ Enriched MCS 51 Instruction Set

— 16-bit and 32-bit Arithmetic and Logic Instructions

— Compare and Conditional Jump Instructions

— Expanded Set of Move Instructions

■ Linear Addressing

■ 256-Kbyte Expanded External Code/Data Memory Space

■ ROM Options: 16 Kbytes (TB/TQ), 8 Kbytes (TA/TP), or without ROM

■ 16-bit Internal Code Fetch

■ 64-Kbyte Extended Stack Space

■ On-chip Data RAM Options: 1-Kbyte (TA/TB) or 512-Byte (TP/TQ)

■ 8-bit, 2-clock External Code Fetch in Page Mode

■ Fast MCS 251 Instruction Pipeline

■ User-selectable Configurations:

— External Wait States (0-3 wait states)

— Address Range & Memory Mapping

— Page Mode

— Extended Data Float Timings or 8xC251Sx Compatible AC Timings

■ 32 Programmable I/O Lines

■ Eight Maskable Interrupt Sources with Four Programmable Priority Levels

■ Three Flexible 16-bit Timer/counters

■ Hardware Watchdog Timer

■ Programmable Counter Array

— High-speed Output

— Compare/Capture Operation

— Pulse Width Modulator

— Watchdog Timer

■ Two Programmable Serial I/O Ports

— Framing Error Detection

— Automatic Address Recognition

■ High-performance CHMOS Technology

■ Static Standby to 24-MHz Operation

■ Complete System Development Support

— Compatible with Existing Tools

— MCS 251 Tools Available: Compiler, Assembler, Debugger, ICE

■ Package Options (PDIP and PLCC)