CXD3511 Просмотр технического описания (PDF) - Sony Semiconductor

Номер в каталоге

Компоненты Описание

производитель

CXD3511 Datasheet PDF : 79 Pages

| |||

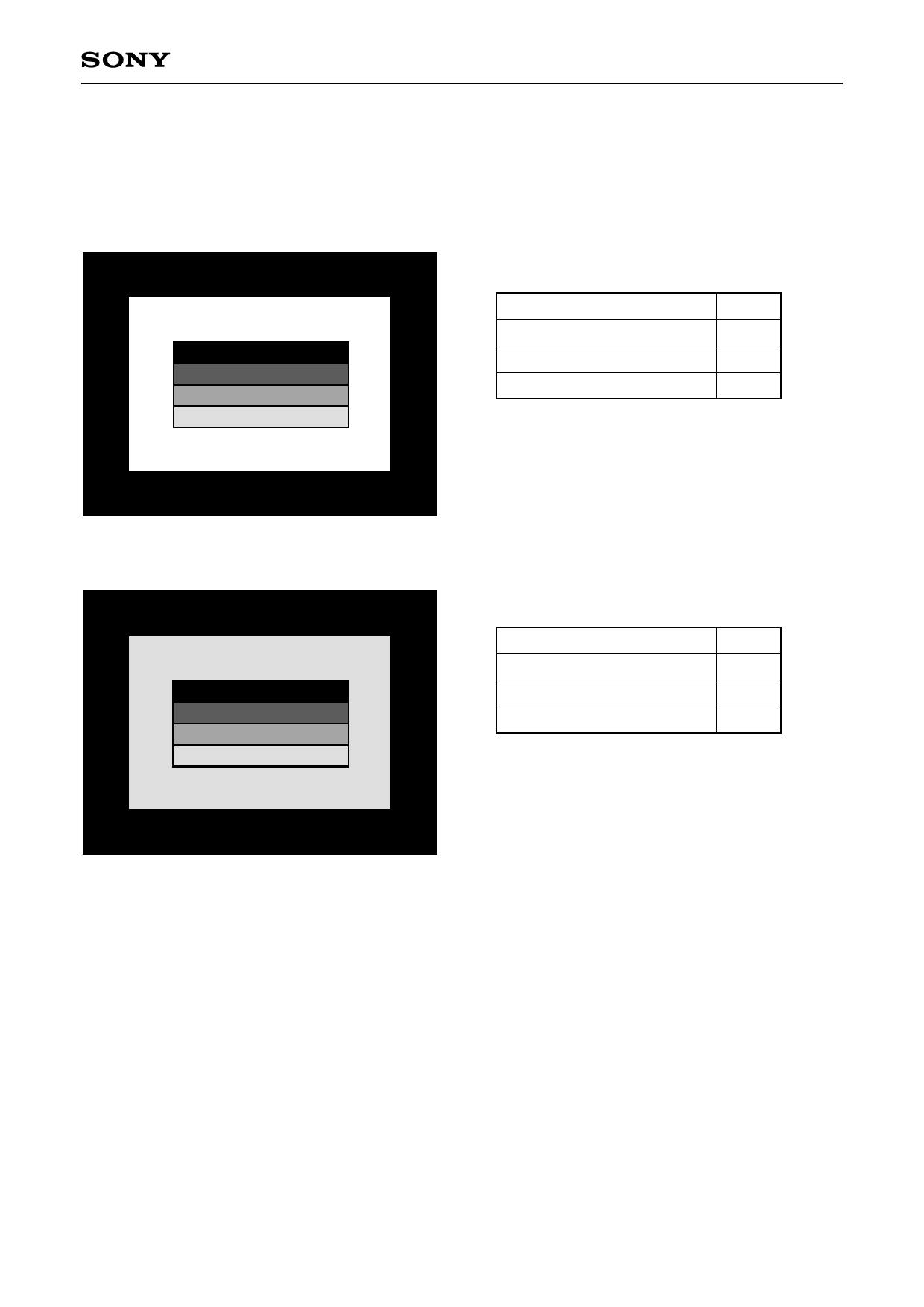

(11) Vertical stair

When PG_PAT[2:0] = 7h and PG_STAIR_SW = 1, a vertical stair is displayed.

The signal level is incremented from 000h by 64 bits for each 32 lines.

CXD3511Q

PG_SIG2R (G, B)

PG_R (G, B)_SEL

0

PG_PAT[2:0]

7h

PG_STRP_SW

x

PG_STAIR_SW

1

PG_SIG1R (G, B)

PG_R (G, B)_SEL

1

PG_PAT[2:0]

7h

PG_STRP_SW

x

PG_STAIR_SW

1

x: Don't care

– 31 –