BM29F400B Просмотр технического описания (PDF) - Unspecified

Номер в каталоге

Компоненты Описание

производитель

BM29F400B Datasheet PDF : 38 Pages

| |||

BRIGHT

Microelectronics

Inc.

Preliminary BM29F400T/BM29F400B

machine is operating will be erroneous. Thus, these address locations will need rewriting after the

device is reset.

FEATURES

• 5.0 V +/- 10% Program and Erase

− Minimizes system-level power requirements

High performance

− 90 nS access time

• Compatible with JEDEC-standard Commands

− Uses software commands, pinouts, and

packages following industry standards for

single power supply Flash memory

• Typically 100,000 Program/Erase Cycles

• Sector Erase Architecture

− One 16 Kbytes, two 8 Kbytes, one 32 Kbytes,

and seven 64 Kbytes

− Any combination of sectors can be erased

concurrently; also supports full chip erase

• Erase Suspend/Resume

− Suspend a sector erase operation to allow a

data read in a sector not being erased within

the same device

• Ready/Busy

− RY/BY output pin for detection of

programming or erase cycle completion

• RESET

− Hardware pin resets the internal state

machine to the read mode

• Internal Erase Algorithms

− Automatically erases a sector, any

combination of sectors, or the entire

chip

• Internal Programming Algorithms

− Automatically programs and verifies data at a

specified address

• Low Power Consumption

− 20 mA typical active read current for Byte

Mode

− 28 mA typical active read current for Word

Mode

− 30 mA typical write/erase current

• Sector Protection

− Hardware method disables any combination

of sectors from a program or erase operation

• Boot Code Sector Architecture

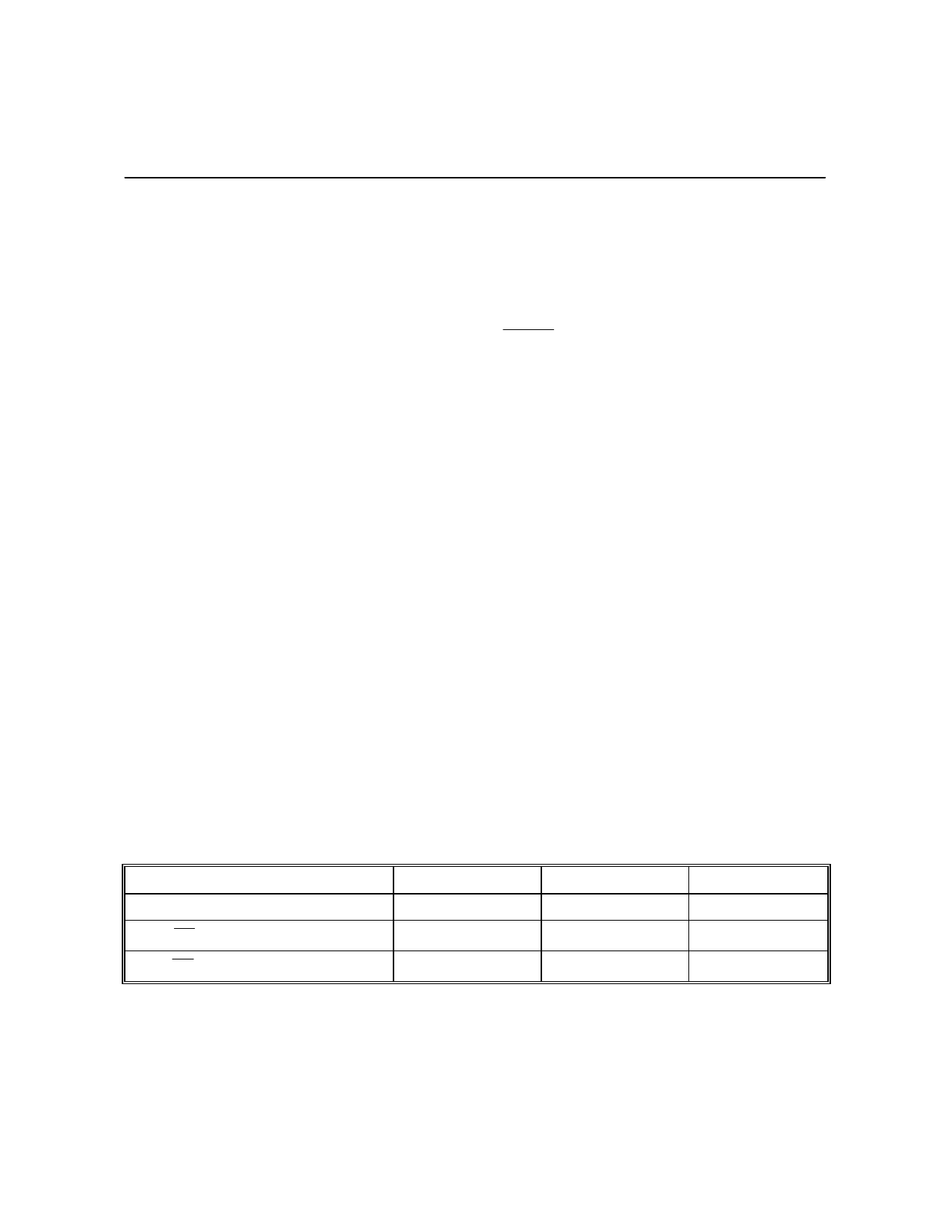

FAMILY PART NO.

-90

-120

Maximum Access Time (nS)

90

120

CE (E) Access time (nS)

90

120

OE (G) Access time (nS)

35

50

*This speed is available with Vcc = 5V +/- 5% variation

-150

150

150

60

-2-