AD9500TE Просмотр технического описания (PDF) - Analog Devices

Номер в каталоге

Компоненты Описание

производитель

AD9500TE Datasheet PDF : 11 Pages

| |||

AD9500

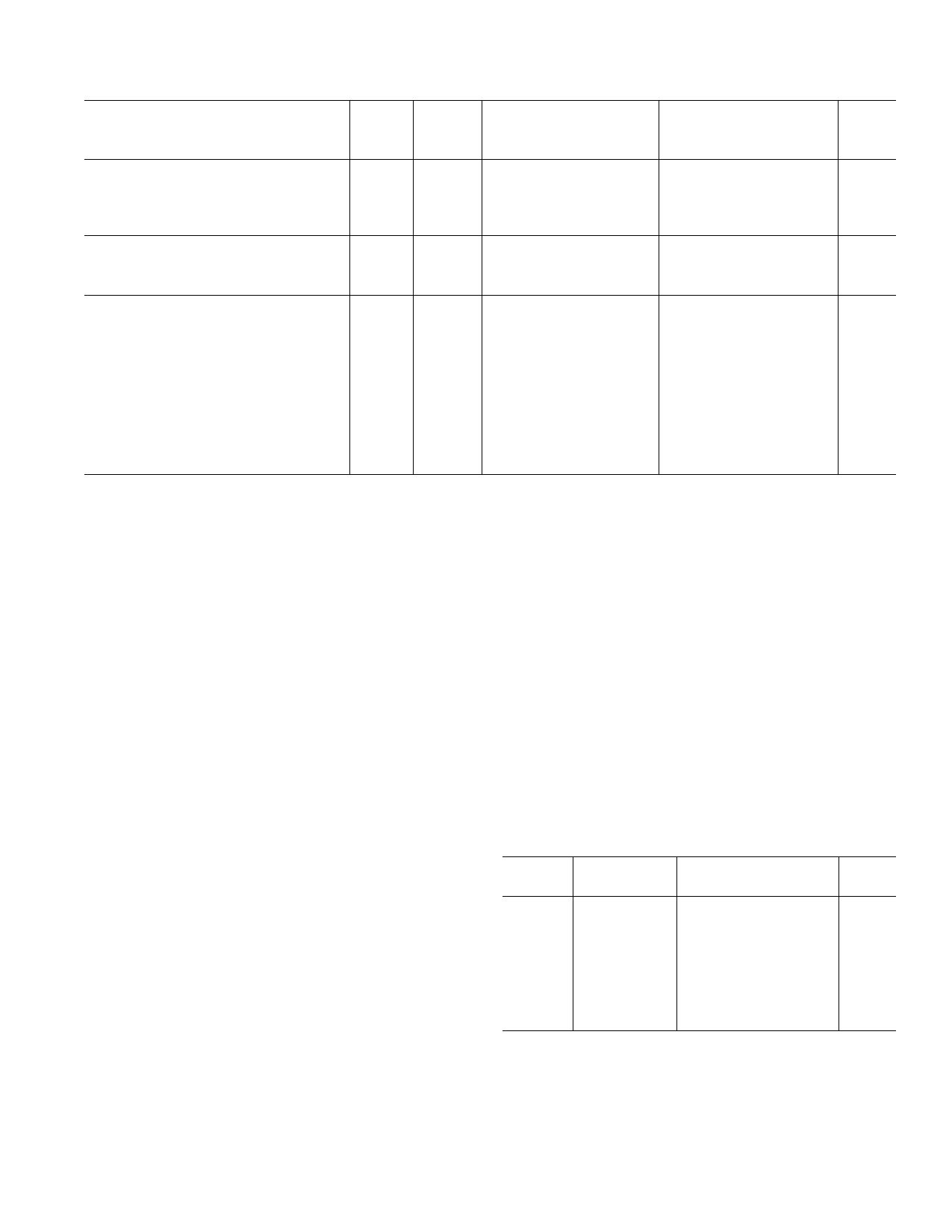

Parameter

Test

Level Temp

–25؇C to +85؇C

AD9500BP/BQ

Min Typ

Max

–55؇C to +125؇C

AD9500TE/TQ

Min Typ

Max

Units

SUPPORT FUNCTIONS

ECLREF

ECLREF Voltage Drift14

Offset Adjust Range

IV

+25°C –1.4 –1.3

–1.2 –1.4 –1.3

–1.2 V

V

Full

1.1

1.1

mV/°C

V

Full

–2

–2

mA

DIGITAL OUTPUTS7

Logic “1” Voltage

Logic “0” Voltage

VI

Full

–1.1

VI

Full

–1.1

–1.5

V

–1.5 V

POWER SUPPLY15

Positive Supply Current (+5.0 V)

Negative Supply Current (–5.2 V)

Nominal Power Dissipation

Power Supply Rejection Ratio16

Full-Scale Range Sensitivity

Minimum Propagation Delay

Sensitivity

I

+25°C

VI

Full

I

+25°C

VI

Full

V

+25°C

I

+25°C

I

+25°C

24

28

30

37

42

44

312

70

300

150

500

24

28

mA

30

mA

37

42

mA

44

mA

312

mW

70

300 ps/V

150

500 ps/V

NOTES

1Absolute maximum ratings are limiting values, to be applied individually, and beyond which serviceability of the circuit may be impaired. Functional operability under

any of these conditions is not necessarily implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

2Typical thermal impedance

24-Lead Cerdip

θJA = 56°C/W; θJC = 16°C/W

28-Leadless PLCC (Plastic) θJA = 60°C/W; θJC = 22°C/W

28-Leaded Ceramic LCC

θJA = 69°C/W; θJC = 25°C/W

3RSET = 10 kΩ (Full-scale delay = 100 ns).

4The digital data inputs must remain stable for the specified time prior to the LATCH ENABLE signal.

5The digital data inputs must remain stable for the specified time after the LATCH ENABLE signal.

6The TRIGGER and RESET inputs are differential and must be driven relative to one another. Both of these inputs are ECL compatible, but can also be used with

TTL logic families in a limited fashion.

7Outputs terminated through 50 Ω resistors to –2.0 V.

8Program Delay = 0.0 ps (Digital Data = 00H). In Operation, any programmed delays are in addition to the Minimum Propagation Delay.

9Change in total delay through AD9500, exclusive of changes in minimum propagation delay t PD.

10Measured from the 50% transition point of the reset signal input, to the 50% transition point of the resetting output.

11Minimum time from falling edge of RESET to triggering input, to ensure a valid output event.

12Minimum time from triggering event to rising edge of RESET, to ensure a valid output event.

13Measured from the LATCH ENABLE input to the point when the AD9500 becomes 8-bit accurate again, after a full-scale change in the programmed delay.

14Standard 10K and 10KH ECL families operate with a 1.1 mV/°C drift by design.

15Supply voltages should remain stable within ±5% for normal operation.

16Measured at ± 5% of –VS and +VS.

Specifications subject to change without notice.

EXPLANATION OF TEST LEVELS

Test Level

I – 100% production tested.

II – 100% production tested at +25°C, and sample tested at

specified temperatures.

III – Periodically sample tested.

IV – Parameter is guaranteed by design and characterization

testing.

V – Parameter is a typical value only.

VI – All devices are 100% production tested at +25°C. 100%

production tested at temperature extremes for extended

temperature devices; sample tested at temperature ex-

tremes for commercial/industrial devices.

ORDERING GUIDE

Model

Temperature Package

Ranges

Descriptions

Package

Options

AD9500BP –25°C to +85°C

AD9500BQ –25°C to +85°C

AD9500TE –55°C to +125°C

AD9500TQ –55°C to +125°C

28-Leadless PLCC (Plastic),

Industrial Temperature

24-Lead Cerdip,

Industrial Temperature

28-Leaded LCC,

Extended Temperature

24-Lead Cerdip,

Extended Temperature

P-28A

Q-24

E-28A

Q-24

REV. D

–3–