LTC2184CUPPBF Просмотр технического описания (PDF) - Linear Technology

Номер в каталоге

Компоненты Описание

производитель

LTC2184CUPPBF Datasheet PDF : 36 Pages

| |||

LTC2185/LTC2184/LTC2183

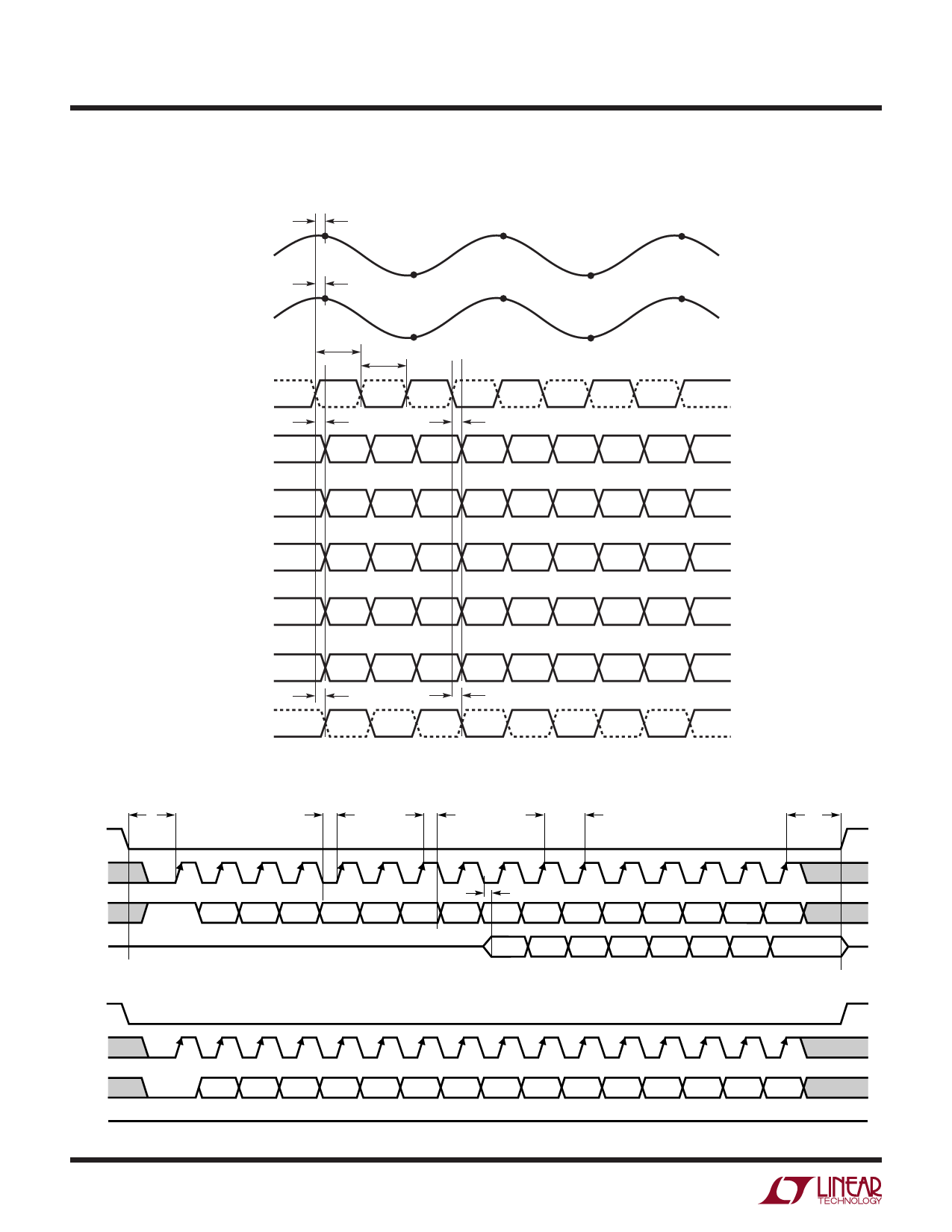

timing DIAGRAMS

CH 1

ANALOG

INPUT

CH 2

ANALOG

INPUT

ENC–

ENC+

D1_0_1+

D1_0_1–

D1_14_1•••5+

D1_14_15–

D2_0_1+

D2_0_1–

D2_14_1•••5+

D2_14_15–

OF2_1+

OF2_1–

CLKOUT+

CLKOUT –

Double Data Rate LVDS Output Mode Timing

All Outputs Are Differential and Have LVDS Levels

tAP

A

tAP

A+1

A+2

A+3

A+4

B

tH

B+1

tL

B+2

B+3

B+4

tD

BIT 0

A-6

BIT 1 BIT 0

A-6

A-5

tD

BIT 1

A-5

BIT 0

A-4

BIT 1

A-4

BIT 0

A-3

BIT 1

A-3

BIT 0

A-2

BIT 14 BIT 15 BIT 14 BIT 15 BIT 14 BIT 15 BIT 14 BIT 15 BIT 14

A-6

A-6

A-5

A-5

A-4

A-4

A-3

A-3

A-2

BIT 0

B-6

BIT 1 BIT 0

B-6

B-5

BIT 1

B-5

BIT 0

B-4

BIT 1

B-4

BIT 0

B-3

BIT 1

B-3

BIT 0

B-2

BIT 14 BIT 15 BIT 14 BIT 15 BIT 14 BIT 15 BIT 14 BIT 15 BIT 14

B-6

B-6

B-5

B-5

B-4

B-4

B-3

B-3

B-2

OF

OF

OF

OF

OF

OF

OF

OF

OF

B-6

A-6

B-5

A-5

B-4

A-4

B-3

A-3

B-2

tC

tC

218543 TD03

SPI Port Timing (Readback Mode)

tS

tDS

tDH

tSCK

tH

CS

SCK

tDO

SDI

R/W

A6

A5

A4

A3

A2

A1

A0

XX

XX

XX

XX

XX

XX

XX

XX

SDO

HIGH IMPEDANCE

D7

D6

D5

D4

D3

D2

D1

D0

SPI Port Timing (Write Mode)

CS

SCK

SDI

R/W

A6

A5

A4

A3

A2

A1

A0

D7

D6

D5

D4

D3

D2

D1

D0

SDO

HIGH IMPEDANCE

10

218543 TD04

218543f