PI74ALVTC16374 Просмотр технического описания (PDF) - Pericom Semiconductor Corporation

Номер в каталоге

Компоненты Описание

производитель

PI74ALVTC16374 Datasheet PDF : 9 Pages

| |||

PI74ALVTC16374 1122334455667788990011223344556677889900112233445566778899001122112233445566778899001122334455667788990011223344556677889900112211223344556677889900112233445566778899001122334455667788990011221122334455667788990011223344556677889900112233445566778899001122112233445566778899001122

16-Bit D-Type Flip-Flop

with 3-State Outputs

Product Features

• The PI74ALVTC Family is designed for low voltage

operation, VDD = 1.8V to 3.6V

• Supports Live Insertion

• 3.6V I/O Tolerant Inputs and Outputs

• Bus Hold

• High Drive, –32/64mA @ 3.3V

• Uses patented Noise Reduction Circuitry

• Power-Off high impedance inputs and outputs

• Industrial operation at –40°C to +85°C

• Packaging (Pb-free & Green available):

– 48-pin 240 mil wide plastic TSSOP (A)

Product Description

The PI74ALVTC16374 is particularly suitable for implementing

buffer registers, I/O ports, bidirectional bus drivers, and working

registers. This device can be used as two 8-bit flip-flops or one 16-

bit flip-flop. On the positive transition of the clock (CLK) input, the

Q outputs of the flip-flop take on the logic levels set up at the data

(D) inputs.

A buffered Output Enable (OE) input can be used to place the eight

outputs in either a normal logic state (high or low logic levels) or

a high-impedance state in which the outputs neither load nor drive

the bus lines significantly. The high-impedance state and the

increased drive provide the capability to drive bus lines without

need for interface or pullup components. OE does not affect

internal operations of the flip-flop. Old data can be retained or new

data can be entered while the outputs are in the high-impedance

state.

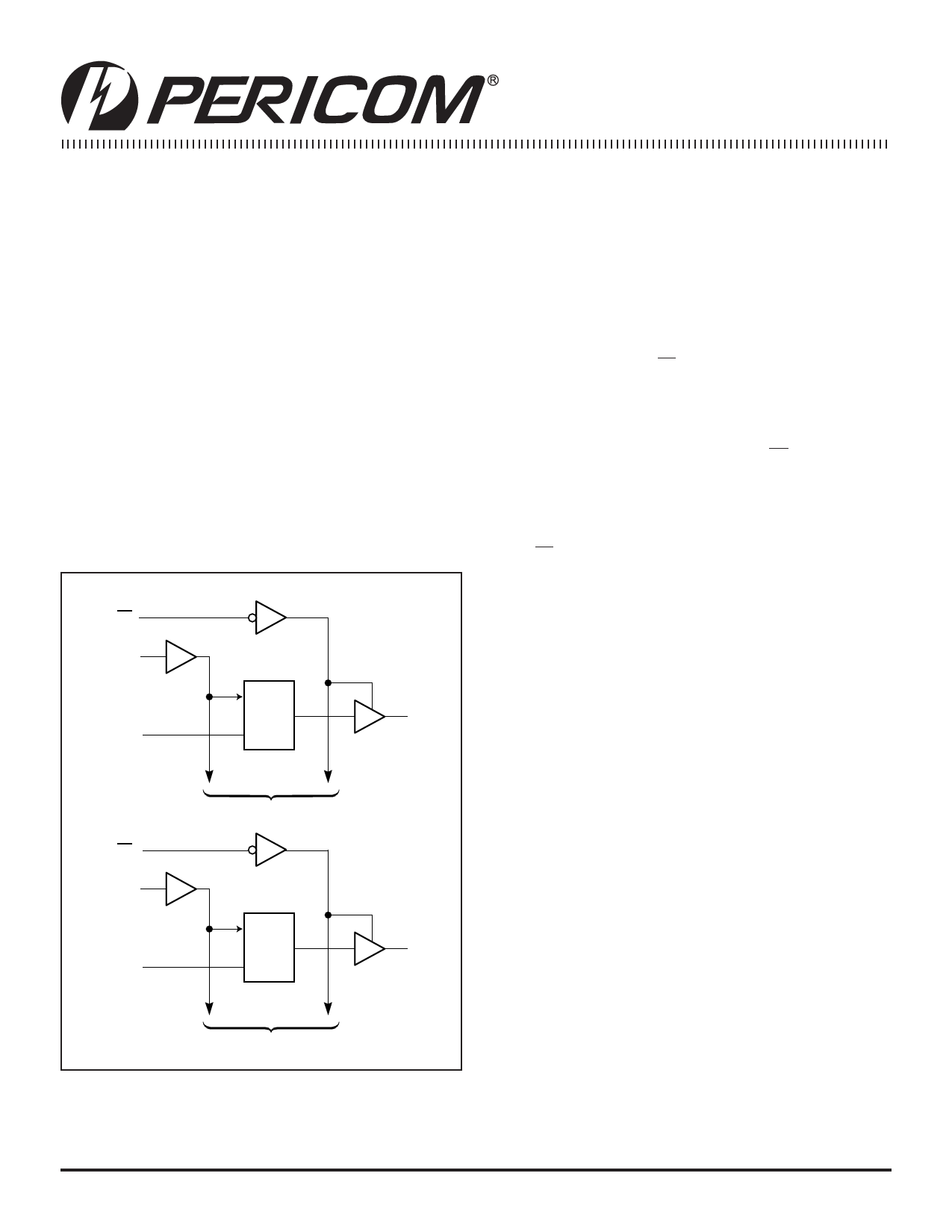

Logic Block Diagram

1

1OE

1CLK 48

>C1

47

1D1

1D

2 1Q1

To ensure the high-impedance state during power up or power

down, OE should be tied to VDD through a pullup resistor; whose

minimum value is determined by the current-sinking capability of

the driver.

The family offers both I/O Tolerant, which allows it to operate in

mixed 1.8/3.6V systems, and “Bus Hold,” which retains the data

input’s last state whenever the data input goes to high-imped-

ance, preventing “floating” inputs and eliminating the need for

pullup/down resistors.

24

2OE

2CLK 25

36

2D1

To Seven Other Channels

>C1

1D

13 2Q1

To Seven Other Channels

1

PS8356C 11/06/08