AD7872BR Просмотр технического описания (PDF) - Analog Devices

Номер в каталоге

Компоненты Описание

производитель

AD7872BR Datasheet PDF : 16 Pages

| |||

(VDD = +5 V ؎ 5%, VSS = –5 V ؎ 5%, AGND = DGND =

AD7871/AD7872–SPECIFICATIONS O V, fCLK = 2 MHz external, fSAMPLE = 83 kHz unless otherwise

noted.) All Specifications TMIN to TMAX unless otherwise noted.

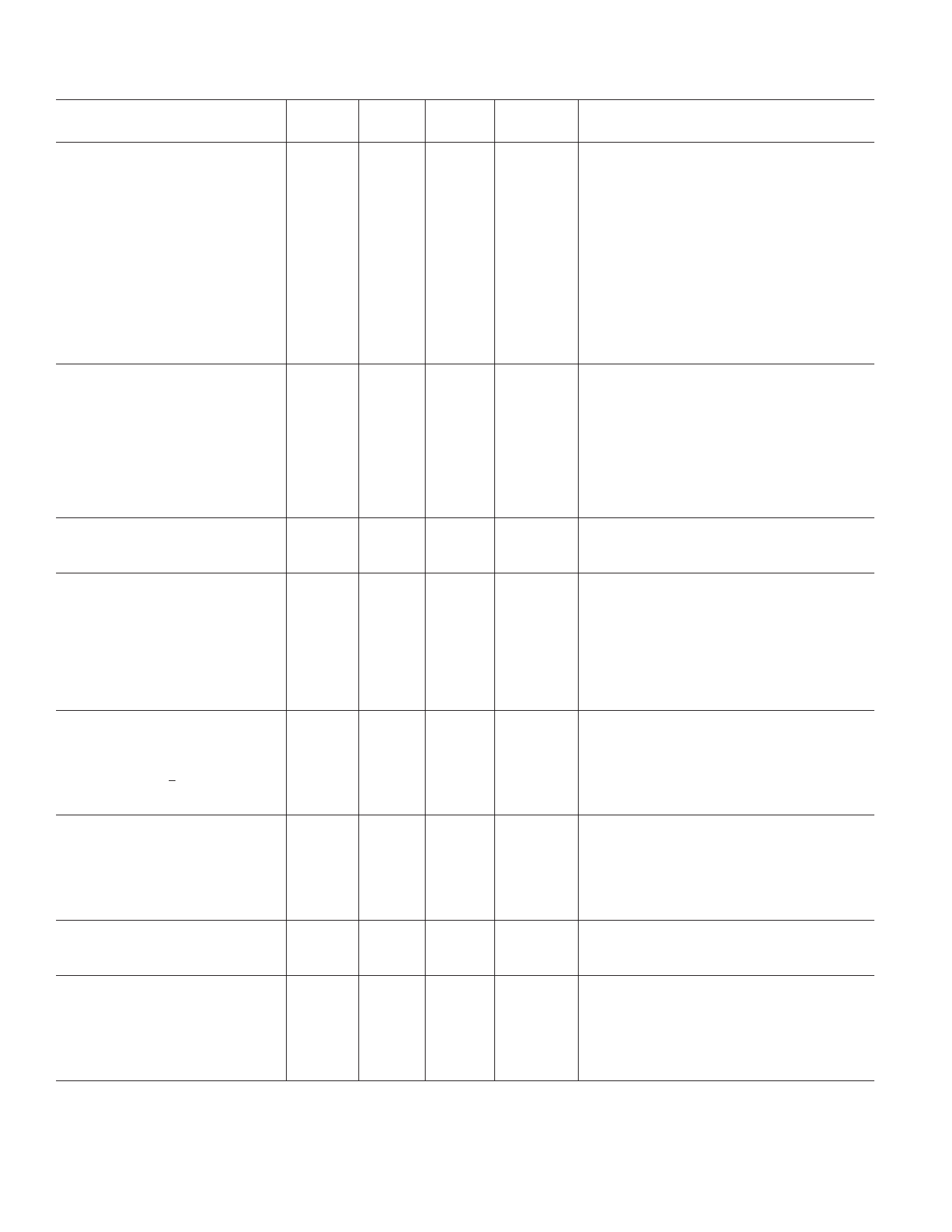

Parameter

J, A

K

T, B

Versions1 Version1 Versions1 Units

Test Conditions/Comments

DYNAMIC PERFORMANCE2

Signal-to-Noise Ratio3 (SNR) @ +25°C 80

TMIN to TMAX

80

Total Harmonic Distortion (THD)

–86

Peak Harmonic or Spurious Noise

–86

Intermodulation Distortion (IMD)

Second Order Terms

–86

Third Order Terms

–86

Track/Hold Acquisition Time

2

80

79

80

79

–88

–85

–88

–85

–88

–85

–88

–85

2

2

dB min

dB min

dB max

dB typ

dB max

dB typ

dB max

dB typ

dB max

dB typ

µs max

VIN = 10 kHz Sine Wave

SNR is Typically 82 dB for <VIN<41.5 kHz;

VIN = 10 kHz Sine Wave

VIN = 10 kHz.

fa = 9 kHz, fb = 9.5 kHz, fSAMPLE = 50 kHz

fa = 9 kHz, fb = 9.5 kHz, fSAMPLE = 50 kHz

DC ACCURACY

Resolution

14

Minimum Resolution for Which

No Missing Codes Are Guaranteed 14

Integral Nonlinearity @ +25°C

Integral Nonlinearity

Bipolar Zero Error

± 12

Positive Gain Error4

± 12

Negative Gain Error4

± 12

14

14

14

14

± 1/2

± 1/2

±1

±1

± 12

± 12

± 12

± 12

± 12

± 12

Bits

Bits

LSB typ

LSB max

LSB max

LSB max

LSB max

ANALOG INPUT

Input Voltage Range

Input Current

±3

± 500

±3

± 500

±3

± 500

Volts

µA max

REFERENCE OUTPUT

REF OUT @ +25°C

TMIN to TMAX

REF OUT Tempco

Reference Load Sensitivity

(∆REF OUT/∆I)

2.99/3.01

2.98/3.02

2.99/3.01 2.99/3.01

2.98/3.02 2.98/3.02

± 40

± 40

V min/V max

V min/V max

ppm/°C max

Typically 35 ppm

± 1.2

± 1.2

± 1.2

mV max

Reference Load Current Change (0 µA–300 µA);

Reference Load Should Not Be Changed During

Conversion

LOGIC INPUTS

Input High Voltage, VINH

2.4

Input Low Voltage, VINL

0.8

Input Current, IIN

± 10

Input Current (14/8/CLK Input Only) ± 10

Input Capacitance, CIN5

10

LOGIC OUTPUTS

Output High Voltage, VOH

4.0

Output Low Voltage, VOL

0.4

DB13 – DB0

Floating-State Leakage Current

10

Floating-State Output Capacitance5 15

2.4

2.4

0.8

0.8

± 10

± 10

± 10

± 10

10

10

4.0

4.0

0.4

0.4

10

10

15

15

V min

V max

µA max

µA max

pF max

V min

V max

µA max

pF max

VDD = 5 V ± 5%

VDD = 5 V ± 5%

VIN = 0 V to VDD

VIN = VSS to VDD

ISOURCE = 40 µA

ISINK = 1.6 mA

CONVERSION TIME

External Clock

Internal Clock

10

10

10

10.5

10.5

11

µs max

µs max

The Internal Clock Has a Nominal Value of 2 MHz

POWER REQUIREMENTS

VDD

VSS

IDD

ISS

Power Dissipation

+5

+5

+5

V nom

± 5% for Specified Performance

–5

–5

–5

V nom

± 5% for Specified Performance

13

13

13

mA max

Typically 6 mA

6

6

6

mA max

Typically 4 mA

95

95

95

mW max

Typically 50 mW

NOTES

1Temperature ranges are as follows: J, K versions, 0°C to +70°C; A, B versions, –40°C to +85°C; T version; –55°C to +125°C.

2VIN = ± 3 V.

3SNR calculation includes distortion and noise components.

4Measured with respect to internal reference.

5Sample tested @ +25°C to ensure compliance.

Specifications subject to change without notice.

–2–

REV. D