# UT1553B RTI Remote Terminal Interface

#### **FEATURES**

- ☐ Complete MIL-STD-1553B Remote Terminal interface compliance

- Dual-redundant data bus operation supported

- ☐ Internal illegalization of selected mode code commands

- External illegal command definition capability

- Automatic DMA control and address generation

- Operational status available via dedicated lines or internal status register

- ☐ ASD/ENASC (formerly SEAFAC) tested and approved

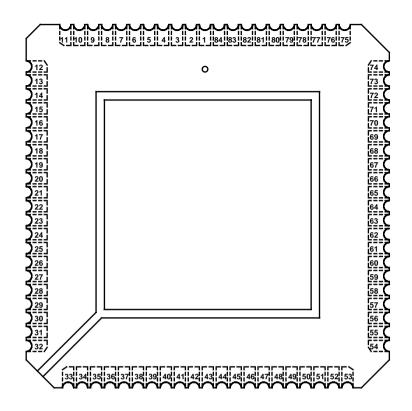

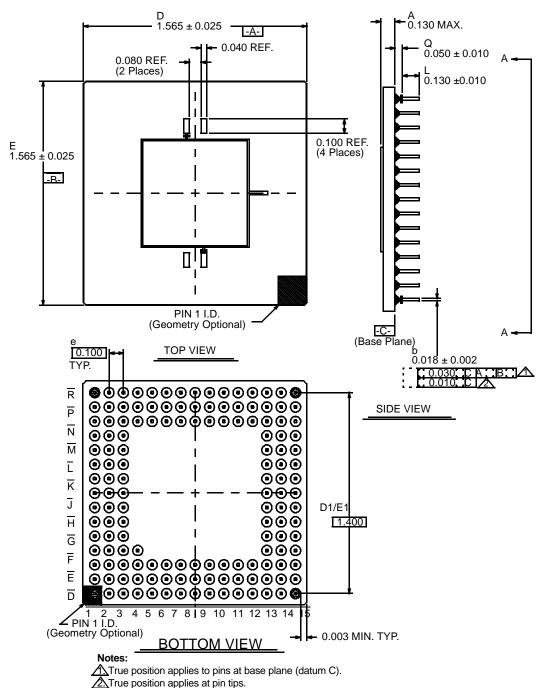

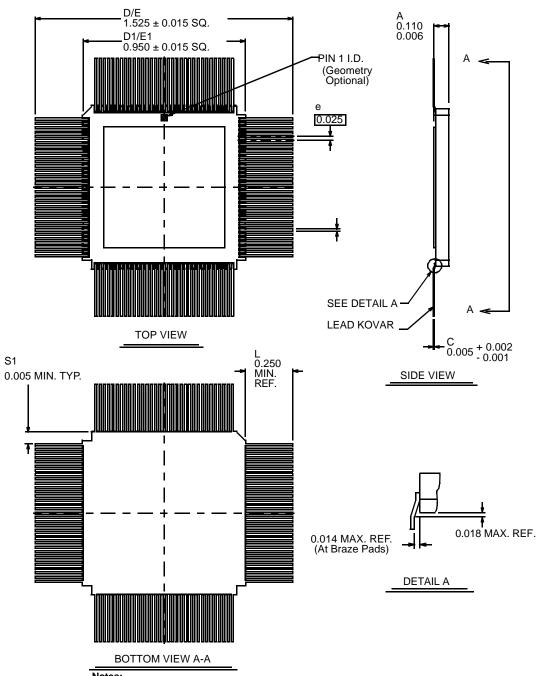

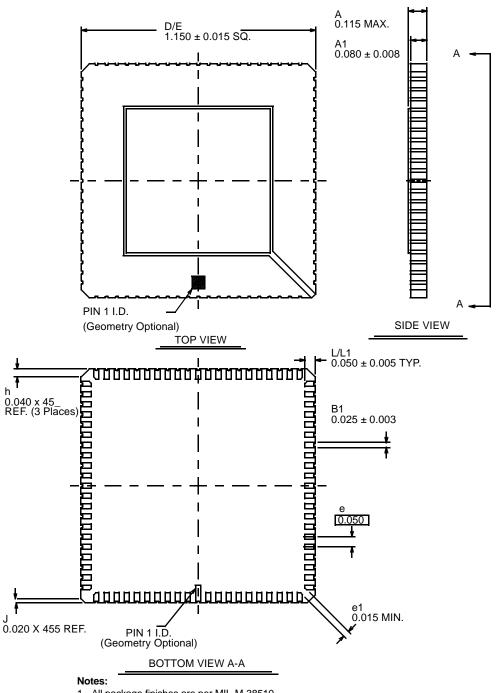

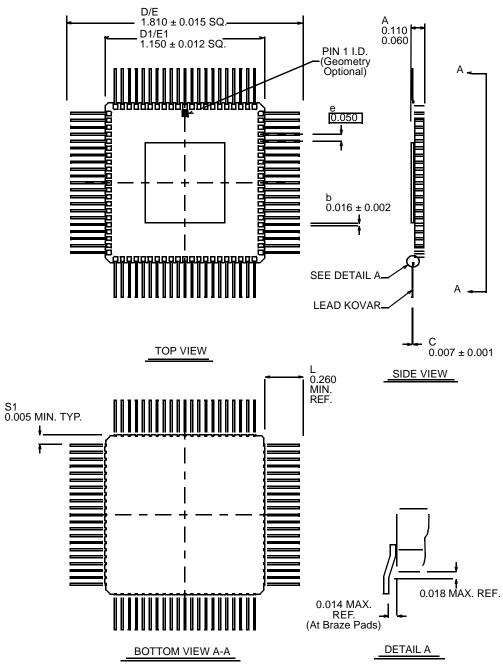

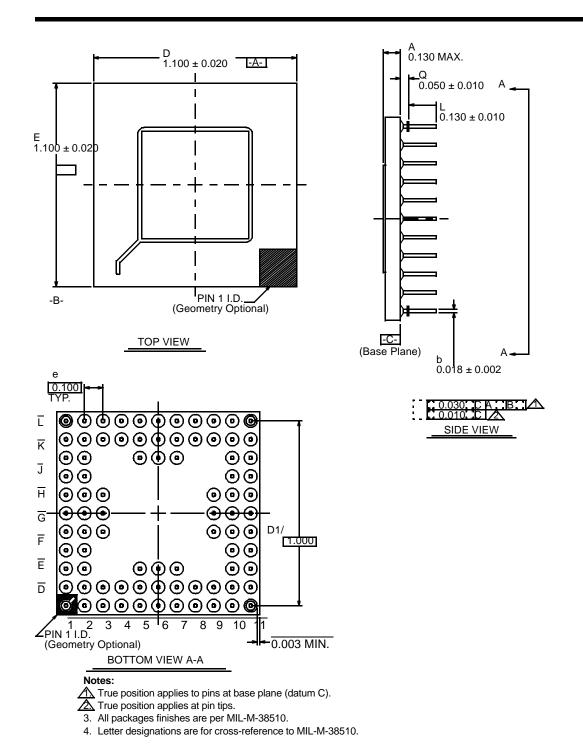

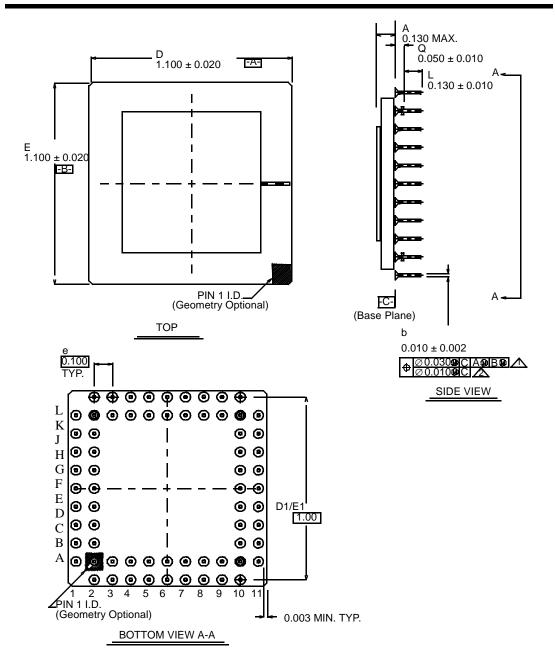

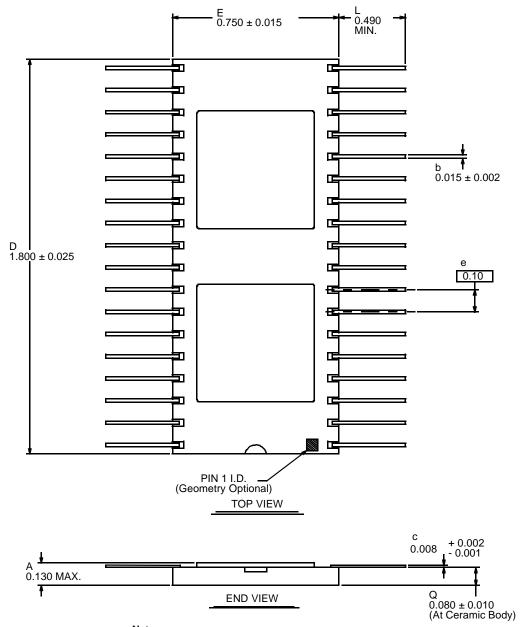

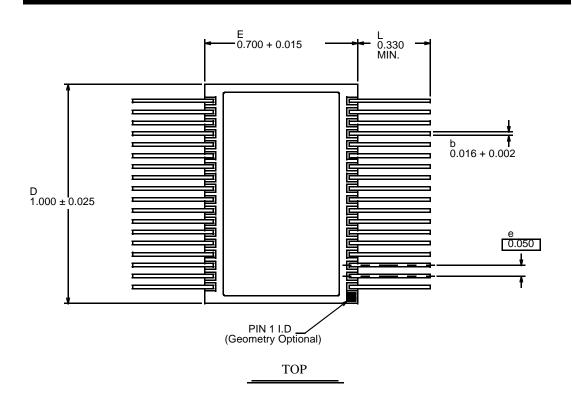

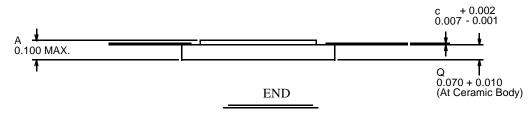

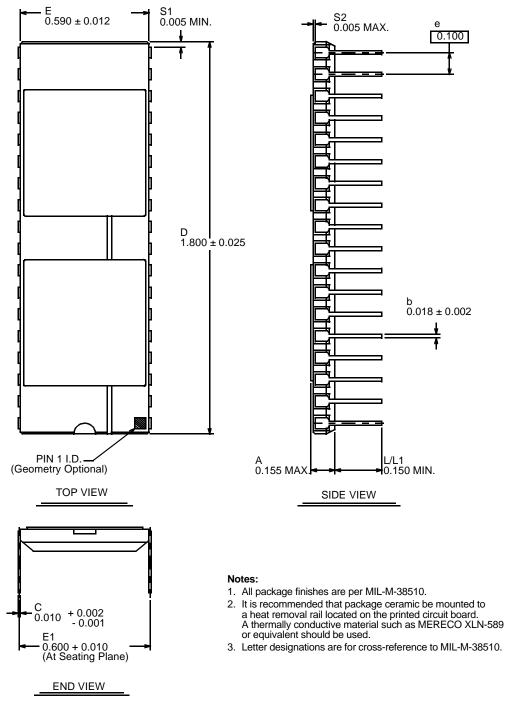

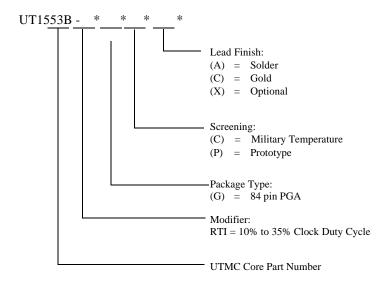

- Available in ceramic 84-lead leadless chip carrier and 84-pin pingrid array

- ☐ Full military operating temperature range, -55°C to +125°C, screened to the specific test methods listed in Table I of MIL-STD-883, Method 5004, Class B

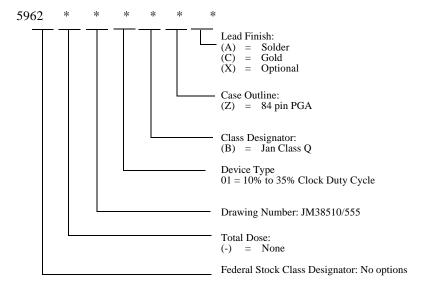

- JAN-qualified devices available

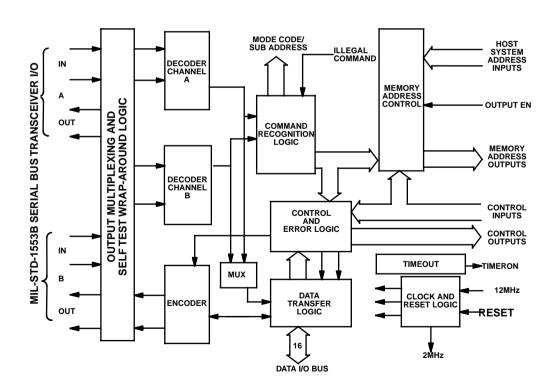

Figure 1. UT1553B RTI Functional Block Diagram

# **Table of Contents**

| 1.0 | ARCHITECTURE AND OPERATION.                                                                       |

|-----|---------------------------------------------------------------------------------------------------|

|     | 1.1 Host Interface 1.1.1 Direct Memory Access                                                     |

|     | 1.1.2 Transparent Memory Access 1.2 Internal Register Description 1.3 Mode Codes and Subaddresses |

|     | 1.4 MIL-STD-1553B Subaddress and Mode Codes 1.5 Remote Terminal Address                           |

|     | 1.6 Internal Self-Test                                                                            |

|     | 1.8 Encoder and Decoder                                                                           |

| 2.0 | MEMORY MAP EXAMPLE                                                                                |

| 3.0 | PIN IDENTIFICATION AND DESCRIPTION                                                                |

| 4.0 | MAXIMUM AND RECOMMENDED OPERATING CONDITIONS                                                      |

| 5.0 | DC ELECTRICAL CHARACTERISTICS                                                                     |

| 6.0 | AC ELECTRICAL CHARACTERISTICS                                                                     |

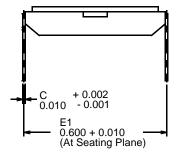

| 7.0 | PACKAGE OUTLINE DRAWINGS 33                                                                       |

### 1.0 ARCHITECTURE AND OPERATION

The UT1553B RTI is an interface device linking a MIL-STD-1553 serial data bus and a host microprocessor system. The RTI's MIL-STD-1553B interface includes encoding/decoding logic, error detection, command recognition, memory address control, clock, and reset circuits.

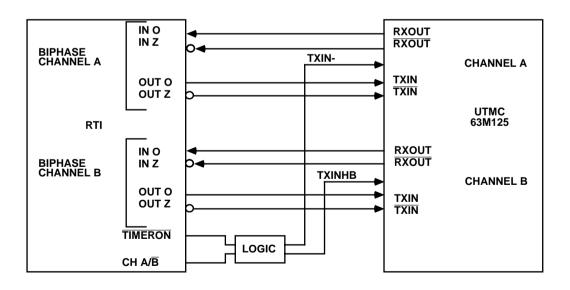

#### Decoders

The UT1553B RTI contains two separate free-running decoders to insure that all redundancy requirements of MIL-STD-1553B are met. Each decoder receives, decodes, and verifies biphase Manchester II data. Proper frequency and edge skew are also verified.

#### **Command Recognition Logic**

The command recognition logic monitors the output of both decoders at all times. Recognition of a valid command causes a reset of present interface activity followed by execution of the command. This procedure meets the requirement for superseding valid commands.

#### Encoder

The encoder receives serial data from the data transfer logic, converts it to Manchester II form with proper synchronization and parity, and passes it to the output and self-test logic.

#### **Data Transfer Logic**

The data transfer logic provides double-buffered 16-bit parallel-to-serial and serial-to-parallel conversion during reception and transmission of data.

#### Memory Address Control

The memory address control logic controls the output of the three-state address lines during memory access. In DMA system implementations, the memory address control provides RTI-generated addresses. In a pseudo-dual-port memory configuration, the memory address control logic provides either RTI-generated or host system addressing.

#### **Control and Error Logic**

The control and error logic performs the following four major functions:

- Interface control for proper processing of MIL-STD-1553B commands

- Error checking of both MIL-STD-1553B data and RTI operation

- Memory control (DMA or pseudo-dual-port) for proper data transfer

- Operational status and control signal generation

#### **Output Multiplexing and Self-Test Logic**

This logic directs the output of the encoder to one of four places:- Channel A outputs

- Channel B outputs

- Channel A decoders during self-test

- Channel B decoders during self-test

#### **Clock and Reset Logic**

The UT1553B RTI requires a 12MHz input clock to operate properly. The RTI provides a 2MHz output for the system designer to use. The device provides a hardware reset pin as well as software-generated reset.

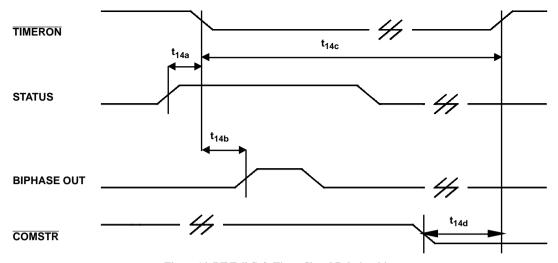

#### **Timer Logic**

The UT1553B RTI has a built-in 730ms timer that is activated when the encoder is about to transmit. The timer is reset upon receipt of a valid command, master reset, or a time-out condition.

#### 1.1 HOST INTERFACE

Configure the RTI into the host system for either a direct memory or transparent memory access. The following sections discuss the system configuration for each method of memory management.

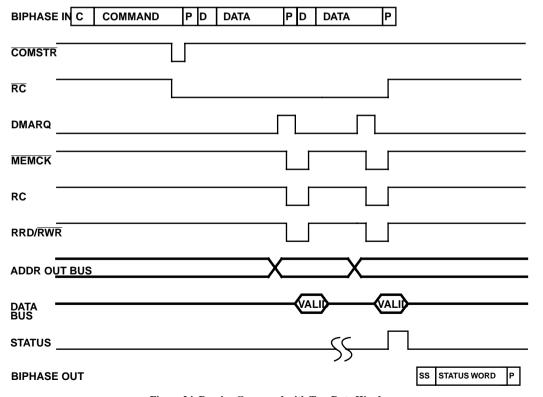

#### 1.1.1 Direct Memory Access

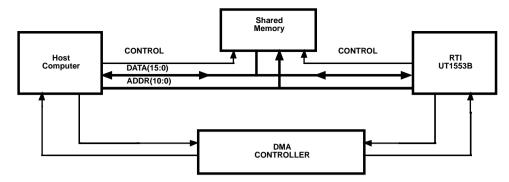

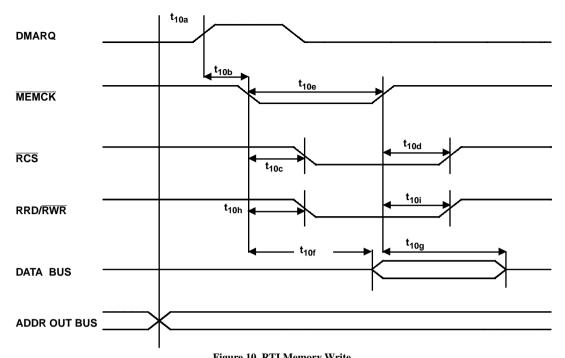

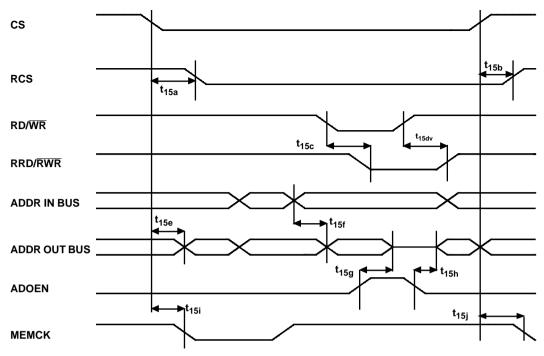

In the direct memory access configuration the RTI and host arbitrate for the shared 2K x 16 memory space. To request access to memory the RTI asserts direct memory request output (DMARQ); the system bus arbiter grants the RTI access to memory by asserting the direct memory access grant signal (MEMCK). The system arbiter should not assert the MEMCK signal before the RTI has requested access to memory (i.e., DMARQ) asserted).

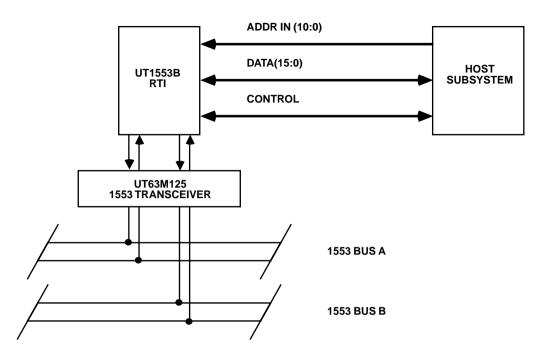

Once granted access to memory, the RTI address out (ADDR OUT(10:0)), RAM chip select ( $\overline{RCS}$ ), RAM read/write (RRD/ $\overline{RWR}$ ), and Data bus (DATA I/O(15:0)) provide the interface signals to control the memory access. Figure 2 shows an example of a direct memory access system configuration; for clarity the interface buffers and logic are excluded. The host microprocessor also gains access to memory by arbitration.

Take care to insure that bus contention does not occur between the host and RTI Address buses or memory control signals. To place the RTI Address Out bus in a high impedance state negate the  $\overline{ADOEN}$  input pin. Also note that outputs  $\overline{RCS}$  and RRD/ $\overline{RWR}$  are not three-state outputs. When the RTI is not writing to memory, bidirectional Data bus DATA I/O(15:0) is an input (i.e., not actively driving the bus).

Figure 2. Direct Memory Access Configuration

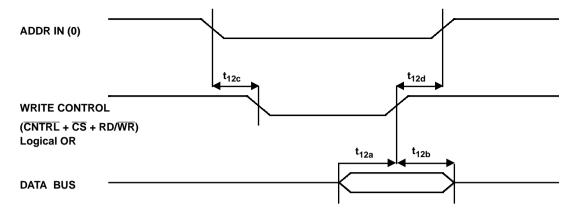

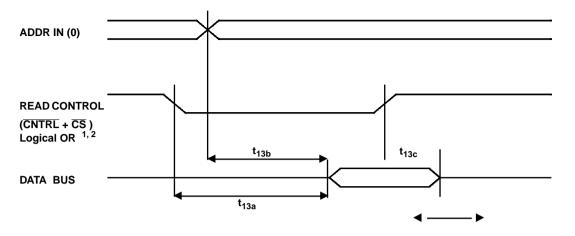

The host microprocessor gains access to the RTI internal registers by controlling input pins  $\overline{CS}$ ,  $\overline{CTRL}$ , ADDR IN (10:0), and RD/ $\overline{WR}$ . During message processing the host microprocessor should limit access to RTI internal registers.

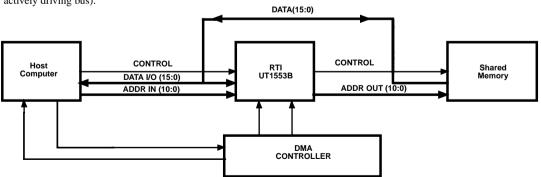

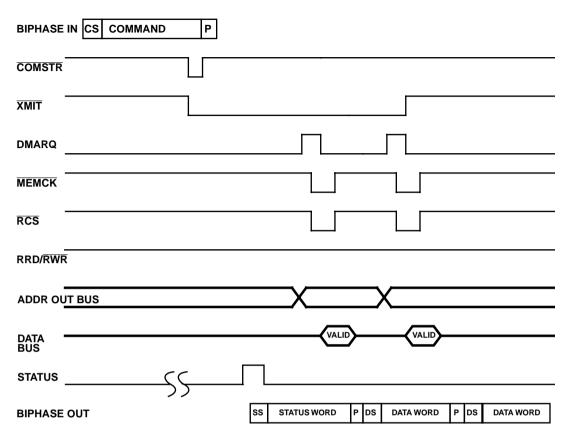

#### 1.1.2 Transparent Memory Access

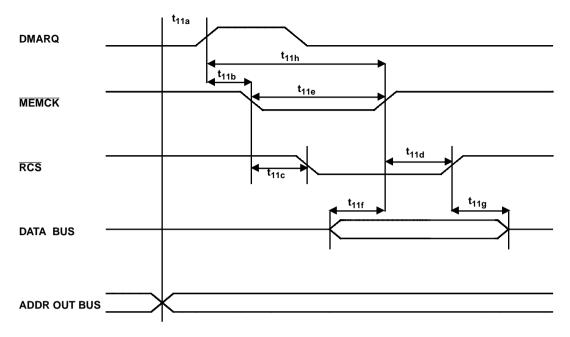

Configured in the transparent memory mode the host microprocessor accesses shared memory through the RTI. Arbitration for access to the bus is performed as discussed in section 1.1.1 of this document.

When granted access to memory, the RTI asserts memory control signals ADDR OUT(10:0),  $\overline{RCS}$ , and RRD/ $\overline{RWR}$ . For host-controlled memory accesses the RAM memory address from the host is propagated from the Address In bus ADDR IN (10:0) to the Address Out bus ADDR OUT (10:0). Memory control signals RD/ $\overline{WR}$  and  $\overline{CS}$  are also propagated through the RTI as RRD/ $\overline{RWR}$  and  $\overline{RCS}$ . Input  $\overline{CTRL}$  is negated during all transparent memory accesses to prevent the RTI from inadvertently performing an internal register access or software reset. While  $\overline{CS}$  is asserted, the RTI's bidirectional Data bus DATA I/O (15:0) is an input (i.e., not actively driving bus).

The host microprocessor gains access to the RTI internal registers by controlling input pins  $\overline{CS}$ ,  $\overline{CTRL}$ , ADDR IN (10:0), and RD/ $\overline{WR}$ . During message processing the host microprocessor should limit access to RTI internal registers. The host should not assert  $\overline{CS}$  while the RTI is performing a memory access.

#### 1.2 Internal Register Description

The RTI uses three internal registers to allow the host to control the RTI operation and monitor its status. The host uses the following inputs Control ( $\overline{CTRL}$ ), Chip Select ( $\overline{CS}$ ), Read/Write (RD/ $\overline{WR}$ ), and ADDR IN (0) to read the 16-bit System Register or write to the 8-bit Control Register. The Control Register toggles bits in the MIL-STD-1553B status word, enables biphase inputs, selects terminal active flag, and puts the part in self-test. The System Register supplies operational status of the UT1553B RTI to the host. The Last Command Register saves the command word for a Transmit Last Command mode code, along with operational status from the System Register.

Figure 3. Transparent Memory Access Configuration

Control Register (Write Only)

The 8-bit write-only Control Register manages the operation of the RTI. Write to the Control Register by applying a logic zero to  $\overline{CS}$ ,  $\overline{CTRL}$ ,  $RD/\overline{WR}$ , and ADDR IN (0); if ADDR IN (0) is a logic one a master reset occurs. Data is loaded into the Control Register via I/O pins DATA(7:0). Control Register writes must occur 50ns before the rising edge of  $\overline{COMSTR}$  to latch data in the outgoing status word.

| Bit<br>Number | Initial<br>Condition | Description                                                                                                                                                          |

|---------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0             | [0]                  | Channel A Enable. A logic one enables Channel A biphase inputs.                                                                                                      |

| 1             | [0]                  | Channel B Enable. A logic one enables Channel B biphase inputs.                                                                                                      |

| 2             | [0]                  | Terminal Flag. A logic one sets the Terminal Flag bit of the Status Register.                                                                                        |

| 3             | [0]                  | System Busy. A logic one sets the Busy bit of the System Register and inhibits RTI access to memory. No data words are retrieved or stored; command word is stored.  |

| 4             | [0]                  | Subsystem Busy. A logic one sets the Subsystem Flag bit of the Status Register.                                                                                      |

| 5             | [0]                  | Self-Test Channel Select. This bit selects which channel the internal self-test checks; a logic one selects Channel A and a logic zero selects Channel B.            |

| 6             | [0]                  | Self-Test Enable. A logic one sets the RTI in the internal self-test mode and inhibits normal operation. Internal testing is not visible on biphase output channels. |

| 7             | [0]                  | Service Request. A logic one sets the Service Request bit of the Status Register.                                                                                    |

#### CONTROL REGISTER (WRITE ONLY)

| Х   | Х | Х | Х | х | Х | х | Х | SRV<br>RQ | SELF<br>TEST | SELF<br>CH | SUBS | BUSY | TF  | CH B<br>EN | CH A<br>EN |

|-----|---|---|---|---|---|---|---|-----------|--------------|------------|------|------|-----|------------|------------|

| MSB |   |   |   |   |   |   |   | [0]       | [0]          | [0]        | [0]  | [0]  | [0] | [0]        | [0]<br>LSB |

[] defines reset state

Figure 4. Control Register

#### System Register (Read Only)

The 16-bit read-only System Register provides the RTI system status. Read the System Register by applying a logic zero to  $\overline{\text{CS}}$ ,  $\overline{\text{CTRL}}$ , ADDR IN (0), and a logic one to RD/WR. The 16-bit contents of the System Register are read from data I/O pins DATA(15:0).

| Bit<br>Number | Initial<br>Condition | Description                                                                                                                                                                                                                                                                      |

|---------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0             | [0]                  | MCSA(0). The LSB of the mode code or subaddress as indicated by the logic state of bit 5.                                                                                                                                                                                        |

| 1             | [0]                  | MCSA(1). Mode code or subaddress as indicated by the state of bit 5.                                                                                                                                                                                                             |

| 2             | [0]                  | MCSA(2). Mode code or subaddress as indicated by the state of bit 5.                                                                                                                                                                                                             |

| 3             | [0]                  | MCSA(3). Mode code or subaddress as indicated by the state of bit 5.                                                                                                                                                                                                             |

| 4             | [0]                  | MCSA(4). Mode code or subaddress as indicated by the state of bit 5.                                                                                                                                                                                                             |

| 5             | [0]                  | MC/SA. A logic one indicates that bits 4 through 0 are the subaddress of the last command word, and that the last command word was a normal transmit orreceive command. A logic zero indicates that bits 4 through 0 are a mode code, and that the last command was a mode code. |

| 6             | [1]                  | Channel $A/\overline{B}$ . A logic one indicates that the most recent command arrived on Channel A; a logic zero indicates that it arrived on Channel B.                                                                                                                         |

| 7  | [0] | Channel B Enabled. A logic one indicates that Channel B is available for both reception and transmission.                                                                                                                                                                                 |

|----|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8  | [0] | Channel A Enabled. A logic one indicates that Channel A is available for both reception and transmission.                                                                                                                                                                                 |

| 9  | [1] | Terminal Flag Enabled. A logic one indicates that the Bus Controller has not issued an Inhibit Terminal Flag mode code. A logic zero indicates that the Bus Controller, via the above mode code, is overriding the host system's ability to set the Terminal Flag bit of the status word. |

| 10 | [0] | Busy. A logic one indicates the Busy bit is set. This bit is reset when the SystemBusy bit in the Control Register is reset.                                                                                                                                                              |

| 11 | [0] | Self-Test. A logic one indicates that the RTI is in the self-test mode. This bit is reset when the self-test is terminated.                                                                                                                                                               |

| 12 | [0] | TA Parity Error. A logic one indicates the wrong Terminal Address parity; it causes the biphase inputs to be disabled and a message error condition. This bit is reset by reloading the terminal address latch with correct parity.                                                       |

| 13 | [0] | Message Error. A logic one indicates that a message error has occurred since the last System Register read. This bit is not reset until the System Register has been examined and the message error condition is removed.                                                                 |

| 14 | [0] | Valid Message. A logic one indicates that a valid message has been received since the last System Register read. This bit is not reset until the System Register has been examined.                                                                                                       |

| 15 | [0] | Terminal Active. A logic one indicates the device is executing a transmit or receive operation. The state of this bit is the logical NAND of the external $\overline{\text{XMIT}}$ and $\overline{\text{RCV}}$ pins.                                                                      |

## SYSTEM REGISTER (READ ONLY)

| TERM<br>ACTV | VAL<br>MESS | MESS<br>ERR | TAPA<br>ERR | SELF-<br>TEST | BUSY | TFEN | CH A<br>EN | CH B<br>EN | CHNL<br>A/B | MC/<br>SA | MCSA<br>4 | MCSA<br>3 | MCSA<br>2 | MCSA<br>1 | MCSA<br>0 |

|--------------|-------------|-------------|-------------|---------------|------|------|------------|------------|-------------|-----------|-----------|-----------|-----------|-----------|-----------|

| [0]          | [0]         | [0]         | [0]         | [0]           | [0]  | [1]  | [0]        | [0]        | [1]         | [0]       | [0]       | [0]       | [0]       | [0]       | [0]       |

| MSB          |             |             |             |               |      |      |            |            |             |           |           |           |           |           | LSB       |

[] defines reset state

Figure 5. System Registers

#### Last Command Register (Read Only)

The 16-bit read-only Last Command Register provides the host with last command and operational status information. The RTI transmits the lower 11 bits of this register along with terminal address upon receipt of a Transmit Last Command mode code. Read the Last Command Register by applying a logic zero to  $\overline{CS}$ ,  $\overline{CTRL}$ , and a logic one to  $\overline{RD/WR}$  and  $\overline{RD/$

| Bit          | Initial   |                                                        |

|--------------|-----------|--------------------------------------------------------|

| Number       | Condition | Description                                            |

| 0 through 10 | [all 1s]  | Least significant 11 bits of the last command word.    |

| 11           | [0]       | Busy Bit. System Register bit 10.                      |

| 12           | [0]       | Self-test. System Register bit 11.                     |

| 13           | [1]       | Terminal Flag Enabled. System Register bit 9.          |

| 14           | [1]       | Channel A/B. System Register bit 6.                    |

| 15           | [1]       | Illegal Command. The RTI illegalized the last command. |

#### 1.3 Mode Codes and Subaddresses

The UT1553B RTI provides subaddress and mode code decoding meeting MIL-STD-1553B. In addition, the device has automatic internal illegal command decoding for reserved MIL-STD-1553B mode codes. Upon command word validation and decode, status pins MCSA(4:0) and  $\overline{\text{MC}}/\text{SA}$  become valid. Status pin  $\overline{\text{MC}}/\text{SA}$  will indicate whether the data pins MCSA(4:0) are mode code or subaddress information. Status Register bits 5 through 0 contain the same information as pins MCSA(4:0) and  $\overline{\text{MC}}/\text{SA}$ .

The system designer can use signals MCSA(4:0),  $\overline{\text{MC}}/\text{SA}$ ,  $\overline{\text{BRDCST}}$ ,  $\overline{\text{XMIT}}$ , and  $\overline{\text{RCV}}$  to illegalize mode codes, subaddresses, and other message formats via the Illegal Command (ILL COMM) input (see figure 23 on page 36).

The RTI will internally decode the following mode codes as illegal:

- Dynamic Bus Control

- Selected Transmitter Shutdown

- Override Selected Transmitter Shutdown

- All Reserved Mode Codes

If the RTI receives one of the above mode codes, the RTI responds by transmitting a status word with the Message Error bit set to logic one.

Mode codes which involve data transfer are processed like receive and transmit commands. The RTI will not generate DMA request for Transmit Status Word and Transmit Last Command mode codes since the information is stored internal to the RTI.

The following mode codes require assistance from the host:

- Synchronize

- Initiate Self-Test

- Reset Remote Terminal

For example, the RTI will accept and respond to a Reset Remote Terminal mode code; however it will not perform a reset operation. The host must interpret the mode code and take appropriate action.

The RTI does not define or interpret the following data words associated with mode code commands:

- Transmit Vector Word

- Synchronize With Data Word

- Transmit Bit Word

The RTI will accept and respond to mode code with data; the host must interpret or define the data word. The RTI will store or retrieve the data required for mode code command from block #1 of the receive or transmit page

## RTI MODE CODE HANDLING PROCEDURE

| T/R | Mode Code | Function                                               | Operation                                                                                                                                                  |  |  |  |

|-----|-----------|--------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 0   | 10100     | Selected Transmitter Shutdown <sup>2</sup>             | <ol> <li>Command word stored</li> <li>MES ERR pin asserted</li> <li>Message error latch set in System Register</li> <li>Status word transmitted</li> </ol> |  |  |  |

| 0   | 10101     | Override Selected Transmitter<br>Shutdown <sup>2</sup> | Command word stored     MES ERR pin asserted     Message error latch set in System Register     Status word transmitted                                    |  |  |  |

| 0   | 10001     | Synchronize (w/data)                                   | Command word stored     Data word stored     Status word transmitted                                                                                       |  |  |  |

| 1   | 00000     | Dynamic Bus Control <sup>2</sup>                       | Command word stored     MES ERR pin asserted     Message error latch set in System Register     Status word transmitted                                    |  |  |  |

| 1   | 00001     | Synchronize <sup>1</sup>                               | Command word stored     Status word transmitted                                                                                                            |  |  |  |

| 1   | 00010     | Transmit Status Word <sup>3</sup>                      | Command word stored     Status word transmitted                                                                                                            |  |  |  |

| 1   | 00011     | Initiate Self-Test <sup>1</sup>                        | Command word stored     Status word transmitted                                                                                                            |  |  |  |

| 1   | 00100     | Transmitter Shutdown                                   | Command word stored     Alternate bus shutdown     Status word transmitted                                                                                 |  |  |  |

| 1   | 00101     | Override Transmitter Shutdown                          | Command word stored     Alternate bus enabled     Status word transmitted                                                                                  |  |  |  |

| 1   | 00110     | Inhibit Terminal Flag Bit                              | Command word stored     Terminal Flag bit set to zero and disabled     Status word transmitted                                                             |  |  |  |

| 1   | 00111     | Override Inhibit Terminal Flag Bit                     | Command word stored Bit     Terminal Flag bit enabled, but not set to logic one     Status word transmitted                                                |  |  |  |

| 1   | 01000     | Reset Remote Terminal <sup>1</sup>                     | Command word stored     Status word transmitted                                                                                                            |  |  |  |

| 1   | 10010     | Transmit Last Command Word <sup>3</sup>                | Status word transmitted     Last command word transmitted                                                                                                  |  |  |  |

| 1   | 10000     | Transmit Vector Word                                   | Command word stored     Status word transmitted     Data word transmitted                                                                                  |  |  |  |

| 1   | 10011     | Transmit BIT Word                                      | Command word stored     Status word transmitted     Data word transmitted                                                                                  |  |  |  |

- 1. Further host interaction required for mode code operation.

2. Reserved mode code; A) MES ERR pin asserted, B) Message Error bit set, C) status word transmitted (ME bit set to logic one).

- 3.Status word not affected.

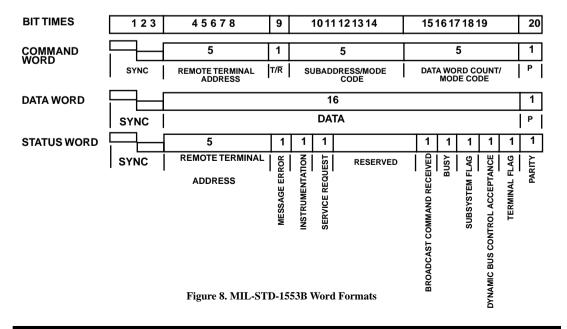

#### 1.4 MIL-STD-1553B Subaddress and Mode Code Definitions

Table 1. Subaddress and Mode Code Definitions Per MIL-STD-1553B

| Subaddress Field | Mess         | sage Format  |                     |

|------------------|--------------|--------------|---------------------|

| Binary (Decimal) | Receive      | Transmit     | Description         |

| 00000 (00)       | 1            | 1            | Mode Code Indicator |

| 00001 (01)       | User Defined | User Defined |                     |

| 00010 (02)       | User Defined | User Defined |                     |

| 00011 (03)       | User Defined | User Defined |                     |

| 00100 (04)       | User Defined | User Defined |                     |

| 00101 (05)       | User Defined | User Defined |                     |

| 00110 (06)       | User Defined | User Defined |                     |

| 00111 (07)       | User Defined | User Defined |                     |

| 01000 (08)       | User Defined | User Defined |                     |

| 01001 (09)       | User Defined | User Defined |                     |

| 01010 (10)       | User Defined | User Defined |                     |

| 01011 (11)       | User Defined | User Defined |                     |

| 01100 (12)       | User Defined | User Defined |                     |

| 01101 (13)       | User Defined | User Defined |                     |

| 01110 (14)       | User Defined | User Defined |                     |

| 01111 (15)       | User Defined | User Defined |                     |

| 10000 (16)       | User Defined | User Defined |                     |

| 10001 (17)       | User Defined | User Defined |                     |

| 10010 (18)       | User Defined | User Defined |                     |

| 10011 (19)       | User Defined | User Defined |                     |

| 10100 (20)       | User Defined | User Defined |                     |

| 10101 (21)       | User Defined | User Defined |                     |

| 10110 (22)       | User Defined | User Defined |                     |

| 10111 (23)       | User Defined | User Defined |                     |

| 11000 (24)       | User Defined | User Defined |                     |

| 11001 (25)       | User Defined | User Defined |                     |

| 11010 (26)       | User Defined | User Defined |                     |

| 11011 (27)       | User Defined | User Defined |                     |

| 11100 (28)       | User Defined | User Defined |                     |

| 11101 (29)       | User Defined | User Defined |                     |

| 11110 (30)       | User Defined | User Defined |                     |

| 11111 (31)       | 1            | 1            | Mode Code Indicator |

#### Note:

1. Refer to mode code assignments per MIL-STD-1553B

#### 1.5 Remote Terminal Address

Assign the RTI remote terminal address by either a software or hardware exercise. The host assigns the RTI remote terminal address by performing a Control Register write; the Terminal Address bus (TA(4:0)) is strobed into the RTI Remote Terminal Address Register upon completion of the Control Register write. To assign the RTI remote terminal address via hardware, use the TALEN/PARITY input pin operating in the terminal latch address enable mode. The Terminal Address bus is latched into the RTI while the TALEN is asserted (i.e., logic low). Valid remote terminal addresses (RTA) include decimal 0 through 31 if Broadcast is disabled, 0 through 30 if Broadcast is enabled

#### **Parity Checker**

An address parity check is performed to insure the remote terminal address applied to TA(4:0) was properly latched into the Remote Terminal Address Register. To perform a parity check, enable the RTI parity circuit via EXT TEST and EXT TST CH SEL  $A/\overline{B}$  input pins. The parity bit is entered through the  $\overline{TALEN}/PARITY$  input pin operating in the parity mode. Input pins EXT TEST and EXT TST CH SEL  $A/\overline{B}$  control dual-function input pin  $\overline{TALEN}/PARITY$ ; see table 2 for description of operation.

If a parity error exists, the Parity Error bit of the System Register is set to a logic one, biphase Channels A and B are disabled (set to logic zero), the Message Error bit set to logic one, and the message error pin is asserted. Table 2. Parity Checking

| STATE # | EXT TEST | EXT TST CH SEL A/B | Function of TALEN/PARITY                                                                                                                                         |

|---------|----------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0       | 0        | 0                  | Terminal Address Latch Enable. Active low signal used to latch TA(4:0) into RTI. Internal parity checker disabled.                                               |

| 1       | 0        | 1                  | Parity. Internal remote terminal address parity checker enabled. TALEN/PARITY pin functions as parity bit for TA(4:0) bus. Proper operation requires odd parity. |

| 2       | 1        | 0                  | Terminal Address Latch Enable. Do not assert EXT TST during reset, otherwise self-test is invoked.                                                               |

| 3       | 1        | 1                  | Terminal Address Latch Enable. Do not assert EXT TST during reset, otherwise self-test is invoked.                                                               |

The following are examples of sequences used to enter remote terminal addresses into the RTI.

Example 1. Hardware-Controlled Remote Terminal Address (parity check disabled): STATE 0, 2, or 3 (i.e., 00, 10, or 11)

TALEN - asserted (i.e., logic low) TA(4:0) - valid RTA

Example 2. Software-Controlled Remote Terminal Address (parity check disabled):

> EXT TEST and EXT TST CH SEL  $A/\overline{B}$ in STATE 0, 2, or 3 (i.e., 00, 10, or 11) CTRL - logic zero CS - logic zero RD/WR - logic zero ADDR IN (0) - logic zero TALEN - logic one

TA(4:0) - valid RTA Example 3. Software Controlled Remote Terminal Address (parity check enabled):

> EXT TEST and EXT TST CH SEL  $A/\overline{B}$ in STATE 1 (i.e., 01) CTRL - logic zero CS - logic zero RD/WR - logic zero ADDR IN (0) - logic zero PARITY - input must provide odd

parity

for the TA(4:0) bus TA(4:0) - valid RTA

For examples 1 and 2, enabling the parity check circuit (STATE 1) after the remote terminal address is stored results in a parity check of the data loaded into the Remote Terminal Address Register.

#### 1.6 Internal Self-Test

Setting bit 6 of the Control Register to a logic one enables the internal self-test. Disable Channels A and B at this time to prevent bus activity during self-test by setting bits 0 and 1 of the Control Register to a logic zero. Normal operation is inhibited when internal self-test is enabled. The RTI's self-test capability is based on the fact that the MIL-STD-1553B status word sync pulse is identical to the command word sync pulse. Thus, if the status word from the encoder is fed back to the decoder, the RTI will recognize the incoming status word as a command word and thus cause the RTI to transmit another status word. After the host invokes self-test, the RTI self-test logic forces a status word transmission even though the RTI has not received a command word. The status word is sent to decoder A or B depending on the channel the host selected for self-test. The host controls the self-test by periodically changing the bit patterns in the status word being transmitted. Writing to the Control Register bits 2, 3, 4, and 8 changes the status word. Monitor the self-test by sampling either the System Register or the external status pins (i.e. Command Strobe  $(\overline{\text{COMSTR}})$ , Transmit  $(\overline{\text{XMIT}})$ , Receive  $(\overline{\text{RCV}})$ ). For a more detailed explanation of internal self-test, consult the UTMC publication RTI Internal Self-Test Routine.

#### 1.7 Power-up Master Reset

Reset the RTI by invoking either a hardware or software master reset after power-up to place the device in a known state. The master reset clears the decoder and encoder registers, the command recognition logic, the control and error logic (which includes the Status, Control and System Registers), the data transfer logic, and the memory address control logic. After reset, configure the device for operation via a Control Register write.

Perform a hardware reset by asserting the MRST input pin for a minimum of 500ns. During reset negate the EXT TEST pin (i.e., logic low); assertion of the EXT TEST pin forces the RTI to enter the external self-test mode of operation.

Software reset the RTI by simultaneously applying a logic zero to input pins  $\overline{CS}$ ,  $RD/\overline{WR}$ , and  $\overline{CTRL}$  while the least significant bit of the address input bus is a logic one (ADDR IN (0)=0).

#### 1.8 Encoder and Decoder

The RTI interfaces directly to a bus transmitter/receiver via the RTI Manchester II encoder/decoder. The UT1553B RTI receives the command word from the MIL-STD-1553B bus and processes it either by the primary or secondary decoder. Each decode checks for the proper sync pulse and Manchester waveform, edge skew, correct number of bits, and parity. If the command is a receive command, the RTI processes each incoming data word for correct word count and contiguous data. If an invalid message error is detected, the message error pin is asserted, the RTI ceases processing the remainder (if any) of the message, and it then suppresses status word transmission. Upon command validation recognition, the external status outputs are enabled. Reception of illegal commands does not suppress status word transmission.

A timer precludes transmission greater than 730ms by the assertion of fail-safe timer (TIMERON). This timer is reset upon receipt of another valid command.

#### 1.9 Illegal Command Decoding

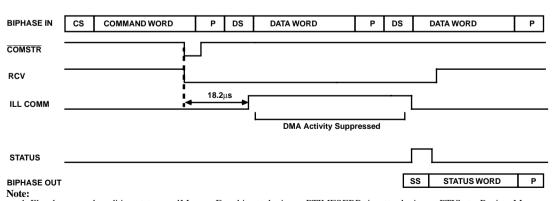

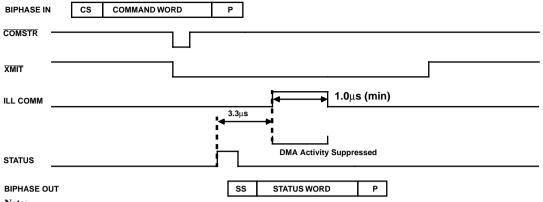

The host has the option of asserting the ILL COMM pin to illegalize a received command word. On receipt of an illegal command, the RTI sets the message error bit in the status

word, sets the Message Error output, and sets the message error latch in the System Register.

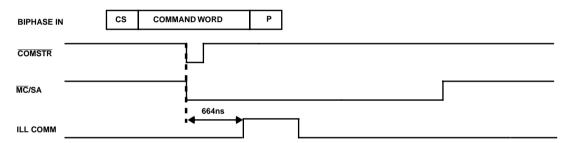

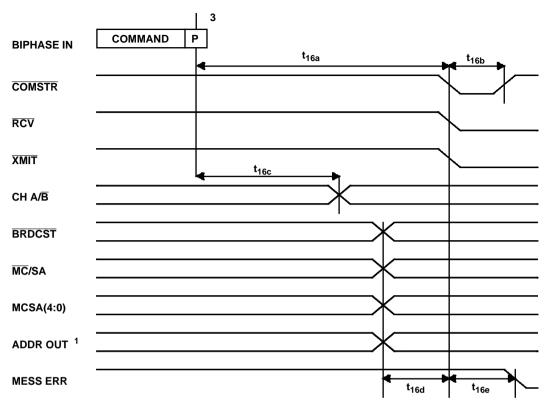

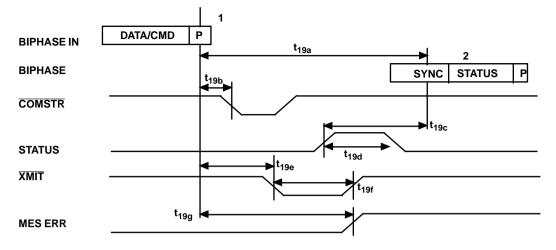

Use the following RTI outputs to externally decode an illegal command, Mode Code or Subaddress indicator ( $\overline{MC}$ /SA), Mode Code or Subaddress bus MCSA(4:0), Command Strobe ( $\overline{COMSTR}$ ), Broadcast ( $\overline{BRDCST}$ ), etc. (See figure 6 pages 11-12).

To illegalize a transmit command the ILL COMM pin is asserted 3.3ms after STATUS goes to a logic one. Assertion of the ILL COMM pin within 3.3ms allows the RTI to respond with the Message Error bit of the outgoing status word at a logic one.

For an illegal receive command, the ILL COMM pin is asserted within 18.2ms after the COMSTR transitions to a logic zero in order to suppress data words from being stored (suppress DMARQ assertions). In addition, the ILL COMM pin must be at a logic one throughout the reception of the message until STATUS is asserted.

If the illegal command is mode code 2, 4, 5, 6, 7, or 18, assert the ILL COMM pin within 664ns after Command Strobe ( $\overline{\text{COMSTR}}$ ) transitions to logic zero. Asserting the ILL COMM pin within the 664 nanoseconds inhibits the mode code function.

The above timing conditions also apply when the host externally decodes an illegal broadcast command. The host must remove the illegal command condition so that the next command is not falsely decoded as illegal. These requirements are easily met if the COMSTR output is used to qualify the ILL COMM input to the RTI.

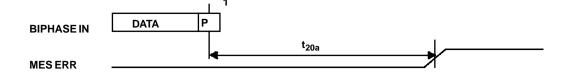

$1. \ Illegal command condition; status word Message Error bit set to logic one, RTIMES ERR pin set to a logic one, RTIS tatus Register Message Error bit set to logic one. \\$

Figure 6a. Illegal Receive Command Decoding

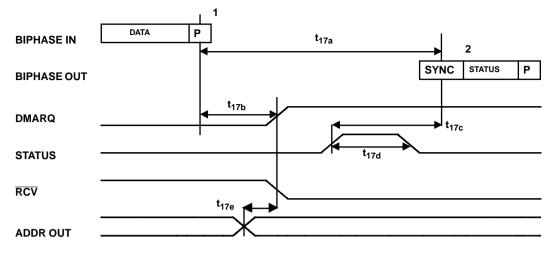

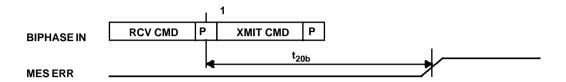

1. Illegal command condition: status word Message Error bit set to logic one, RTI MES ERR pin set to a logic one, RTI Status Register Message Error bit set to logic one.

Figure 6b. Illegal Transmit Command Decoding

#### Note:

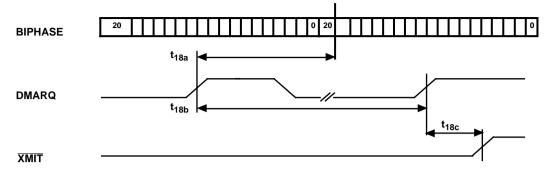

1. To illegalize mode codes 2, 4, 5, 6, 7, or 18 assert ILL COMM within 664ns of COMSTR's transition to logic zero. Asserting the ILL COMM within 664ns inhibits the mode code function

Figure 6c. Mode Code Command Decoding

#### 2.0 MEMORY MAP EXAMPLE

The RTI is capable of addressing 2048 x 16 of external memory for message storage. The 2K memory space is divided into two 1K pages and subdivided into 32 blocks of 32 x 16:

Page 1 (Receive): 32 blocks for receive messages (32 x 16)

Page 2 (Transmit): 32 blocks for transmit messages  $(32 \times 16)$

#### Address Decode

The RTI derives addresses (i.e., data pointers) for external memory directly from the 11 least significant bits of the command word. The address data pointer corresponds to ADDR OUT (10:0) during RTI memory accesses.

$T/\overline{R} = ADDR OUT (10)$ SUBADDRESS/MODE = ADDR OUT (9:5) WORD COUNT/MODE CODE = ADDR OUT (4:0)

The  $T/\overline{R}$  bit of the command word becomes the most significant bit of the data pointer; the  $T/\overline{R}$  bit serves to divide the RAM into transmit and receive pages of 1K each. The 5-bit subaddress/mode field is used to select 1 of 32 possible message storage blocks within the transmit or receive message page. The 5-bit word count/mode code field acts as a data pointer to select one of 32 locations within the message storage block. Multiple word messages are stored from top to bottom within the message storage block.

For mode commands, the address data pointer always contains 00000 in the  $\overline{MC}/SA$  field, regardless of whether 00000 or 11111 was received. Forcing the mode code field to 00000 reserves the first message storage block on both pages (receive and transmit) for mode code messages that require data. The 5-bit mode code specifies which of the 32 locations within the message storage block to access.

For "wrap-around" applications (transmission of data previously received), force the RTI to store and receive messages on one memory page. To accomplish one-page

operation do not use the  $T/\overline{R}$  output pin. Eliminating the T/ $\overline{R}$  limits the RTI access to only one page and the RTI will not differentiate between receive and transmit pages.

### Table 3. RTI Memory Map

#### 1: Receive Memory Map

#### 2: Transmit Memory map

| Block # | Operation     | Address Field (hex) | Block # | Operation     | Address Field (hex) |

|---------|---------------|---------------------|---------|---------------|---------------------|

| 1       | Mode Code 1   | 000 to 01F          | 1       | Mode Code 1   | 400 to 41F          |

| 2       | Subaddress 1  | 020 to 03F          | 2       | Subaddress 1  | 420 to 43F          |

| 3       | Subaddress 2  | 040 to 05F          | 3       | Subaddress 2  | 440 to 45F          |

| 4       | Subaddress 3  | 060 to 07F          | 4       | Subaddress 3  | 460 to 47F          |

| 5       | Subaddress 4  | 080 to 09F          | 5       | Subaddress 4  | 480 to 49F          |

| 6       | Subaddress 5  | 0A0 to 0BF          | 6       | Subaddress 5  | 4A0 to 4BF          |

| 7       | Subaddress 6  | 0C0 to 0DF          | 7       | Subaddress 6  | 4C0 to 4DF          |

| 8       | Subaddress 7  | 0E0 to 0FF          | 8       | Subaddress 7  | 4E0 to 4FF          |

| 9       | Subaddress 8  | 100 to 11F          | 9       | Subaddress 8  | 500 to 51F          |

| 10      | Subaddress 9  | 120 to 13F          | 10      | Subaddress 9  | 520 to 53F          |

| 11      | Subaddress 10 | 140 to 15F          | 11      | Subaddress 10 | 540 to 55F          |

| 12      | Subaddress 11 | 160 to 17F          | 12      | Subaddress 11 | 560 to 57F          |

| 13      | Subaddress 12 | 180 to 19F          | 13      | Subaddress 12 | 580 to 59F          |

| 14      | Subaddress 13 | 1A0 to 1BF          | 14      | Subaddress 13 | 5A0 to 5BF          |

| 15      | Subaddress 14 | 1C0 to 1DF          | 15      | Subaddress 14 | 5C0 to 5DF          |

| 16      | Subaddress 15 | 1E0 to 1FF          | 16      | Subaddress 15 | 5E0 to 5FF          |

| 17      | Subaddress 16 | 200 to 21F          | 17      | Subaddress 16 | 600 to 61F          |

| 18      | Subaddress 17 | 220 to 23F          | 18      | Subaddress 17 | 620 to 63F          |

| 19      | Subaddress 18 | 240 to 25F          | 19      | Subaddress 18 | 640 to 65F          |

| 20      | Subaddress 19 | 260 to 27F          | 20      | Subaddress 19 | 660 to 67F          |

| 21      | Subaddress 20 | 280 to 29F          | 21      | Subaddress 20 | 680 to 69F          |

| 22      | Subaddress 21 | 2A0 to 2BF          | 22      | Subaddress 21 | 6A0 to 6BF          |

| 23      | Subaddress 22 | 2C0 to 2DF          | 23      | Subaddress 22 | 6C0 to 6DF          |

| 24      | Subaddress 23 | 2E0 to 2FF          | 24      | Subaddress 23 | 6E0 to 6FF          |

| 25      | Subaddress 24 | 300 to 31F          | 25      | Subaddress 24 | 700 to 71F          |

| 26      | Subaddress 25 | 320 to 33F          | 26      | Subaddress 25 | 720 to 73F          |

| 27      | Subaddress 26 | 340 to 35F          | 27      | Subaddress 26 | 740 to 75F          |

| 28      | Subaddress 27 | 360 to 37F          | 28      | Subaddress 27 | 760 to 77F          |

| 29      | Subaddress 28 | 380 to 39F          | 29      | Subaddress 28 | 780 to 79F          |

| 30      | Subaddress 29 | 3A0 to 3BF          | 30      | Subaddress 29 | 7A0 to 7BF          |

| 31      | Subaddress 30 | 3C0 to 3DF          | 31      | Subaddress 30 | 7C0 to 7DF          |

| 32      | Unused        | 3E0 to 3FF          | 32      | Unused        | 7E0 to 7FF          |

- 1. Receive mode codes with data:

- Synchronize with data

Selected Transmitter Shutdown (Illegal)

Override Selected Transmitter Shutdown (Illegal)

2. Transmit mode codes with data:

- - Transmit Vector Word Transmit Bit Word

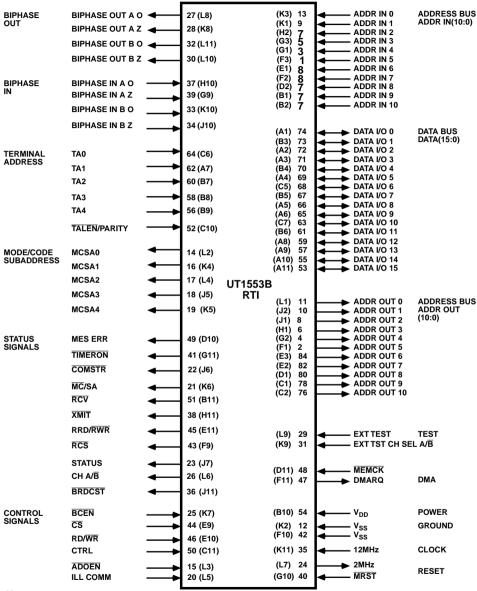

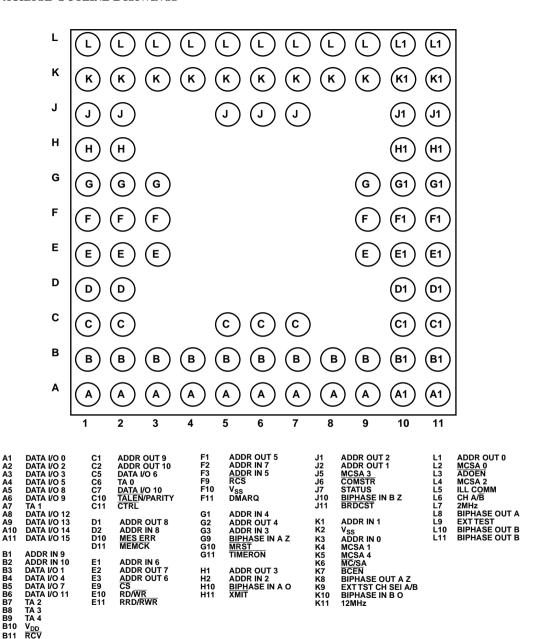

#### 3.0 PIN IDENTIFICATION AND DESCRIPTION

Note:

Pingrid array numbers are in parentheses. LCC pin numbers are not in parentheses.

Figure 7. UT1553B RTI Pin Description

## Legend for TYPE and ACTIVE fields:

TI = TTL input

TUI = TTL input (pull-up)

TDI = TTL input (pull-down)

TO = TTL output TTO = Three-state TTL output

TTB = Three-state TTL bidirectional

[] - Values in parentheses indicate the initialized state of output pin.

## **DATA BUS**

|             | PIN NU | JMBER | TYPE | ACTIVE |                                             |

|-------------|--------|-------|------|--------|---------------------------------------------|

| NAME        | LCC    | PGA   |      |        | DESCRIPTION                                 |

| DATA I/O 15 | 53     | A11   | TTB  |        | Bit 15 (MSB) of the bidirectional Data bus. |

| DATA I/O 14 | 55     | A10   | TTB  |        | Bit 14 of the bidirectional Data bus.       |

| DATA I/O 13 | 57     | A9    | TTB  |        | Bit 13 of the bidirectional Data bus.       |

| DATA I/O 12 | 59     | A8    | TTB  |        | Bit 12 of the bidirectional Data bus.       |

| DATA I/O 11 | 61     | В6    | TTB  |        | Bit 11 of the bidirectional Data bus.       |

| DATA I/O 10 | 63     | C7    | TTB  |        | Bit 10 of the bidirectional Data bus.       |

| DATA I/O 9  | 65     | A6    | TTB  |        | Bit 9 of the bidirectional Data bus.        |

| DATA I/O 8  | 66     | A5    | TTB  |        | Bit 8 of the bidirectional Data bus.        |

| DATA I/O 7  | 67     | B5    | TTB  |        | Bit 7 of the bidirectional Data bus.        |

| DATA I/O 6  | 68     | C5    | TTB  |        | Bit 6 of the bidirectional Data bus.        |

| DATA I/O 5  | 69     | A4    | TTB  |        | Bit 5 of the bidirectional Data bus.        |

| DATA I/O 4  | 70     | B4    | TTB  |        | Bit 4 of the bidirectional Data bus.        |

| DATA I/O 3  | 71     | A3    | TTB  |        | Bit 3 of the bidirectional Data bus.        |

| DATA I/O 2  | 72     | A2    | TTB  |        | Bit 2 of the bidirectional Data bus.        |

| DATA I/O 1  | 73     | В3    | TTB  |        | Bit 1 of the bidirectional Data bus.        |

| DATA I/O 0  | 74     | A1    | TTB  |        | Bit 0 (LSB) of the bidirectional Data bus.  |

## INPUT ADDRESS BUS

|            | PIN NU | UMBER | TYPE | ACTIVE |                                        |  |

|------------|--------|-------|------|--------|----------------------------------------|--|

| NAME       | LCC    | PGA   |      |        | DESCRIPTION                            |  |

| ADDR IN 10 | 75     | B2    | TI   |        | Bit 10 (MSB) of the Address Input bus. |  |

| ADDR IN 9  | 77     | B1    | TI   |        | Bit 9 of the Address Input bus.        |  |

| ADDR IN 8  | 79     | D2    | TI   |        | Bit 8 of the Address Input bus.        |  |

| ADDR IN 7  | 81     | F2    | TI   |        | Bit 7 of the Address Input bus.        |  |

| ADDR IN 6  | 83     | E1    | TI   |        | Bit 6 of the Address Input bus.        |  |

| ADDR IN 5  | 1      | F3    | TI   |        | Bit 5 of the Address Input bus.        |  |

| ADDR IN 4  | 3      | G1    | TI   |        | Bit 4 of the Address Input bus.        |  |

| ADDR IN 3  | 5      | G3    | TI   |        | Bit 3 of the Address Input bus.        |  |

| ADDR IN 2  | 7      | H2    | TI   |        | Bit 2 of the Address Input bus.        |  |

| ADDR IN 1  | 9      | K1    | TI   |        | Bit 1 of the Address Input bus.        |  |

| ADDR IN 0  | 13     | К3    | TI   |        | Bit 0 (LSB) of the Address Input bus.  |  |

## **OUTPUT ADDRESS BUS**

|             | PIN NUMBER |     | TYPE | ACTIVE |                                         |  |

|-------------|------------|-----|------|--------|-----------------------------------------|--|

| NAME        | LCC        | PGA |      |        | DESCRIPTION                             |  |

| ADDR OUT 10 | 76         | C2  | TTO  |        | Bit 10 (MSB) of the Address Output bus. |  |

| ADDR OUT 9  | 78         | C1  | TTO  |        | Bit 9 of the Address Output bus.        |  |

| ADDR OUT 8  | 80         | D1  | TTO  |        | Bit 8 of the Address Output bus.        |  |

| ADDR OUT 7  | 82         | E2  | TTO  |        | Bit 7 of the Address Output bus.        |  |

| ADDR OUT 6  | 84         | E3  | TTO  |        | Bit 6 of the Address Output bus.        |  |

| ADDR OUT 5  | 2          | F1  | TTO  |        | Bit 5 of the Address Output bus.        |  |

| ADDR OUT 4  | 4          | G2  | TTO  |        | Bit 4 of the Address Output bus.        |  |

| ADDR OUT 3  | 6          | H1  | TTO  |        | Bit 3 of the Address Output bus.        |  |

| ADDR OUT 2  | 8          | J1  | TTO  |        | Bit 2 of the Address Output bus.        |  |

| ADDR OUT 1  | 10         | J2  | TTO  |        | Bit 1 of the Address Output bus.        |  |

| ADDR OUT 0  | 11         | L1  | TTO  |        | Bit 0 (LSB) of the Address Output bus.  |  |

## REMOTE TERMINAL ADDRESS INPUTS

|              | PIN NU | JMBER | TYPE | ACTIVE |                                                                                                                                                                                                                                                                                                                                                                                                         |

|--------------|--------|-------|------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME         | LCC    | PGA   |      |        | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                             |

| TA4          | 56     | В9    | TUI  |        | Remote Terminal Address bit 4 (MSB).                                                                                                                                                                                                                                                                                                                                                                    |

| TA3          | 58     | В8    | TUI  |        | Remote Terminal Address bit 3.                                                                                                                                                                                                                                                                                                                                                                          |

| TA2          | 60     | В7    | TUI  |        | Remote Terminal Address bit 2.                                                                                                                                                                                                                                                                                                                                                                          |

| TA1          | 62     | A7    | TUI  |        | Remote Terminal Address bit 1.                                                                                                                                                                                                                                                                                                                                                                          |

| TA0          | C6     | 64    | TUI  |        | Remote Terminal Address bit 0.                                                                                                                                                                                                                                                                                                                                                                          |

| TALEN/PARITY | 52     | C10   | TUI  |        | Remote Terminal Address Latch Enable/ Remote Terminal Parity Input. Function of input is defined by he state of pin EXT TEST and EXT TST CH SEL A/B. For EXT TEST = 0, EXT TST CH SEL A/B = 1, TALEN/PARITY must provide odd parity for the Remote Terminal Address. For all other states of EXT TEST and EXT TST CH SEL A/B (i.e., 00, 10, 11) TALEN/PARITY functions as an active low address strobe. |

;

MODE CODE/SUBADDRESS OUTPUTS

ACTIVE

|          | PIN NU | MBER | TYPE | ACTIVE |                                                                                                                                                                                                                                                                                                                                                                   |

|----------|--------|------|------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME     | LCC    | PGA  | -    |        | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                       |

| MC/SA    | 21     | K6   | ТО   |        | Mode Code/Subaddress Indicator. If \overline{MC}/SA is low, it indicates that the most recent command word is a mode code command. If \overline{MC}/SA is high, it indicates that the most recent command word is for a subaddress. This output indicates whether the mode code/subaddress outputs (i.e., MCSA(4:0)) contain mode code or subaddress information. |

| MCSA4 19 | K5     | ТО   |      |        | Mode Code/Subaddress 4. If $\overline{MC}$ /SA is low, this pin represents the most significant bit of the the most recent command word (the MSB of the mode code). If $\overline{MC}$ /SA is high, this pin represents the MSB of the subaddress.                                                                                                                |

| MCSA3 18 | J5     | TO   |      |        | Mode Code/Subaddress 3.                                                                                                                                                                                                                                                                                                                                           |

| MCSA2 17 | L4     | TO   |      |        | Mode Code/Subaddress 2.                                                                                                                                                                                                                                                                                                                                           |

| MCSA1 16 | K4     | TO   |      |        | Mode Code/Subaddress 1.                                                                                                                                                                                                                                                                                                                                           |

| MCSA0 14 | L2     | ТО   |      |        | Mode Code/Subaddress 0. If MC/SA is low, this pin represents the least significant bit of the the most recent command word. If MC/SA is high, this pin represents the LSB of the subaddress                                                                                                                                                                       |

## **BIPHASE INPUTS**

|                | PIN NU | JMBER |    |  |                                                                                               |

|----------------|--------|-------|----|--|-----------------------------------------------------------------------------------------------|

| NAME           | LCC    | PGA   |    |  | DESCRIPTION                                                                                   |

| BIPHASE IN A Z | 39     | G9    | TI |  | Receiver - Channel A, Zero Input. Idle low<br>Manchester input from the 1553 bus transceiver. |

| BIPHASE IN A O | 37     | H10   | TI |  | Receiver - Channel A, One Input. This input is the complement of BIPHASE IN A Z.              |

| BIPHASE IN B Z | 34     | J10   | TI |  | Receiver - Channel B, Zero Input. Idle low<br>Manchester input from the 1553 bus transceiver. |

| BIPHASE IN B O | 33     | K10   | TI |  | Receiver - Channel B, One Input. This input is the complement of BIPHASE IN B Z.              |

## **BIPHASE OUTPUTS**

|                 | PIN NU | JMBER |      | A COMPANIE |                                                                                                                                                   |

|-----------------|--------|-------|------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME            | LCC    | PGA   | TYPE | ACTIVE     | DESCRIPTION                                                                                                                                       |

| BIPHASE OUT A Z | 28     | K8    | ТО   |            | Transmitter - Channel A, Zero Output. This Manchester-encoded data output is connected to the 1553 bus transmitter input. The output is idle low. |

| BIPHASE OUT A O | 27     | L8    | ТО   |            | Transmitter - Channel A, One Output. This output is the complement of BIPHASE OUT A Z. The output is idle low.                                    |

| BIPHASE OUT B Z | 30     | L10   | ТО   |            | Transmitter - Channel B, Zero Output. This Manchester-encoded data output is connected to the 1553 bus transmitter. The output is idle low.       |

| BIPHASE OUT B O | 32     | L11   | ТО   |            | Transmitter - Channel B, One Output. This output is the complement of BIPHASE OUT B Z. The output is idle low.                                    |

## MASTER RESET AND CLOCK

| NAME  |     | MBER | ТҮРЕ | ACTIVE | DESCRIPTION                                                                                                                                      |

|-------|-----|------|------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME  | LCC | PGA  | TIFE | ACTIVE | DESCRIPTION                                                                                                                                      |

| MRST  | 40  | G10  | TUI  | AL     | Master Reset. Initializes all internal functions of the RTI. MRST must be asserted 500 nanoseconds before normal RTI operation. (500ns minimum). |

| 12MHz | 35  | K11  | TI   |        | 12MHz Input Clock. This is the RTI system clock that requires an accuracy greater than 0.01% with a duty cycle from 50% ±10%.                    |

| 2MHz  | 24  | L7   | ТО   |        | 2MHz Clock Output. This is a 2MHz output generated by the 12MHz input clock. This clock is stopped when MRST is low.                             |

## POWER AND GROUND

|                 | PIN NUMBER |     |      |        |                                                         |

|-----------------|------------|-----|------|--------|---------------------------------------------------------|

| NAME            | LCC        | PGA | TYPE | ACTIVE | DESCRIPTION                                             |

| V <sub>DD</sub> | 54         | B10 | PWR  |        | $+5V_{DC}$ . Power supply must be $+5V_{DC} \pm 10\%$ . |

| V <sub>SS</sub> | 12         | K2  | GND  |        | Ground reference. Zero V <sub>DC</sub> logic ground.    |

|                 | 42         | F10 | GND  |        |                                                         |

## **CONTROL PINS**

|          | PIN NUMBER |     | TYPE | ACTIVE |                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------|------------|-----|------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME     | LCC        | PGA |      |        | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                 |

| CS       | 44         | E9  | TI   | AL     | Chip Select. Active low input for host access of transparent memory or the RTI internal registers. In the transparent memory configuration $\overline{\text{CS}}$ is propagated through the RTI to the $\overline{\text{RCS}}$ output.                                                                                                                                                                                      |

| CTRL     | 50         | C11 | TI   | AL     | Control. The host processor uses the active low CTRL input signal in conjunction with CS and RD/WR to access the RTI internal registers. CTRL is also used in the software assignment of the terminal address and programmed reset.                                                                                                                                                                                         |

| ADOEN    | 15         | L3  | TI   | AL     | Address Output Enable. When ADOEN is low the Address Out bus (ADDR OUT (15:0)) is active. If ADOEN = 1 the Address Out bus is high impedance.                                                                                                                                                                                                                                                                               |

| RD/WR    | 46         | E10 | TI   |        | Read/Write. The host processor uses a high level on this input in conjunction with $\overline{CS}$ and $\overline{CTRL}$ to read the RTI internal registers. A low level on this input is used in conjunction with $\overline{CS}$ and $\overline{CTRL}$ to write to internal RTI registers. In the transparent memory configuration RD/ $\overline{WR}$ is propagated through the RTI to the RRD/ $\overline{RWR}$ output. |

| BCEN     | 25         | K7  | TUI  | AL     | Broadcast Enable. Active low input enables broadcast commands.                                                                                                                                                                                                                                                                                                                                                              |

| ILL COMM | 20         | L5  | TDI  | АН     | Illegal Command. The host processor uses the ILL COMM input to inform the RTI that the present command is illegal. ILL COMM is used in conjunction with MCSA(4:0) and MC/SA to define system dependent illegal commands.                                                                                                                                                                                                    |

## STATUS OUTPUTS

|         | PIN N | PIN NUMBER |    | ACTIVE |                                                                                                                                                                                                                                                                                                                                                           |

|---------|-------|------------|----|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME    | LCC   | PGA        |    |        | DESCRIPTION                                                                                                                                                                                                                                                                                                                                               |

| RCS     | 43    | F9         | TO | AL     | RAM Chip Select. Active low output used to enable memory for access.                                                                                                                                                                                                                                                                                      |

| RRD/RWR | 45    | E11        | ТО |        | RAM Read/Write. High output enables memory read, low output enables memory write, used in conjunction with $\overline{RCS}$ ). Normally high output.                                                                                                                                                                                                      |

| COMSTR  | 22    | J6         | ТО | AL     | Command Strobe. COMSTR is an active low output of 500ns duration identifying receipt of a valid command.                                                                                                                                                                                                                                                  |

| TIMERON | 41    | G11        | ТО | AL     | Fail-safe Timer. The TIMERON output pulses low for 730ms when the RTI begins transmitting (i.e., rising edge of STATUS) to provide a fail-safe timer meeting the requirements of MIL-STD-1553B. This pulse is reset when COMSTR goes low or during Master Reset. in the external self-test mode TIMERON does not recognize COMSTR and resets after 730ms. |

| MES ERR | 49    | D10        | ТО | АН     | Message Error. The active high MES ERR output signals that the Message Error bit in the Status Register has been set due to receipt of an invalid command or an error during message sequence. MES ERR will reset to logic zero on receipt of next valid command.                                                                                         |

| CH A/B  | 26    | L6         | ТО |        | Channel A/ $\overline{B}$ . Output identifying the channel on which the most recent valid command was received. Channel A = 1, Channel B = 0.                                                                                                                                                                                                             |

| XMIT    | 38    | H11        | ТО | AL     | Transmit. Active low output identifies a transmit command message transfer by the RTI is in progress.                                                                                                                                                                                                                                                     |

| RCV     | 51    | B11        | ТО | AL     | Receive. Active low output identifies a receive command message transfer by the RTI is in progress.                                                                                                                                                                                                                                                       |

| BRDCST  | 36    | J11        | ТО | AL     | Broadcast. BRDCST is an active low output that identifies receipt of a valid broadcast command.                                                                                                                                                                                                                                                           |

| STATUS  | 23    | J7         | ТО | АН     | Status. Active high output pulse indicating that the RTI is in the process of transmitting a status word.                                                                                                                                                                                                                                                 |

### **BUS ARBITRATION**

|                       | PIN NU | JMBER | TYPE | ACTIVE |                                                                                                                                                                                                                                                                                                            |

|-----------------------|--------|-------|------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                  | LCC    | PGA   |      |        | DESCRIPTION                                                                                                                                                                                                                                                                                                |

| DMARQ                 | 47     | F11   | ТО   | AH     | Direct Memory Access Request. Active high output requesting RTI access to memory.                                                                                                                                                                                                                          |

| MEMCK                 | 48     | D11   | TI   | AL     | Memory Clock (DMA Grant). Active low input signaling the RTI that a memory access is granted. Internal to the RTI, receipt of MEMCK generates RAM chip select and RAM read/write signals.                                                                                                                  |

| EXT TST               | 29     | L9    | TDI  |        | External Self-test Enable. Multi-function input pin. In self-test mode forcing this pin high allows the monitoring of self-test activity at the bus stub. When the RTI is not in self-test this pin defines the function of TALEN/PARITY.                                                                  |

| EXT TST CH SEL<br>A/B | 31     | К9    | TUI  |        | External Self-test Channel Select. $A/\overline{B}$ Multifunction input pin. In self-test mode forcing this pin high selects the channel on which the self-test is performed (Channel A = 1, Channel B = 0). When the RTI is not in self-test this pin defines the function of $\overline{TALEN/PARITY}$ . |

## 4.0 OPERATING CONDITIONS

ABSOLUTE MAXIMUM RATINGS <sup>1</sup> (referenced to VSS)

| SYMBOL           | PARAMETER                            | LIMITS                       | UNIT |

|------------------|--------------------------------------|------------------------------|------|

| $V_{DD}$         | DC supply voltage                    | -0.3 to +7.0                 | V    |

| $V_{IO}$         | Voltage on any pin                   | -0.3 to V <sub>DD</sub> +0.3 | V    |

| $I_{\mathrm{I}}$ | DC input current                     | ±10                          | mA   |

| T <sub>STG</sub> | Storage temperature                  | -65 to +150                  | °C   |

| P <sub>D</sub>   | Maximum power dissipation            | 300                          | mW   |

| $T_{J}$          | Maximum junction temperature         | +175                         | °C   |

| $\Theta_{ m JC}$ | Thermal resistance, junction-to-case | 20                           | °C/W |

#### Note:

## **Recommended Operating Conditions**

| SYMBOL          | PARAMETER           | LIMITS               | UNIT |

|-----------------|---------------------|----------------------|------|

| $V_{DD}$        | DC supply voltage   | 4.5 to 5.5           | V    |

| V <sub>IN</sub> | DC input voltage    | 0 to V <sub>DD</sub> | V    |

| T <sub>C</sub>  | Temperature range   | -55 to +125          | °C   |

| F <sub>O</sub>  | Operating frequency | 12 ± .01%            | MHz  |

Stresses outside the listed absolute maximum ratings may cause permanent damage to the device. This is a stress rating only, and functional

operation of the device at these or any other conditions beyond limits indicated in the operational sections of this specification is not

recommended. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### 5.0 DC ELECTRICAL CHARACTERISTICS

$(VDD = 5.0V \pm 10\%; -55^{\circ}C < TC < +125^{\circ}C)$

| SYMBOL           | PARAMETER                                                                                      | CONDITION                                                                                                   | MINIMUM             | MAXIMUM            | UNIT           |

|------------------|------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|---------------------|--------------------|----------------|

| V <sub>IL</sub>  | Low-level input voltage                                                                        |                                                                                                             |                     | 0.8                | V              |

| V <sub>IH</sub>  | High-level input voltage                                                                       |                                                                                                             | 2.0                 |                    | V              |

| I <sub>IN</sub>  | Input leakage current TTL inputs Inputs with pull-down resistors Inputs with pull-up resistors | $\begin{aligned} &V_{IN} = V_{DD} \text{ or } V_{SS} \\ &V_{IN} = V_{DD} \\ &V_{IN} = V_{SS} \end{aligned}$ | -10<br>110<br>-2750 | 10<br>2750<br>-110 | μΑ<br>μΑ<br>μΑ |

| V <sub>OL</sub>  | Low-level output voltage                                                                       | $I_{OL} = 4mA$                                                                                              |                     | 0.4                | V              |