### USB251xB/xBi

# **USB 2.0 Hi-Speed Hub Controller**

#### PRODUCT FEATURES

**Datasheet**

#### **General Description**

The SMSC USB251xB/xBi hub is a family of low-power, configurable, MTT (multi transaction translator) hub controller IC products for embedded USB solutions. The x in the part number indicates the number of downstream ports available, while the B indicates battery charging support. The SMSC hub supports low-speed, full-speed, and hi-speed (if operating as a hi-speed hub) downstream devices on all of the enabled downstream ports.

#### **Highlights**

- High performance, low-power, small footprint hub controller IC with 2, 3, or 4 downstream ports

- Fully compliant with the USB 2.0 Specification [1]

- Enhanced OEM configuration options available through either a single serial I<sup>2</sup>C<sup>®</sup> EEPROM, or SMBus slave port

#### ■ MultiTRAK™

High-performance multiple transaction translator which provides one transaction translator per port

#### PortMap

Flexible port mapping and disable sequencing

#### PortSwap

Programmable USB differential-pair pin locations ease PCB design by aligning USB signal lines directly to connectors

#### PHYBoost

Programmable USB signal drive strength for recovering signal integrity using 4-level driving strength resolution

#### **Features**

- USB251xB/xBi products are fully footprint compatible with USB251x/xi/xA/xAi products as direct drop-in replacements

- Cost savings include using the same PCB components and application of USB-IF Compliance by Similarity

- Full power management with individual or ganged power control of each downstream port

- Fully integrated USB termination and pull-up/pulldown resistors

- Supports a single external 3.3 V supply source; internal regulators provide 1.2 V internal core voltage

- Onboard 24 MHz crystal driver or external 24 MHz clock input

- Customizable vendor ID, product ID, and device ID

- 4 kilovolts of HBM JESD22-A114F ESD protection (powered and unpowered)

- Supports self- or bus-powered operation

- Supports the USB Battery Charging specification Rev. 1.1 for Charging Downstream Ports (CDP)

- The USB251xB/xBi offers the following package:

36-pin QFN (6x6 mm) lead-free RoHS compliant

- package

- USB251xBi products support the industrial temperature range of -40°C to +85°C

- USB251xB products support the extended commercial temperature range of 0°C to +85°C

#### **Applications**

- LCD monitors and TVs

- Multi-function USB peripherals

- PC motherboards

- Set-top boxes, DVD players, DVR/PVR

- Printers and scanners

- PC media drive bay

- Portable hub boxes

- Mobile PC docking

- Embedded systems

#### **Order Numbers:**

| ORDER NUMBERS*                                     | LEAD-FREE<br>ROHS COMPLIANT<br>PACKAGE | PACKAGE<br>SIZE (MM) | TEMPERATURE<br>RANGE |

|----------------------------------------------------|----------------------------------------|----------------------|----------------------|

| USB2512B-AEZG<br>USB2513B-AEZC<br>USB2514B-AEZC    | 00.051                                 | 6x6x0.5              | 0°C to 85°C          |

| USB2512Bi-AEZG<br>USB2513Bi-AEZG<br>USB2514Bi-AEZG | 36-QFN                                 | OXOXU.3              | -40°C to 85°C        |

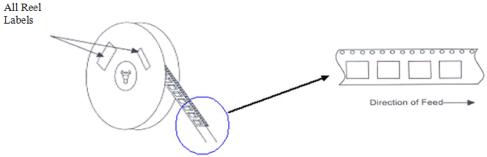

\* Add -TR to the end of any QFN order number to order tape and reel (36-pin packages only). Reel size is 3,000 pieces.

This product meets the halogen maximum concentration values per IEC61249-2-21 For RoHS compliance and environmental information, please visit www.smsc.com/rohs

Please contact your SMSC sales representative for additional documentation related to this product such as application notes, anomaly sheets, and design guidelines.

Copyright © 2012 SMSC or its subsidiaries. All rights reserved.

Circuit diagrams and other information relating to SMSC products are included as a means of illustrating typical applications. Consequently, complete information sufficient for construction purposes is not necessarily given. Although the information has been checked and is believed to be accurate, no responsibility is assumed for inaccuracies. SMSC reserves the right to make changes to specifications and product descriptions at any time without notice. Contact your local SMSC sales office to obtain the latest specifications before placing your product order. The provision of this information does not convey to the purchaser of the described semiconductor devices any licenses under any patent rights or other intellectual property rights of SMSC or others. All sales are expressly conditional on your agreement to the terms and conditions of the most recently dated version of SMSC's standard Terms of Sale Agreement dated before the date of your order (the "Terms of Sale Agreement"). The product may contain design defects or errors known as anomalies which may cause the product's functions to deviate from published specifications. Anomaly sheets are available upon request. SMSC products are not designed, intended, authorized or warranted for use in any life support or other application where product failure could cause or contribute to personal injury or severe property damage. Any and all such uses without prior written approval of an Officer of SMSC and further testing and/or modification will be fully at the risk of the customer. Copies of this document or other SMSC literature, as well as the Terms of Sale Agreement, may be obtained by visiting SMSC's website at http://www.smsc.com. SMSC is a registered trademark of Standard Microsystems Corporation ("SMSC"). Product names and company names are the trademarks of their respective holders.

SMSC DISCLAIMS AND EXCLUDES ANY AND ALL WARRANTIES, INCLUDING WITHOUT LIMITATION ANY AND ALL IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, TITLE, AND AGAINST INFRINGEMENT AND THE LIKE, AND ANY AND ALL WARRANTIES ARISING FROM ANY COURSE OF DEALING OR USAGE OF TRADE. IN NO EVENT SHALL SMSC BE LIABLE FOR ANY DIRECT, INCIDENTAL, INDIRECT, SPECIAL, PUNITIVE, OR CONSEQUENTIAL DAMAGES; OR FOR LOST DATA, PROFITS, SAVINGS OR REVENUES OF ANY KIND; REGARDLESS OF THE FORM OF ACTION, WHETHER BASED ON CONTRACT; TORT; NEGLIGENCE OF SMSC OR OTHERS; STRICT LIABILITY; BREACH OF WARRANTY; OR OTHERWISE; WHETHER OR NOT ANY REMEDY OF BUYER IS HELD TO HAVE FAILED OF ITS ESSENTIAL PURPOSE. AND WHETHER OR NOT SMSC HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

Datasheet

# **Conventions**

Within this manual, the following abbreviations and symbols are used to improve readability.

| Example                 | Description                                                                                                             |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------|

| BIT                     | Name of a single bit within a field                                                                                     |

| FIELD.BIT               | Name of a single bit (BIT) in FIELD                                                                                     |

| xy                      | Range from x to y, inclusive                                                                                            |

| BITS[m:n]               | Groups of bits from m to n, inclusive                                                                                   |

| PIN                     | Pin Name                                                                                                                |

| zzzzb                   | Binary number (value zzzz)                                                                                              |

| 0xzzz                   | Hexadecimal number (value zzz)                                                                                          |

| zzh                     | Hexadecimal number (value zz)                                                                                           |

| rsvd                    | Reserved memory location. Must write 0, read value indeterminate                                                        |

| code                    | Instruction code, or API function or parameter                                                                          |

| Section Name            | Section or Document name                                                                                                |

| Х                       | Don't care                                                                                                              |

| <parameter></parameter> | <> indicate a Parameter is optional or is only used under some conditions                                               |

| {,Parameter}            | Braces indicate Parameter(s) that repeat one or more times                                                              |

| [Parameter]             | Brackets indicate a nested Parameter. This Parameter is not real and actually decodes into one or more real parameters. |

# **Table of Contents**

| Chapter 1 Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| Chapter 2 Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 10             |

| Chapter 3 Pin Information.  3.1 Pin Configurations.  3.2 Pin List (Alphabetical).  3.3 Pin Descriptions (Grouped by Function).  3.3.1 Configuring the Strap Pins.  3.4 Buffer Type Descriptions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                |

| Chapter 4 Battery Charging Support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 24<br>24<br>25 |

| Chapter 5 Initial Interface/Configuration Options 5.1 Internal Register Set (Common to I <sup>2</sup> C EEPROM and SMBus) 5.1.1 Register 00h: Vendor ID (LSB) 5.1.2 Register 01h: Vendor ID (MSB) 5.1.3 Register 02h: Product ID (LSB) 5.1.4 Register 03h: Product ID (MSB) 5.1.5 Register 04h: Device ID (LSB) 5.1.6 Register 04h: Device ID (LSB) 5.1.7 Register 05h: Device ID (MSB) 5.1.7 Register 05h: CONFIG_BYTE_1 5.1.8 Register 07h: Configuration Data Byte 2 5.1.9 Register 08h: Configuration Data Byte 3 5.1.10 Register 09h: Non-Removable Device 5.1.11 Register 09h: Port Disable For Self-Powered Operation. 5.1.12 Register 0Bh: Port Disable For Bus-Powered Operation. 5.1.13 Register 0Ch: Max Power For Self-Powered Operation 5.1.14 Register 0Ch: Max Power For Bus-Powered Operation 5.1.15 Register 0Fh: Hub Controller Max Current For Self-Powered Operation 5.1.16 Register 0Fh: Hub Controller Max Current For Bus-Powered Operation 5.1.17 Register 10h: Power-On Time 5.1.18 Register 11h: Language ID High 5.1.19 Register 12h: Language ID Low 5.1.20 Register 13h: Manufacturer String Length 5.1.21 Register 14h: Product String Length 5.1.22 Register 15h: Serial String Length 5.1.23 Register 16h-53h: Manufacturer String 5.1.24 Register 56h: Boost Up |                |

| Appendix B (References)                                                                                                                                                                                                                                                                                                                                                                                                                                               | 62                                                                         |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                            |

| Appendix A (Acronyms)                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 61                                                                         |

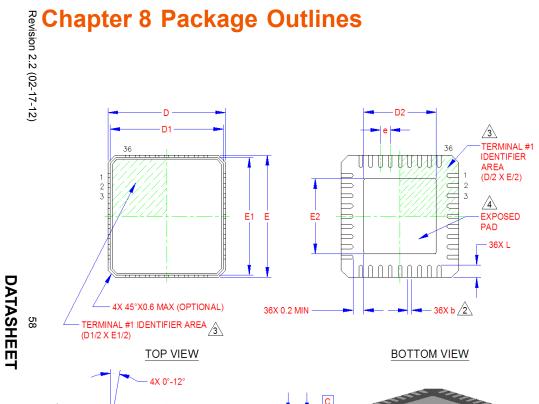

| Chapter 8 Package Outlines                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                            |

| Chapter 7 AC Specifications 7.1 Oscillator/Crystal 7.2 External Clock 7.2.1 SMBus Interface 7.2.2 I <sup>2</sup> C EEPROM 7.2.3 USB 2.0                                                                                                                                                                                                                                                                                                                               | 57<br>57<br>57                                                             |

| Chapter 6 DC Parameters  6.1 Maximum Guaranteed Ratings  6.2 Operating Conditions  6.2.1 Package Thermal Specifications                                                                                                                                                                                                                                                                                                                                               | 49<br>49                                                                   |

| 5.2 I <sup>2</sup> C Slave Address 5.2.1 I <sup>2</sup> C Slave Address 5.2.2 Protocol Implementation 5.2.3 Pull-Up Resistor 5.2.4 In-Circuit EEPROM Programming 5.3 SMBus 5.3.1 SMBus Slave Address 5.3.2 Protocol Implementation 5.3.3 Slave Device Timeout 5.3.4 Stretching the SCLK Signal 5.3.5 SMBus Timing 5.3.6 Bus Reset Sequence 5.3.7 SMBus Alert Response Address 5.4 Default Configuration 5.5 Reset 5.5.1 External Hardware RESET_N 5.5.2 USB Bus Reset | 41<br>42<br>42<br>42<br>42<br>42<br>43<br>44<br>44<br>44<br>44<br>44<br>44 |

| 5.1.31 Register FCh: PortMap 34                                                                                                                                                                                                                                                                                                                                                                                                                                       | 40<br>41                                                                   |

| 5.1.29 Register FAn: Port Swap                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                            |

# **List of Figures**

| Figure 2.1 | USB251xB/xBi Hub Family Block Diagram      | . 10 |

|------------|--------------------------------------------|------|

| Figure 3.1 | 2-Port 36-Pin QFN                          | 11   |

| Figure 3.2 | 3-Port 36-Pin QFN                          | 12   |

| Figure 3.3 | 4-Port 36-Pin QFN                          | . 13 |

| Figure 3.4 | Non-Removable Pin Strap Example            | 22   |

| Figure 3.5 | Pin Strap Option with IPD Pin Example      | 22   |

| Figure 3.6 | LED Pin Strap Example                      |      |

| Figure 4.1 | Battery Charging via External Power Supply |      |

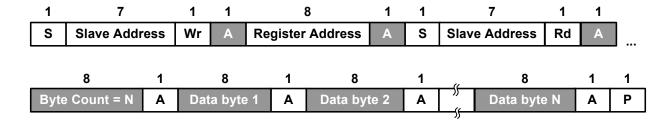

| Figure 5.1 | Block Write                                | 43   |

| Figure 5.2 | Block Read                                 | 43   |

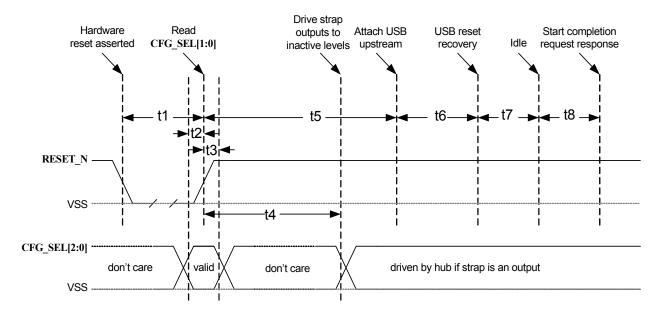

| Figure 5.3 | Reset_N Timing for Default Configuration   |      |

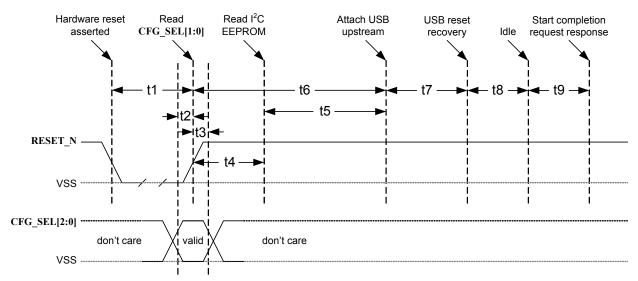

| Figure 5.4 | Reset_N Timing for EEPROM Mode             |      |

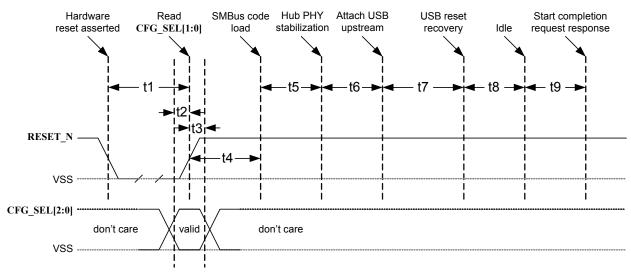

| Figure 5.5 | Reset_N Timing for SMBus Mode              |      |

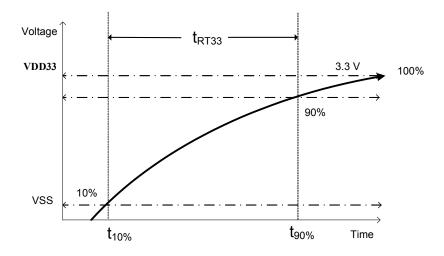

| Figure 6.1 | Supply Rise Time Model                     |      |

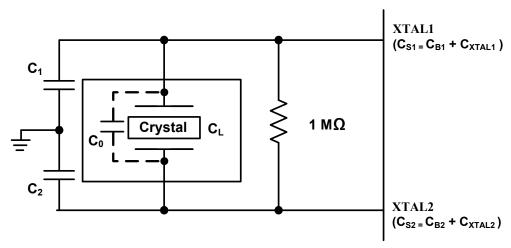

| Figure 7.1 | Typical Crystal Circuit                    | 56   |

| Figure 7.2 | Formula to Find the Value of C1 and C2     | 56   |

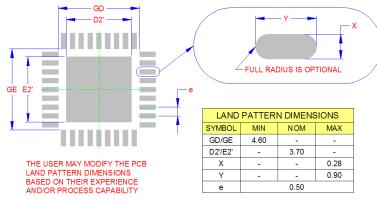

| Figure 8.1 | 36-Pin QFN, 6x6 mm Body, 0.5 mm Pitch      | 58   |

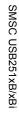

| Figure 8.2 | 36-Pin Package Tape Specifications         |      |

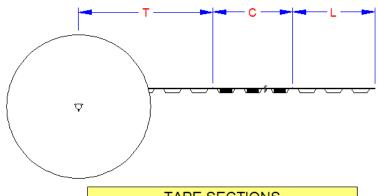

| Figure 8.3 | 36-Pin Package Reel Specifications         |      |

|            |                                            |      |

# **List of Tables**

| Table 1.1  | Summary of Compatibilities between USB251xB/xBi and USB251x/xi/xA/xAi Products | . 9 |

|------------|--------------------------------------------------------------------------------|-----|

| Table 3.1  | USB251xB/xBi Pin List (Alphabetical)                                           | 14  |

| Table 3.2  | USB251xB/xBi Pin List (Alphabetical)                                           | 16  |

| Table 3.3  | USB251xB/xBi Pin Descriptions                                                  | 19  |

| Table 3.4  | Strap Option Summary                                                           | 22  |

| Table 3.5  | Buffer Type Descriptions                                                       | 23  |

| Table 5.1  | Initial Interface/Configuration Options                                        | 26  |

| Table 6.1  | DC Electrical Characteristics                                                  | 50  |

| Table 6.2  | Supply Current Unconfigured: Hi-Speed Host (I <sub>CCINTHS</sub> )             | 51  |

| Table 6.3  | Supply Current Unconfigured: Full-Speed Host (I <sub>CCINTES</sub> )           | 52  |

| Table 6.4  | Supply Current Configured: Hi-Speed Host (I <sub>HCH1</sub> )                  |     |

| Table 6.5  | Supply Current Configured: Full-Speed Host (I <sub>FCC1</sub> )                |     |

| Table 6.6  | Supply Current Suspend (I <sub>CSBY</sub> )                                    |     |

| Table 6.7  | Supply Current Reset (I <sub>CRST</sub> )                                      | 53  |

| Table 6.8  | Pin Capacitance                                                                | 53  |

| Table 6.9  | Package Thermal Resistance Parameters                                          | 54  |

| Table 6.10 | Package Thermal Resistance Parameters                                          | 54  |

| Table 6.11 | Legend                                                                         | 55  |

| Table 7.1  | Crystal Circuit Legend                                                         | 56  |

|            | Customer Revision History                                                      | 63  |

# **Chapter 1 Overview**

The SMSC USB251xB/xBi hub family is a group of low-power, configurable, MTT (multi transaction translator) hub controller ICs. The hub provides downstream ports for embedded USB solutions and is fully compliant with the *USB 2.0 Specification* [1]. Each of the SMSC hub controllers can attach to an upstream port as a full-speed or full-/hi-speed hub. The hub can support low-speed, full-speed, and hi-speed downstream devices when operating as a hi-speed hub.

All required resistors on the USB ports are integrated into the hub. This includes all series termination resistors and all required pull-down and pull-up resistors on D+ and D- pins. The over-current sense inputs for the downstream facing ports have internal pull-up resistors.

The USB251xB/xBi hub family includes programmable features, such as:

- MultiTRAK<sup>TM</sup> Technology: implements a dedicated Transaction Translator (TT) for each port.

Dedicated TTs help maintain consistent full-speed data throughput regardless of the number of active downstream connections.

- PortMap: provides flexible port mapping and disable sequences. The downstream ports of a USB251xB/xBi hub can be reordered or disabled in any sequence to support multiple platform designs with minimum effort. For any port that is disabled, the USB251xB/xBi hub controller automatically reorders the remaining ports to match the USB host controller's port numbering scheme.

- PortSwap: allows direct alignment of USB signals (D+/D-) to connectors to avoid uneven trace length or crossing of the USB differential signals on the PCB.

- **PHYBoost**: enables 4 programmable levels of USB signal drive strength in downstream port transceivers. PHYBoost will also attempt to restore USB signal integrity.

# 1.1 Configurable Features

The SMSC USB251xB/xBi hub controller provides a default configuration that may be sufficient for most applications. Strapping option pins (see Section 3.3.1 on page 22) provide additional features to enhance the default configuration. When the hub is initialized in the default configuration, the following features may be configured using the strapping options:

- Downstream non-removable ports, where the hub will automatically report as a compound device

- Downstream disabled ports

- Enabling of battery charging option on individual ports

The USB251xB/xBi hub controllers can alternatively be configured by an external I<sup>2</sup>C EEPROM or a microcontroller as an SMBus slave device. When the hub is configured by an I<sup>2</sup>C EEPROM or over SMBus, the following configurable features are provided:

- Support for compound devices on a port-by-port basis

- Selectable over-current sensing and port power control on an individual or ganged basis to match the circuit board component selection

- Customizable vendor ID, product ID, and device ID

- Configurable USB signal drive strength

- Configurable USB differential pair pin location

- Configurable delay time for filtering the over-current sense inputs

- Configurable downstream port power-on time reported to the host

- Indication of the maximum current that the hub consumes from the USB upstream port

- Indication of the maximum current required for the hub controller

- Custom string descriptors (up to 31 characters):

Product

Manufacturer

Serial number

Battery charging USB251xB/xBi products are fully footprint compatible with USB251x/xi/xA/xAi products:

Pin-compatible

Direct drop-in replacement

Use the same PCB components

USB-IF Compliance by Similarity for ease of use and a complete cost reduction solution Product IDs, device IDs, and other register defaults may differ. See Section 5.1 on page 27 for details.

Table 1.1 Summary of Compatibilities between USB251xB/xBi and USB251x/xi/xA/xAi Products

| Part<br>Number | Drop-in Replacement |

|----------------|---------------------|

| USB2512        | USB2512B            |

| USB2512i       | USB2512Bi           |

| USB2512A       | USB2512B            |

| USB2512Ai      | USB2512Bi           |

| USB2513        | USB2513B            |

| USB2513i       | USB2513Bi           |

| USB2514        | USB2514B            |

| USB2514i       | USB2514Bi           |

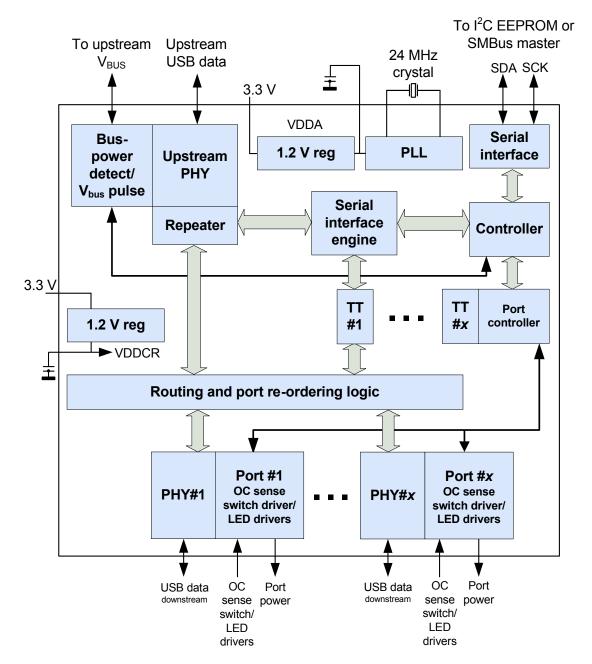

# **Chapter 2 Block Diagram**

x indicates the number of available downstream ports: 2, 3, or 4

Figure 2.1 USB251xB/xBi Hub Family Block Diagram

# **Chapter 3 Pin Information**

This chapter outlines the pinning configurations for each package type available, followed by a corresponding pin list organized alphabetically. The detailed pin descriptions are listed then outlined by function in Section 3.3: *Pin Descriptions (Grouped by Function)* on page 19.

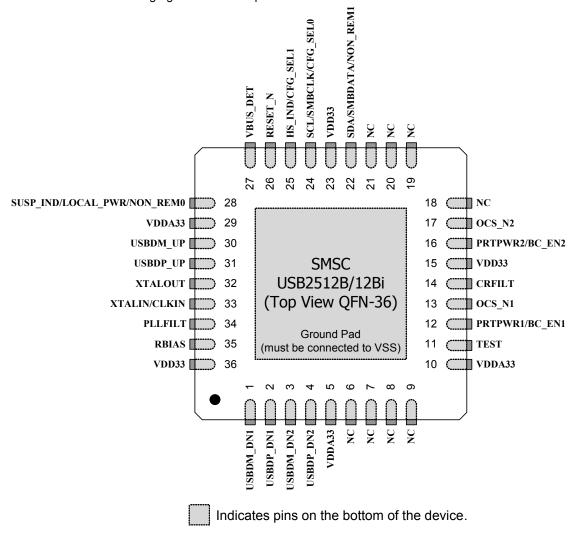

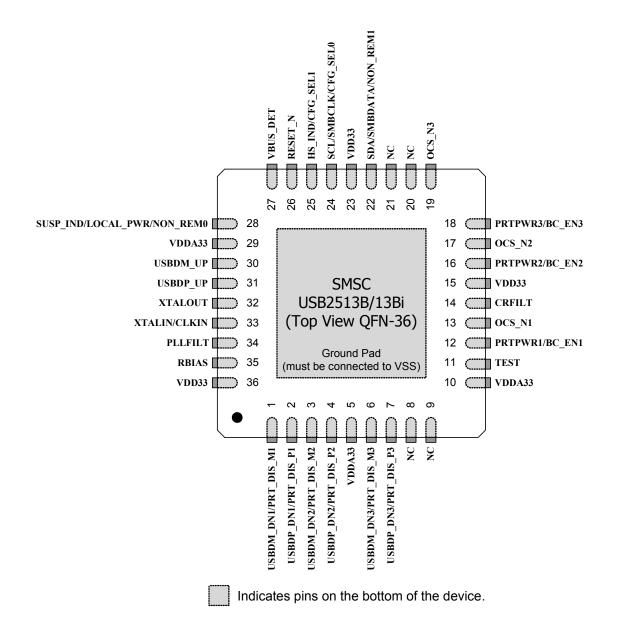

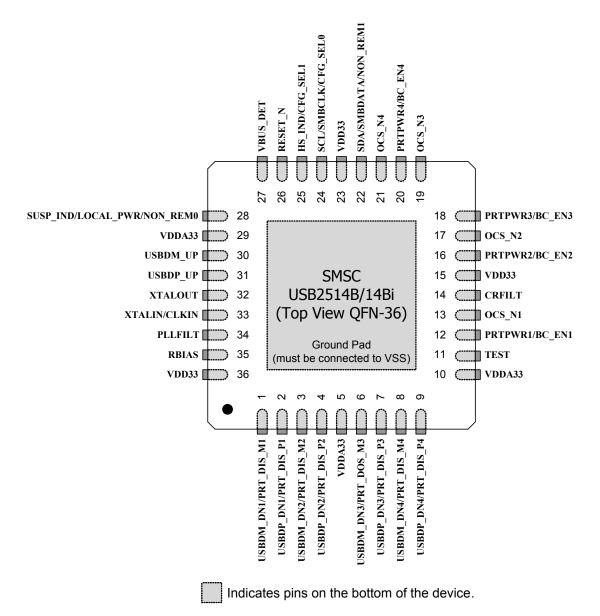

### 3.1 Pin Configurations

The following figures detail the pinouts of the various USB251xB/xBi versions.

Figure 3.1 2-Port 36-Pin QFN

Figure 3.2 3-Port 36-Pin QFN

Figure 3.3 4-Port 36-Pin QFN

# 3.2 Pin List (Alphabetical)

Table 3.1 USB251xB/xBi Pin List (Alphabetical)

|            |                                     | PIN NUMBERS           |                       |                       |  |

|------------|-------------------------------------|-----------------------|-----------------------|-----------------------|--|

|            |                                     |                       | 36 QFN                |                       |  |

| SYMBOL     | NAME                                | USB2512B<br>USB2512Bi | USB2513B<br>USB2513Bi | USB2514B<br>USB2514Bi |  |

| BC_EN1     | Battery Charging                    | 12                    |                       |                       |  |

| BC_EN2     | Strap Option                        | 16                    |                       |                       |  |

| BC_EN3     |                                     | -                     | 1                     | 8                     |  |

| BC_EN4     |                                     |                       | -                     | 20                    |  |

| CFG_SEL0   | Configuration                       |                       | 24                    |                       |  |

| CFG_SEL1   | Programming Selection               |                       | 25                    |                       |  |

| CLKIN      | External Clock Input                |                       | 33                    |                       |  |

| CRFILT     | Core Regulator Filter<br>Capacitor  |                       | 14                    |                       |  |

| Ground Pad | Exposed Pad Tied to<br>Ground (VSS) | ePad                  |                       |                       |  |

| HS_IND     | Hi-Speed Upstream<br>Port Indicator | 25                    |                       |                       |  |

| LOCAL_PWR  | Local Power<br>Detection            | 28                    |                       |                       |  |

| NC         | No Connect                          | 6                     |                       | -                     |  |

| NC         |                                     | 7                     |                       | -                     |  |

| NC         |                                     | 18                    |                       | -                     |  |

| NC         |                                     | 19 -                  |                       |                       |  |

| NC         |                                     | 8 -                   |                       |                       |  |

| NC         |                                     | (                     | 9                     | -                     |  |

| NC         |                                     | 20 -                  |                       |                       |  |

| NC         |                                     | 2                     | :1                    | -                     |  |

| NON_REM0   | Non-Removable Port                  |                       | 28                    |                       |  |

| NON_REM1   | Strap Option                        | 22                    |                       |                       |  |

| OCS_N1     | Over-Current Sense                  | 13                    |                       |                       |  |

| OCS_N2     |                                     | 17                    |                       |                       |  |

| OCS_N3     |                                     | - 19                  |                       |                       |  |

| OCS_N4     |                                     | - 21                  |                       |                       |  |

| PLLFILT    | PLL Regulator Filter<br>Capacitor   | 34                    |                       |                       |  |

Table 3.1 USB251xB/xBi Pin List (Alphabetical) (continued)

|            |                                     | PIN NUMBERS           |                       |                        |  |

|------------|-------------------------------------|-----------------------|-----------------------|------------------------|--|

|            |                                     |                       | 36 QFN                |                        |  |

| SYMBOL     | NAME                                | USB2512B<br>USB2512Bi | USB2513B<br>USB2513Bi | USB2514Bi<br>USB2514Bi |  |

| PRT_DIS_M1 | Downstream Port                     | -                     |                       | 1                      |  |

| PRT_DIS_M2 | Disable Strap Option                |                       | 3                     |                        |  |

| PRT_DIS_M3 |                                     | -                     | (                     | 6                      |  |

| PRT_DIS_M4 |                                     |                       | -                     | 8                      |  |

| PRT_DIS_P1 | Port Disable                        | -                     |                       | 2                      |  |

| PRT_DIS_P2 |                                     |                       | 4                     |                        |  |

| PRT_DIS_P3 |                                     | -                     | -                     | 7                      |  |

| PRT_DIS_P4 |                                     |                       | -                     | 9                      |  |

| PRTPWR1    | USB Port Power                      |                       | 12                    |                        |  |

| PRTPWR2    | Enable                              |                       | 16                    |                        |  |

| PRTPWR3    |                                     | -                     | 1                     | 8                      |  |

| PRTPWR4    |                                     |                       | -                     | 20                     |  |

| RBIAS      | USB Transceiver<br>Bias             | 35                    |                       |                        |  |

| RESET_N    | Reset Input                         | 26                    |                       |                        |  |

| SCL        | Serial Clock                        | 24                    |                       |                        |  |

| SDA        | Serial Data Signal                  |                       | 22                    |                        |  |

| SMBCLK     | System Management<br>Bus Clock      |                       | 24                    |                        |  |

| SMBDATA    | Server Message<br>Block Data Signal |                       | 22                    |                        |  |

| SUSP_IND   | Active/Suspend<br>Status Indicator  |                       | 28                    |                        |  |

| TEST       | Test Pin                            |                       | 11                    |                        |  |

| USBDM_UP   | USB Bus Data                        |                       | 30                    |                        |  |

| USBDP_UP   |                                     |                       | 31                    |                        |  |

| USBDM_DN1  | Hi-Speed USB Data                   | 1                     |                       |                        |  |

| USBDM_DN2  |                                     | 3                     |                       |                        |  |

| USBDM_DN3  |                                     | - 6                   |                       |                        |  |

| USBDM_DN4  |                                     | - 8                   |                       |                        |  |

| USBDP_DN1  |                                     | 2                     |                       |                        |  |

| USBDP_DN2  |                                     | 4                     |                       |                        |  |

| USBDP_DN3  |                                     | - 7                   |                       |                        |  |

| USBDP_DN4  |                                     | - 9                   |                       |                        |  |

Table 3.1 USB251xB/xBi Pin List (Alphabetical) (continued)

|          |                                  | PIN NUMBERS 36 QFN    |                       |                       |

|----------|----------------------------------|-----------------------|-----------------------|-----------------------|

|          |                                  |                       |                       |                       |

| SYMBOL   | NAME                             | USB2512B<br>USB2512Bi | USB2513B<br>USB2513Bi | USB2514B<br>USB2514Bi |

| VBUS_DET | Upstream VBUS<br>Power Detection | 27                    |                       |                       |

| VDD33    | 3.3 V Power                      | 5                     |                       |                       |

| VDD33    |                                  | 10                    |                       |                       |

| VDD33    |                                  | 15                    |                       |                       |

| VDD33    |                                  | 23                    |                       |                       |

| VDD33    |                                  | 29                    |                       |                       |

| VDD33    |                                  | 36                    |                       |                       |

| XTALIN   | Crystal Input                    | 33                    |                       |                       |

| XTALOUT  | Crystal Output                   | 32                    |                       |                       |

Table 3.2 USB251xB/xBi Pin List (Alphabetical)

|                     |                                     | PIN NUMBERS 36 QFN    |                       |                       |

|---------------------|-------------------------------------|-----------------------|-----------------------|-----------------------|

|                     |                                     |                       |                       |                       |

| SYMBOL              | NAME                                | USB2512B<br>USB2512Bi | USB2513B<br>USB2513Bi | USB2514B<br>USB2514Bi |

| BC_EN1              | Battery Charging                    |                       | 12                    |                       |

| BC_EN2              | Strap Option                        | - 16<br>- 18          |                       |                       |

| BC_EN3              |                                     |                       |                       | 8                     |

| BC_EN4              |                                     |                       | -                     | 20                    |

| CFG_SEL0            | Configuration                       | 24                    |                       |                       |

| CFG_SEL1            | Programming Selection               | 25                    |                       |                       |

| CLKIN               | External Clock Input                | 33                    |                       |                       |

| CRFILT              | Core Regulator<br>Filter Capacitor  | 14                    |                       |                       |

| Ground Pad<br>(VSS) | Exposed Pad Tied to Ground (VSS)    | ePad                  |                       |                       |

| HS_IND              | Hi-Speed Upstream<br>Port Indicator | 25                    |                       |                       |

| LOCAL_PWR           | Local Power<br>Detection            | 28                    |                       |                       |

Table 3.2 USB251xB/xBi Pin List (Alphabetical) (continued)

|            |                                   | PIN NUMBERS           |                       |                       |

|------------|-----------------------------------|-----------------------|-----------------------|-----------------------|

|            |                                   |                       | 36 QFN                |                       |

| SYMBOL     | NAME                              | USB2512B<br>USB2512Bi | USB2513B<br>USB2513Bi | USB2514B<br>USB2514Bi |

| NC         | No Connect                        | 6                     | -                     |                       |

| NC         |                                   | 7                     | -                     | -                     |

| NC         |                                   | 18                    | -                     |                       |

| NC         |                                   | 19                    | -                     |                       |

| NC         |                                   | 8                     | 3                     | -                     |

| NC         |                                   | 9                     | )                     | -                     |

| NC         |                                   | 2                     | 0                     | -                     |

| NC         |                                   | 2                     | 1                     | -                     |

| NON_REM0   | Non-Removable                     |                       | 28                    |                       |

| NON_REM1   | Port Strap Option                 | 22                    |                       |                       |

| OCS_N1     | Over-Current Sense                |                       | 13                    |                       |

| OCS_N2     |                                   | 17                    |                       |                       |

| OCS_N3     |                                   | -                     | 1                     | 9                     |

| OCS_N4     |                                   | -                     |                       | 21                    |

| PLLFILT    | PLL Regulator Filter<br>Capacitor |                       | 34                    |                       |

| PRT_DIS_M1 | Downstream Port                   | -                     | 1                     |                       |

| PRT_DIS_M2 | Disable Strap Option              |                       | 3                     |                       |

| PRT_DIS_M3 | Орион                             | -                     | 6                     | 3                     |

| PRT_DIS_M4 |                                   | -                     | -                     | 8                     |

| PRT_DIS_P1 | Port Disable                      | -                     | 2                     | 2                     |

| PRT_DIS_P2 |                                   |                       | 4                     |                       |

| PRT_DIS_P3 |                                   | -                     | 7                     | 7                     |

| PRT_DIS_P4 |                                   | -                     |                       | 9                     |

| PRTPWR1    | USB Port Power                    |                       | 12                    |                       |

| PRTPWR2    | Enable                            | 16                    |                       |                       |

| PRTPWR3    |                                   | - 18                  |                       | 8                     |

| PRTPWR4    |                                   | -                     | -                     | 20                    |

| RBIAS      | USB Transceiver<br>Bias           |                       | 35                    |                       |

| RESET_N    | Reset Input                       |                       | 26                    |                       |

| SCL        | Serial Clock                      | 24                    |                       |                       |

| SDA        | Serial Data Signal                | 22                    |                       |                       |

Table 3.2 USB251xB/xBi Pin List (Alphabetical) (continued)

|           |                                     |                       | PIN NUMBERS           |                       |

|-----------|-------------------------------------|-----------------------|-----------------------|-----------------------|

|           |                                     |                       | 36 QFN                |                       |

| SYMBOL    | NAME                                | USB2512B<br>USB2512Bi | USB2513B<br>USB2513Bi | USB2514B<br>USB2514Bi |

| SMBCLK    | System<br>Management Bus<br>Clock   |                       | 24                    |                       |

| SMBDATA   | Server Message<br>Block Data Signal |                       | 22                    |                       |

| SUSP_IND  | Active/Suspend<br>Status Indicator  |                       | 28                    |                       |

| TEST      | Test Pin                            |                       | 11                    |                       |

| USBDM_UP  | USB Bus Data                        |                       | 30                    |                       |

| USBDP_UP  |                                     | 31                    |                       |                       |

| USBDM_DN1 | Hi-Speed USB Data                   | 1                     |                       |                       |

| USBDM_DN2 |                                     | 3                     |                       |                       |

| USBDM_DN3 |                                     | - 6                   |                       | 3                     |

| USBDM_DN4 |                                     |                       | -                     | 8                     |

| USBDP_DN1 |                                     |                       | 2                     |                       |

| USBDP_DN2 |                                     |                       | 4                     |                       |

| USBDP_DN3 |                                     | -                     | -                     | 7                     |

| USBDP_DN4 |                                     |                       | -                     | 9                     |

| VBUS_DET  | Upstream VBUS<br>Power Detection    |                       | 27                    |                       |

| VDD33     | 3.3 V Digital Power                 |                       | 15                    |                       |

| VDD33     |                                     |                       | 23                    |                       |

| VDD33     |                                     |                       | 36                    |                       |

| VDDA33    | 3.3 V Analog Power                  | er 5                  |                       |                       |

| VDDA33    |                                     | 10                    |                       |                       |

| VDDA33    |                                     | 29                    |                       |                       |

| VDDA33    |                                     | -                     |                       |                       |

| XTALIN    | Crystal Input                       | 33                    |                       |                       |

| XTALOUT   | Crystal Output                      |                       | 32                    |                       |

### 3.3 Pin Descriptions (Grouped by Function)

An N at the end of a signal name indicates that the active (asserted) state occurs when the signal is at a low voltage level. When the N is not present, the signal is asserted when it is at a high voltage level. The terms assertion and negation are used exclusively in order to avoid confusion when working with a mixture of active low and active high signals. The term assert, or assertion, indicates that a signal is active, independent of whether that level is represented by a high or low voltage. The term negate, or negation, indicates that a signal is inactive.

Table 3.3 USB251xB/xBi Pin Descriptions

| SYMBOL                           | BUFFER<br>TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------------------------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                  | ···· <b>-</b>  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                  |                | UPSTREAM USB 2.0 INTERFACES                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| USBDM_UP<br>USBDP_UP             | IO-U           | USB Data: connect to the upstream USB bus data signals (host, port, or upstream hub).                                                                                                                                                                                                                                                                                                                                                                                                        |

| VBUS_DET                         | I              | Detect Upstream VBUS Power: detects the state of the upstream VBUS power. The SMSC hub monitors VBUS_DET to determine when to assert the internal D+ pull-up resistor: (signaling a connect event).                                                                                                                                                                                                                                                                                          |

|                                  |                | When designing a detachable hub, this pin should be connected to VBUS on the upstream port via a 2:1 voltage divider. Two 100 k $\Omega$ resistors are suggested.                                                                                                                                                                                                                                                                                                                            |

|                                  |                | For self-powered applications with a permanently attached host, this pin must be connected to a dedicated host control output, or connected to the 3.3 V domain that powers the host (typically VDD33).                                                                                                                                                                                                                                                                                      |

|                                  |                | DOWNSTREAM USB 2.0 INTERFACES                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| USBDP_DN[x:1]/<br>PRT_DIS_P[x:1] | IO-U           | Hi-Speed USB Data: connect to the downstream USB peripheral devices attached to the hub's port. To disable, use a 10 k $\Omega$ pull-up resistor to 3.3 V.                                                                                                                                                                                                                                                                                                                                   |

| USBDM_DN[x:1]/<br>PRT_DIS_M[x:1] |                | Downstream Port Disable Strap Option: when enabled by package and configuration settings (see Table 5.1 on page 26), this pin is sampled at RESET_N negation to determine if the port is disabled.                                                                                                                                                                                                                                                                                           |

|                                  |                | To disable a port, pull up both PRT_DIS_M[x:1] and PRT_DIS_P[x:1] pins for the corresponding port number(s). See Section 3.3.1, on page 22 for pull up details.                                                                                                                                                                                                                                                                                                                              |

| PRTPWR[x:1]/                     | O12            | USB Power Enable: enables power to USB peripheral devices downstream.                                                                                                                                                                                                                                                                                                                                                                                                                        |

| BC_EN[x:1]                       | IPD            | Battery Charging Strap Option: when enabled by package and configuration settings (see Table 5.1), the pin will be sampled at RESET_N negation to determine if ports [x:1] support the battery charging protocol. When supporting the battery charging protocol, the hub also supports external port power controllers. The battery charging protocol enables a device to draw the currents per the USB battery charging specification. See Section 3.3.1, on page 22 for strap pin details. |

|                                  |                | Battery charging feature is supported for port <i>x</i> Battery charging feature is not supported for port <i>x</i>                                                                                                                                                                                                                                                                                                                                                                          |

| OCS_N[x:1]                       | IPU            | Over-Current Sense: input from external current monitor indicating an over-current condition.                                                                                                                                                                                                                                                                                                                                                                                                |

| RBIAS                            | I-R            | USB Transceiver Bias: a 12.0 k $\Omega$ (+/- 1%) resistor is attached from ground to this pin to set the transceiver's internal bias settings.                                                                                                                                                                                                                                                                                                                                               |

Table 3.3 USB251xB/xBi Pin Descriptions (continued)

| SYMBOL   | BUFFER<br>TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                       |

|----------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          |                | SERIAL PORT INTERFACES                                                                                                                                                                                                                                                                            |

| SDA/     | I/OSD12        | Serial Data Signal                                                                                                                                                                                                                                                                                |

| SMBDATA/ |                | System Management Bus Signal                                                                                                                                                                                                                                                                      |

| NON_REM1 |                | Non-Removable Port 1 Strap Option: when enabled by package and configuration options (see Table 5.1 on page 26), this pin will be sampled (in conjunction with LOCAL PWR/SUSP_IND/NON_REM0) at RESET_N negation to determine if ports [x:1] contain permanently attached (non-removable) devices: |

|          |                | NON_REM[1:0] = 00 : all ports are removable NON_REM[1:0] = 01 : port 1 is non-removable NON_REM[1:0] = 10 : ports 1 and 2 are non-removable NON_REM[1:0] = 11 : when available, ports 1, 2, and 3 are non-removable                                                                               |

|          |                | When NON_REM[1:0] is chosen such that there is a non-removable device, the hub will automatically report itself as a compound device (using the proper descriptors).                                                                                                                              |

| RESET_N  | IS             | RESET Input: the system can reset the chip by driving this input low. The minimum active low pulse is 1 $\mu s. $                                                                                                                                                                                 |

| SCL/     | I/OSD12        | Serial Clock (SCL)                                                                                                                                                                                                                                                                                |

| SMBCLK/  |                | System Management Bus Clock                                                                                                                                                                                                                                                                       |

| CFG_SEL0 |                | Configuration Select: the logic state of this multifunction pin is internally latched on the rising edge of RESET_N (RESET_N negation), and will determine the hub configuration method as described in Table 5.1.                                                                                |

| HS_IND/  | I/O12          | Hi-Speed Upstream Port Indicator: upstream port connection speed.                                                                                                                                                                                                                                 |

|          |                | Asserted = the hub is connected at HS<br>Negated = the hub is connected at FS                                                                                                                                                                                                                     |

|          |                | Note: When implementing an external LED on this pin, the active state is indicated above and outlined in Section 3.3.1.3, on page 23.                                                                                                                                                             |

| CFG_SEL1 |                | Configuration Programming Select 1: the logic state of this pin is internally latched on the rising edge of RESET_N (RESET_N negation), and will determine the hub configuration method as described in Table 5.1.                                                                                |

|          |                | MISC                                                                                                                                                                                                                                                                                              |

| XTALIN   | ICLKx          | Crystal Input: 24 MHz crystal.                                                                                                                                                                                                                                                                    |

|          |                | This pin connects to either one terminal of the crystal or to an external 24 MHz clock when a crystal is not used.                                                                                                                                                                                |

| CLKIN    |                | External Clock Input: this pin connects to either one terminal of the crystal or to an external 24 MHz clock when a crystal is not used.                                                                                                                                                          |

| XTALOUT  | OCLKx          | Crystal Output: this is the other terminal of the crystal circuit with 1.2 V p-p output and a weak (< 1mA) driving strength. When an external clock source is used to drive XTALIN/CLKIN, leave this pin unconnected, or use with appropriate caution.                                            |

Table 3.3 USB251xB/xBi Pin Descriptions (continued)

| SYMBOL     | BUFFER<br>TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                        |

|------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SUSP_IND/  | I/O            | Active/Suspend Status LED: indicates USB state of the hub.                                                                                                                                                                                                                                         |

|            |                | Negated = unconfigured; or configured and in USB suspend<br>Asserted = hub is configured and is active (i.e., not in suspend)                                                                                                                                                                      |

| LOCAL_PWR/ |                | Local Power: detects availability of local self-power source.                                                                                                                                                                                                                                      |

|            |                | Low = self/local power source is NOT available (i.e., the hub gets all power from the upstream USB VBus) High = self/local power source is available                                                                                                                                               |

| NON_REM0   |                | Non-Removable 0 Strap Option: when enabled by package and configuration settings (see Table 5.1 on page 26), this pin will be sampled (in conjunction with NON_REM[1]) at RESET_N negation to determine if ports [x:1] contain permanently attached (non-removable) devices:                       |

|            |                | <b>Note:</b> When implementing an external LED on this pin, the active state is outlined below and detailed in Section 3.3.1.3, on page 23.                                                                                                                                                        |

|            |                | NON_REM[1:0] = 00 : all ports are removable; LED is active high NON_REM[1:0] = 01 : port 1 is non-removable; LED is active low NON_REM[1:0] = 10 : ports 1 and 2 are non-removable; LED is active high NON_REM[1:0] = 11 : (when available) ports 1, 2, and 3 are non-removable; LED is active low |

| TEST       | IPD            | Test Pin: treat as a no connect pin or connect to ground. No trace or signal should be routed or attached to this pin.                                                                                                                                                                             |

|            |                | POWER, GROUND, and NO CONNECTS                                                                                                                                                                                                                                                                     |

| CRFILT     |                | VDD Core Regulator Filter Capacitor: this pin can have up to a 0.1 $\mu\text{F}$ low-ESR capacitor to VSS, or be left unconnected.                                                                                                                                                                 |

| VDD33      |                | 3.3 V Power                                                                                                                                                                                                                                                                                        |

| PLLFILT    |                | PLL Regulator Filter Capacitor: this pin can have up to a 0.1 $\mu\text{F}$ low-ESR capacitor to VSS, or be left unconnected.                                                                                                                                                                      |

| VSS        |                | Ground Pad/ePad: the package slug is the only VSS for the device and must be tied to ground with multiple vias.                                                                                                                                                                                    |

| NC         |                | No Connect: no signal or trace should be routed or attached to all NC pins.                                                                                                                                                                                                                        |

#### 3.3.1 Configuring the Strap Pins

If a pin's strap function is enabled thru the hub configuration selection, (Table 5.1: *Initial Interface/Configuration Options* on page 26) the strap pins must be pulled either high or low using the values provided in Table 3.4. Each strap option is dependent on the pin's buffer type, as outlined in the sections that follow.

| STRAP OPTION       | RESISTOR VALUE | BUFFER TYPE | NOTES                                                                                     |

|--------------------|----------------|-------------|-------------------------------------------------------------------------------------------|

| Non-Removable      | 47 - 100 kΩ    | I/O         |                                                                                           |

| Internal Pull-Down | 10 kΩ          | IPD         | <ul><li>Only applicable to port power pins</li><li>Contains a built-in resistor</li></ul> |

| LED                | 47 - 100 kΩ    | I/O         |                                                                                           |

**Table 3.4 Strap Option Summary**

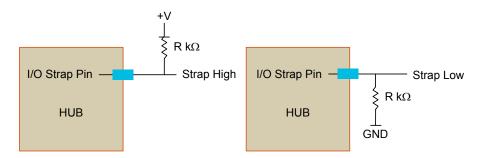

#### 3.3.1.1 Non-Removable

If a strap pin's buffer type is I/O, an external pull-up or pull-down must be implemented as shown in Figure 3.4. Use Strap High to set the strap option to 1 and Stap Low to set the strap option to 0. When implementing the Strap Low option, no additional components are needed (i.e., the internal pull-down provides the resistor)

Figure 3.4 Non-Removable Pin Strap Example

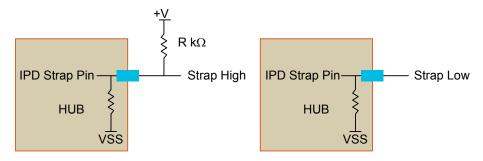

#### 3.3.1.2 Internal Pull-Down (IPD)

If a strap pin's buffer type is IPD (pins  $BC_EN[x:1]$ ), one of the two hardware configurations outlined below must be implemented. Use the Strap High configuration to set the strap option value to 1 and Strap Low to set the strap option value to 0.

Figure 3.5 Pin Strap Option with IPD Pin Example

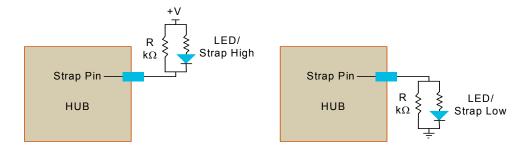

#### 3.3.1.3 LED

If a strap pin's buffer type is I/O and shares functionality with an LED, the hardware configuration outlined below must be implemented. The internal logic will drive the LED appropriately (active high or low) depending on the sampled strap option. Use the Strap High configuration to set the strap option value to 1 and Strap Low to set the strap option to 0.

Figure 3.6 LED Pin Strap Example

### 3.4 Buffer Type Descriptions

**Table 3.5 Buffer Type Descriptions**

| BUFFER TYPE | DESCRIPTION                                                                                                    |

|-------------|----------------------------------------------------------------------------------------------------------------|

| I           | Input                                                                                                          |

| I/O         | Input/output                                                                                                   |

| IPD         | Input with internal weak pull-down resistor                                                                    |

| IPU         | Input with internal weak pull-up resistor                                                                      |

| IS          | Input with Schmitt trigger                                                                                     |

| 012         | Output 12 mA                                                                                                   |

| I/O12       | Input/output buffer with 12 mA sink and 12 mA source                                                           |

| I/OSD12     | Open drain with Schmitt trigger and 12 mA sink. Meets the I <sup>2</sup> C-Bus Specification [2] requirements. |

| ICLKx       | XTAL clock input                                                                                               |

| OCLKx       | XTAL clock output                                                                                              |

| I-R         | RBIAS                                                                                                          |

| I/O-U       | Analog input/output defined in USB specification                                                               |

# **Chapter 4 Battery Charging Support**

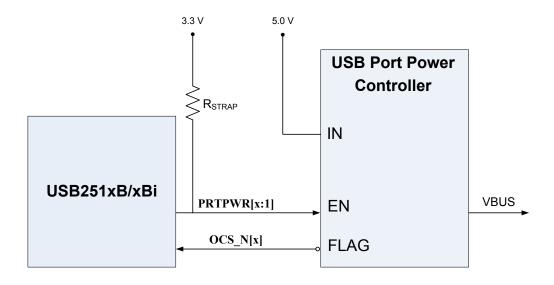

The USB251xB/xBi SMSC hub provides support for battery charging devices on a per port basis in compliance with the *USB Battery Charging Specification, Revision 1.1*. The hub can be configured to individually enable each downstream port for battery charging support either via pin strapping as illustrated in Figure 4.1 or by setting the corresponding configuration bits via I<sup>2</sup>C EEPROM or SMBus (Section 5.1 on page 27).

Figure 4.1 Battery Charging via External Power Supply

Note: R<sub>STRAP</sub> enables battery charging.

# 4.1 USB Battery Charging