# DATA SHEET

# ADPCM SPEECH SYNTHESIZER LSIs

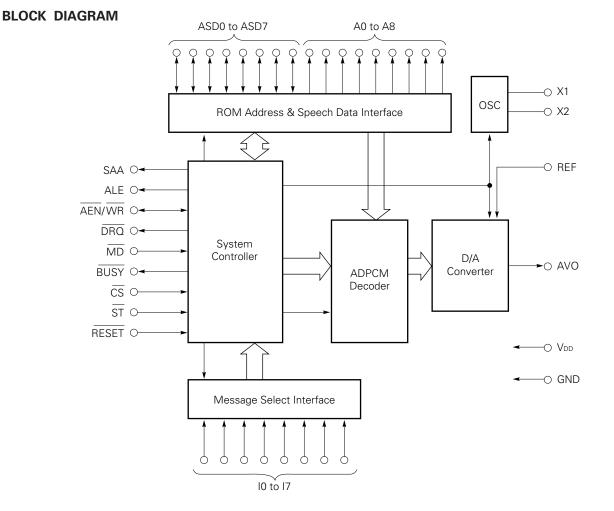

The  $\mu$ PD7759 is an external ROM type speech synthesis LSI employing the waveform coding method. In addition to the ROM capability of up to 1 Mbit, the  $\mu$ PD7759 realizes the synthesis of speech sounds of any length by using the ADPCM data transferred from an external ROM.

As the synthesizing method, it adopts the ADPCM method and the PCM + waveform element method. The ADPCM method is suitable for synthesizing clear and natural speech sounds, and the PCM + waveform element method is for the synthesis of sound effects and melodies. And by using them together, the  $\mu$ PD7759 realizes the long-time synthesis of high-quality sounds.

Because of the short turn-around time of speech analysis, the  $\mu$ PD7759 can perform the quick system development using a PROM, or the evaluation of an on-chip ROM type of the  $\mu$ PD7755 family.

### **FEATURES**

- : ADPCM, PCM + waveform element methods used together ★ ● Synthesizing method

- Sampling frequency

- : 5, 6 or 8 kHz

- Bit rate (speech) : 20 to 32 K bps

- Number of Messages : 256 (MAX.)

- External speech data ROM

| Parameters | Speech data ROM<br>(External) | Synthesizing time    |                                                                       |  |  |  |

|------------|-------------------------------|----------------------|-----------------------------------------------------------------------|--|--|--|

| Products   |                               | Speech (ADPCM) Note1 | Melodies & sound effects <sup>Note2</sup><br>(PCM + waveform element) |  |  |  |

| μPD7759    | 1 Mbits                       | 50 sec. (TYP.)       | 340 sec. (TYP.)                                                       |  |  |  |

Note 1. The synthesizing time for the speech is the value for a 6 kHz sampling.

2. The synthesizing time for the melodies & sound effects is variable according to their tone.

• Speech output

: Current sink type analog output, 9-bit D/A converter

• Host CPU interface

: Compatible with a 4/8-bit CPU

- Standby mode

- : 2.7 to 5.5 V Supply voltage

: Pop-noise preventive circuit incorporated

CMOS technology

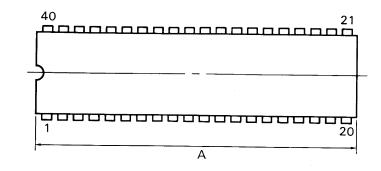

### **ORDERING INFORMATION**

| Part Number        | Package                      | Quality grade |

|--------------------|------------------------------|---------------|

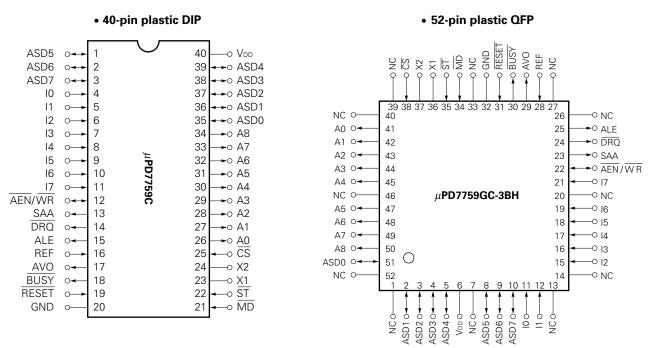

| $\mu$ PD7759C      | 40-pin plastic DIP (600 mil) | Standard      |

| $\mu$ PD7759GC-3BH | 52-pin plastic QFP (□14 mm)  | Standard      |

Please refer to "Quality grade on NEC Semiconductor Devices" (Document number IEI-1209) published by NEC Corporation to know the specification of quality grade on the devices and its recommended applications.

The information in this document is subject to change without notice.

### PIN CONFIGURATION (Top View)

#### 2

# **1. PIN FUNCTIONS**

#### **1.1 COMMON FUNCTION TO ALL MODES**

| Pin<br>(Abbre-<br>viation) | 52-pin<br>QFP<br>Pin No.                              | 40-pin<br>DIP<br>Pin No. | I/O    | Function                                                                                                                                                                                                                                                                                                                                                                |

|----------------------------|-------------------------------------------------------|--------------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Vdd                        | 6                                                     | 40                       | _      | Power supply (2.7 to 5.5 V)                                                                                                                                                                                                                                                                                                                                             |

| DRQ                        | 24                                                    | 14                       | Output | Speech synthesis data request.                                                                                                                                                                                                                                                                                                                                          |

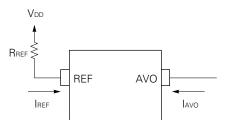

| REF                        | 28                                                    | 16                       | Input  | D/A converter reference current input.<br>The sink-load current input causes the output current of the<br>D/A converter to change.<br>The D/A converter reference current is passed to VDD via<br>a resistor.<br>In standby mode, REF is set to high impedance.                                                                                                         |

| AVO                        | 29                                                    | 17                       | Output | Analog speech signal output.<br>AVO outputs a unipolar sink-load current.<br>The output current is reduced to 0 when the μPD7759 is in the<br>standby mode.<br>The output current of the D/A converter from AVO is changed<br>according to the input current from REF.<br>Maximum output current of the D/A converter is approx. the<br>34 times the REF input current. |

| BUSY                       | 30                                                    | 18                       | Output | Active-low BUSY signal output. When inputting ST signal,<br>it outputs a low level signal.<br>MD, ST and WR are invalid while BUSY is low.<br>In standby mode, BUSY is set to high impedance.                                                                                                                                                                           |

| RESET                      | 31                                                    | 19                       | Input  | Reset input.<br>In standby mode, RESET must be at low level more than 12<br>clock cycles after clock oscillation becomes stable.<br>In operation mode, RESET must be at low level for 12 clock<br>cycles (oscillation clock).                                                                                                                                           |

| GND                        | 32                                                    | 20                       | _      | Ground.                                                                                                                                                                                                                                                                                                                                                                 |

| X1                         | 36                                                    | 23                       | _      | Ceramic resonator connection for generating a clock signal.<br>The 640 kHz ceramic resonator can be connected.                                                                                                                                                                                                                                                          |

| X2                         | 37                                                    | 24                       | _      | In standby mode, the $\mu$ PD7759 outputs a low-level to X1 and a high-level to X2.                                                                                                                                                                                                                                                                                     |

| NC                         | 1, 7, 13,<br>14, 20, 26,<br>27, 33, 39,<br>40, 46, 52 |                          | _      | No Connection                                                                                                                                                                                                                                                                                                                                                           |

$\star$

### 1.2 PIN FUNCTION FOR STAND ALONE MODE

| Pin<br>(Abbre-<br>viation)                                   | 52-pin<br>QFP<br>Pin No.                           | 40-pin<br>DIP<br>Pin No.                           | I/O              | Function                                                                                                                                                                                                                                                                                                                                                                                                                |

|--------------------------------------------------------------|----------------------------------------------------|----------------------------------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10<br>11<br>12<br>13<br>14<br>15<br>16<br>17                 | 11<br>12<br>15<br>16<br>17<br>18<br>19<br>21       | 4<br>5<br>7<br>8<br>9<br>10<br>11                  | Input            | Message selection code input.<br>The message selection code signals are positive logics.<br>Ground the pins not used.<br>These pins are connected to the internal latch circuit which<br>latches I0 to I7 data at the rising edge of the ST input.<br>In standby mode, these pins should be set high or low level.<br>If they are biased at or near the typical CMOS threshold,<br>the excess supply current is caused. |

| AEN/WR                                                       | 22                                                 | 12                                                 | Output/<br>Input | This signal is at low level while address signal is valid.<br>Controls the latch circuit for the higher 8 bits of the external<br>ROM address.                                                                                                                                                                                                                                                                          |

| SAA                                                          | 23                                                 | 13                                                 | Output           | Outputs high level when the start address of a message stored in the directory area of data memory, is being read out.                                                                                                                                                                                                                                                                                                  |

| ALE                                                          | 25                                                 | 15                                                 | Output           | Determines the timing that higher 8 bits of the external ROM<br>address are externally latched. They must be latched at the<br>falling edge of the signal.                                                                                                                                                                                                                                                              |

| MD                                                           | 34                                                 | 21                                                 | Input            | set at high-level.                                                                                                                                                                                                                                                                                                                                                                                                      |

| ST                                                           | 35                                                 | 22                                                 | Input            | Start signal input.<br>When $\overline{ST}$ goes low while $\overline{CS}$ is at low level, the $\mu$ PD7759 starts<br>synthesizing the message specified by I0 to I7. In standby<br>mode, this signal resets the standby mode and starts speech<br>synthesis.                                                                                                                                                          |

| cs                                                           | 38                                                 | 25                                                 | Input            | Chip select signal input.<br>ST becomes valid when CS goes low.                                                                                                                                                                                                                                                                                                                                                         |

| A0<br>A1<br>A2<br>A3<br>A4<br>A5<br>A6<br>A7<br>A8           | 41<br>42<br>43<br>44<br>45<br>47<br>48<br>49<br>50 | 26<br>27<br>28<br>29<br>30<br>31<br>32<br>33<br>34 | Output           | Outputs the lower 9 bits of the external ROM address.                                                                                                                                                                                                                                                                                                                                                                   |

| ASD0<br>ASD1<br>ASD2<br>ASD3<br>ASD4<br>ASD5<br>ASD6<br>ASD7 | 51<br>2<br>3<br>4<br>5<br>8<br>9<br>10             | 35<br>36<br>37<br>38<br>39<br>1<br>2<br>3          | Input/<br>Output | <ul> <li>(1) Outputs the higher 8 bits of external ROM address.</li> <li>(2) Inputs 8-bit speech synthesis data from the external ROM.<br/>These functions are executed from (1) to (2) on a time-<br/>shared basis.</li> </ul>                                                                                                                                                                                         |

# 1.3 PIN FUNCTION FOR SLAVE MODE

| Pin<br>(Abbre-<br>viation)                                   | 52-pin<br>QFP<br>Pin No.                           | 40-pin<br>DIP<br>Pin No.                           | I/O     | Function                                                                                                                         |

|--------------------------------------------------------------|----------------------------------------------------|----------------------------------------------------|---------|----------------------------------------------------------------------------------------------------------------------------------|

| 10<br>11<br>12<br>13<br>14<br>15<br>16<br>17                 | 11<br>12<br>15<br>16<br>17<br>18<br>19<br>21       | 4<br>5<br>7<br>8<br>9<br>10<br>11                  | Input   | Invalid.<br>Set at high or low level.                                                                                            |

| AEN/WR                                                       | 22                                                 | 12                                                 | Output/ | Inputs write strobe signal for a speech synthesis data.                                                                          |

| SAA                                                          | 23                                                 | 13                                                 | Output  | Invalid.<br>Leave this pin open.                                                                                                 |

| ALE                                                          | 25                                                 | 15                                                 | Output  | Invalid.<br>Leave this pin open.                                                                                                 |

| MD                                                           | 34                                                 | 21                                                 | Input   | Slave mode selection input.<br>Transition between two operation mode is not accepted<br>during synthesis or in the standby mode. |

| ST                                                           | 35                                                 | 22                                                 | Input   | Invalid.<br>Set at high level.                                                                                                   |

| cs                                                           | 38                                                 | 25                                                 | Input   | Chip select signal input. $\overline{\text{WR}}$ becomes valid when $\overline{\text{CS}}$ goes low.                             |

| A0<br>A1<br>A2<br>A3<br>A4<br>A5<br>A6<br>A7<br>A8           | 41<br>42<br>43<br>44<br>45<br>47<br>48<br>49<br>50 | 26<br>27<br>28<br>29<br>30<br>31<br>32<br>33<br>34 | Output  | Invalid.<br>Leave these pins open.                                                                                               |

| ASD0<br>ASD1<br>ASD2<br>ASD3<br>ASD4<br>ASD5<br>ASD6<br>ASD7 | 51<br>2<br>3<br>4<br>5<br>8<br>9<br>10             | 35<br>36<br>37<br>38<br>39<br>1<br>2<br>3          | Input   | Input speech synthesis data from an external source.                                                                             |

# 2. ELECTRICAL SPECIFICATIONS

### ABSOLUTE MAXIMUM RATINGS (Ta = 25 $^{\circ}$ C)

| Parameters            | Symbol | Conditions | Ratings                       | Unit |

|-----------------------|--------|------------|-------------------------------|------|

| Power supply voltage  | Vdd    |            | -0.3 to + 7.0                 | V    |

| Input voltage         | Vı     |            | -0.3 to V <sub>DD</sub> + 0.3 | V    |

| Output voltage        | Vo     |            | -0.3 to V <sub>DD</sub> + 0.3 | V    |

| Storage temperature   | Tstg   |            | -40 to +125                   | °C   |

| Operating temperature | Topt   |            | -10 to +70                    | °C   |

## **RECOMMENDED OPERATING CONDITIONS**

| Parameters               | Symbol | Conditions                                                                                                         | MIN.    | TYP. | MAX.    | Unit |

|--------------------------|--------|--------------------------------------------------------------------------------------------------------------------|---------|------|---------|------|

| Supply voltage           | Vdd    |                                                                                                                    | 2.7     |      | 5.5     | V    |

| High-level input voltage | VIH1   | Applied to I0 to I7, $\overline{ST}$ , $\overline{CS}$ ,<br>$\overline{RESET}$ , $\overline{MD}$ , $\overline{WR}$ | 0.7 VDD |      | Vdd     | V    |

|                          | VIH2   | Applied to ASD0 to ASD7, $V_{DD} = 5 \text{ V} \pm 10 \%$                                                          | 2.2     |      | Vdd     | V    |

| Low-level input voltage  | VIL1   | Applied to I0 to I7, $\overline{ST}$ , $\overline{CS}$ ,<br>$\overline{RESET}$ , $\overline{MD}$ , $\overline{WR}$ | 0       |      | 0.3 Vdd | V    |

| Low-level input voltage  | VIL2   | Applied to ASD0 to ASD7, $V_{DD} = 5 \text{ V} \pm 10 \%$                                                          | 0       |      | 0.8     | V    |

| Clock frequency          | fosc   |                                                                                                                    | 630     | 640  | 650     | kHz  |

Remark AC timing test voltage

$\label{eq:VIL} \begin{array}{l} \mathsf{V}_{\mathsf{IL}} = \mathsf{V}_{\mathsf{OL}} = \mathbf{0.3} \ \mathsf{V}_{\mathsf{DD}} \\ \\ \mathsf{V}_{\mathsf{IH}} = \mathsf{V}_{\mathsf{OH}} = \mathbf{0.7} \ \mathsf{V}_{\mathsf{DD}} \end{array}$

| DC CHARACTERISTICS (Ta = $-10$ to $+70$ °C, VDD = 2.7 to 5.5 V, fosc = 640 kHz) |

|---------------------------------------------------------------------------------|

|---------------------------------------------------------------------------------|

| Parameters                        | Symbol      | Conditions                                                                    | MIN.    | TYP.                 | MAX.                                                                                                              | Unit |

|-----------------------------------|-------------|-------------------------------------------------------------------------------|---------|----------------------|-------------------------------------------------------------------------------------------------------------------|------|

| High-level output voltage         | Vон         | Іон = −100 μА                                                                 |         | V <sub>DD</sub> -0.5 |                                                                                                                   | V    |

| Low-level output voltage          | Vol         | $V_{\text{DD}}$ = 5 V $\pm$ 10 %, Iol = 1.6 mA                                |         |                      | 0.4                                                                                                               | V    |

| Input leak current                | l lu l      | lo to I7, ST, CS, WR, ASD0<br>to ASD7, MD                                     |         |                      | 3                                                                                                                 | μΑ   |

| Output leak current               | <b> </b> lo | BUSY, A0 to A8                                                                |         |                      | 3                                                                                                                 | μA   |

|                                   |             | (Stand alone, slave mode)<br>V <sub>DD</sub> = 5 V                            |         |                      | 10                                                                                                                | mA   |

| Supply surrent                    | lpp         | (Standby mode)<br>V <sub>DD</sub> = 5 V                                       |         |                      | 0.4                                                                                                               | μΑ   |

| Supply current                    |             | (Stand alone, slave mode)<br>2.7 V $\leq$ V <sub>DD</sub> $\leq$ 3.5 V        |         |                      | 1                                                                                                                 | mA   |

|                                   |             | (Standby mode)<br>2.7 V ≦ V <sub>DD</sub> ≦ 3.5 V                             |         |                      | 10                                                                                                                | μΑ   |

|                                   |             | $V_{DD} = 2.7 \text{ V}, \text{ Rref} = 0 \Omega$                             | 140     | 250                  | 0.4<br>3<br>3<br>10<br>20<br>1<br>1<br>20<br>1<br>20<br>1<br>20<br>1<br>20<br>3<br>9<br>88<br>39<br>88<br>36 IREF | μΑ   |

| Reference input current Note      | IREF        | $V_{DD} = 5.5 \text{ V}, \text{ Rref} = 0 \Omega$                             | 500     | 760                  |                                                                                                                   | μΑ   |

| Reference input current Note      | IREF        | $V_{DD} = 2.7 \text{ V}, \text{ Rref} = 50 \text{ k}\Omega$                   | 21      | 30                   | 39                                                                                                                | μΑ   |

|                                   |             | $V_{DD} = 5.5 \text{ V}, \text{ Rref} = 50 \text{ k}\Omega$                   | 68      | 78                   | 88                                                                                                                | μΑ   |

| D/A converter output current      | lavo        | 2.7 V ≤ V <sub>DD</sub> ≤ 5.5 V<br>V <sub>AVO</sub> = 2.0 V, D/A input: 1 FFH | 32 Iref | 34 Iref              | 36 Iref                                                                                                           | μΑ   |

| D/A converter output leak current | I Ild I     | $0 V \leq V_{AVO} \leq V_{DD}$<br>in the standby mode                         |         |                      | 5                                                                                                                 | μΑ   |

Note Measuring circuit

### **★** AC CHARACTERISTICS (Ta = -10 to +70 °C, VDD = 2.7 to 5.5 V, fosc = 640 kHz)

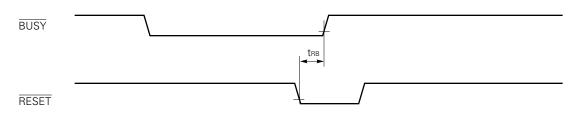

#### TIMING REQUIREMENTS (common to all modes)

| Parameters            | Symbol          | Conditions                                                            | MIN. | TYP. | MAX. | Unit |

|-----------------------|-----------------|-----------------------------------------------------------------------|------|------|------|------|

| BUSY rise time        | tr1             | $C_{\text{L}}$ = 150 pF, $V_{\text{DD}}$ = 5 V $\pm$ 10 %             |      |      | 800  | ns   |

|                       | tr2             | $C_{\text{L}}$ = 150 pF, $V_{\text{DD}}$ = 2.7 to 5.5 V               |      |      | 2    | μs   |

| BUSY fall time        | t <sub>f1</sub> | $C_{\text{L}}$ = 150 pF, $V_{\text{DD}}$ = 5 V $\pm$ 10 %             |      |      | 800  | ns   |

|                       | t <sub>f2</sub> | $C_L = 150 \text{ pF}, \text{V}_{DD} = 2.7 \text{ to } 5.5 \text{ V}$ |      |      | 2    | μs   |

| BUSY output stop time | trв             | from $\overline{\text{RESET}}\downarrow$                              |      |      | 9.5  | μs   |

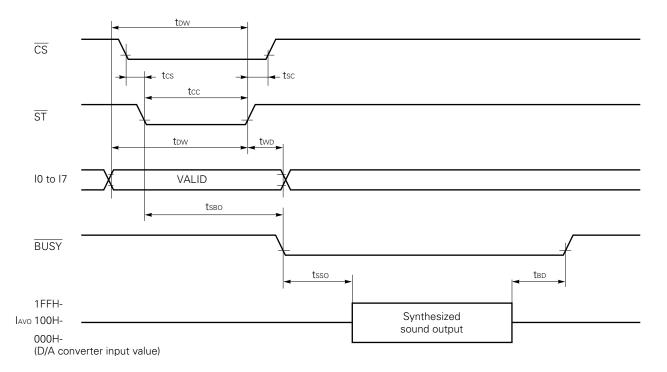

### 2.1 STAND ALONE MODE

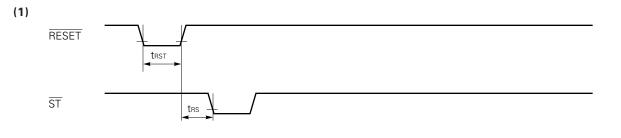

### (1) TIMING REQUIREMENTS

| Parameters                      | Symbol       | Conditions                                                        | MIN. | TYP. | MAX. | Unit |

|---------------------------------|--------------|-------------------------------------------------------------------|------|------|------|------|

| RESET pulse width               | <b>t</b> rst |                                                                   | 18.5 |      |      | μs   |

| CS set up time                  | tcs          | for $\overline{ST}\downarrow$                                     | 0    |      |      | ns   |

| CS hold time                    | tsc          | from ST ↑                                                         | 0    |      |      | ns   |

| ST set up time                  | trs          | In operation mode, from $\overline{\text{RESET}}$ $\uparrow$      | 200  |      |      | μs   |

|                                 | LKS          | In standby mode, from $\overline{\text{RESET}}$ $\uparrow$        | 1.6  |      |      | ms   |

| $\overline{ST}$ pulse width     | tcc          | $2.7 \text{ V} \leq \text{ V}_{\text{DD}} \leq 5.5 \text{ V}$     | 2    |      |      | μs   |

|                                 | icc          | $4.5 \text{ V} \leq \text{V}_{\text{DD}} \leq 5.5 \text{ V}$      | 350  |      |      | ns   |

| Message select code set up time | tow          | 2.7 V $\leq$ V <sub>DD</sub> $\leq$ 5.5 V, from ST ↑              | 5    |      |      | μs   |

|                                 | LDVV         | 4.5 V $\leq$ V <sub>DD</sub> $\leq$ 5.5 V, from $\overline{ST}$ ↑ | 350  |      |      | ns   |

| Message select code hold time   | two          | from ST ↑                                                         | 0    |      |      | ns   |

| Speech data set up time         | <b>t</b> dr  | for $\overline{DRQ}\downarrow$                                    | 2    |      | 7.5  | μs   |

| Speech data hold time           | trdh         | from DRQ 1                                                        |      |      | 1.25 | μs   |

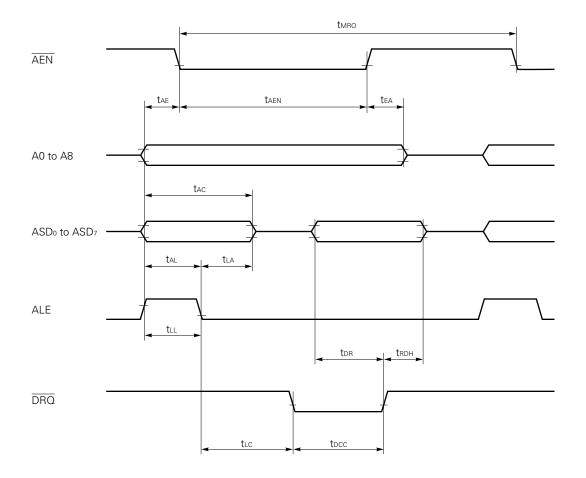

| Parameters                 | Symbol       | Conditions                                                  | MIN. | TYP. | MAX. | Unit |

|----------------------------|--------------|-------------------------------------------------------------|------|------|------|------|

| BUSY output delay          | tsвo         | In operation mode, from $\overline{\mathrm{ST}}\downarrow$  |      | 6.25 | 10   | μs   |

| Speech output delay        | tsso         | In operation mode, from $\overline{	extsf{BUSY}}\downarrow$ |      | 2.1  | 2.2  | ms   |

| BUSY hold time             | <b>t</b> BD  | from synthesis                                              |      |      | 15   | μs   |

| ALE pulse width            | tu           |                                                             |      | 3.13 |      | μs   |

| Higher address set up time | tal          | for ALE $\downarrow$                                        |      | 3.13 |      | μs   |

|                            | <b>t</b> AE  | for $\overline{AEN} \downarrow$                             |      | 0    |      | μs   |

| Higher address hold time   | tla          | from ALE $\downarrow$                                       |      | 3.13 |      | μs   |

|                            | tεΑ          | from AEN ↑                                                  |      | 0    |      | μs   |

| AEN pulse width            | <b>t</b> AEN |                                                             |      | 14.1 |      | μs   |

| DRQ output delay           | t∟c          | from ALE $\downarrow$                                       |      | 3.13 |      | μs   |

| Higher address pulse width | tac          |                                                             |      | 6.25 |      | μs   |

| DRQ pulse width            | tDCC         |                                                             |      | 7.81 |      | μs   |

| ROM read cycle time        | tмro         |                                                             |      | 37.5 |      | μs   |

# (2) SWITCHING CHARACTERISTICS

# TIMING CHART (at reset)

(2)

### TIMING CHART (Stand alone mode)

(1) CONTROL

## (2) MEMORY ACCESS

$\star$

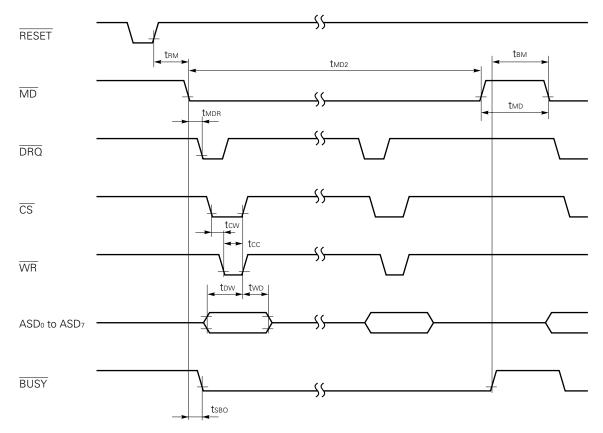

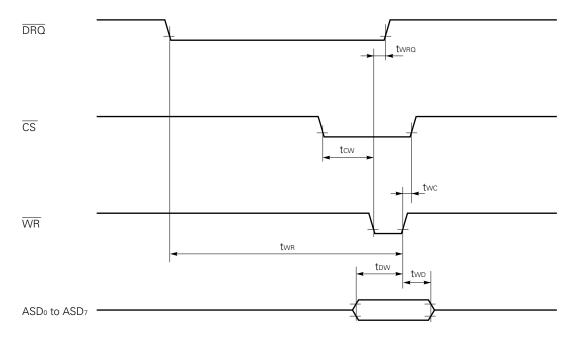

# 2.2 SLAVE MODE

### (1) TIMING REQUIREMENTS

| Parameters              | Symbol | Conditions                                              | MIN. | TYP. | MAX. | Unit |

|-------------------------|--------|---------------------------------------------------------|------|------|------|------|

|                         | trм    | from RESET ↑                                            | 200  |      |      | μs   |

| MD set up time          | tвм    | from BUSY ↑                                             | 0    |      |      | ns   |

|                         | tмd    | from MD ↑                                               | 6.2  |      |      | μs   |

| MD pulse width          | tmd2   |                                                         | 6.2  |      |      | μs   |

| Speech data set up time | tow    | for $\overline{\text{WR}}$ $\uparrow$ , 5 V ± 10 %      | 350  |      |      | ns   |

| Speech data hold time   | two    | from $\overline{\text{WR}}$ $\uparrow$ , 5 V $\pm$ 10 % | 0    |      |      | ns   |

| WR input stop time      | twr    | from $\overline{DRQ}\downarrow$                         |      |      | 31.7 | μs   |

| WR pulse width          | tcc    | 5 V ± 10 %                                              | 350  |      |      | ns   |

| CS set up time          | tcw    | for $\overline{WR}\downarrow$                           | 0    |      |      | ns   |

| CS hold time            | twc    | from WR ↑                                               | 0    |      |      | ns   |

# (2) SWITCHING CHARACTERISTICS

| Parameters           | Symbol       | Conditions                                                                                    | MIN. | TYP. | MAX.  | Unit |

|----------------------|--------------|-----------------------------------------------------------------------------------------------|------|------|-------|------|

| BUSY output delay    | tsвo         | from $\overline{\text{MD}}\downarrow$                                                         |      |      | 9.5   | μs   |

|                      |              | In operation mode, from $\overline{\text{MD}}\downarrow$                                      | 50   |      | 70    |      |

| DRQ output delay     | <b>t</b> mdr | In standby mode, after $\overline{\text{RESET}}$ input, from $\overline{\text{MD}}\downarrow$ | 50   |      | 50000 | μs   |

| DRQ output stop time | twro         | from $\overline{WR}\downarrow$                                                                |      |      | 3     | μs   |

$\star$

#### TIMING CHART (Slave mode)

### (1) CONTROL

### (2) DATA TRANSFER

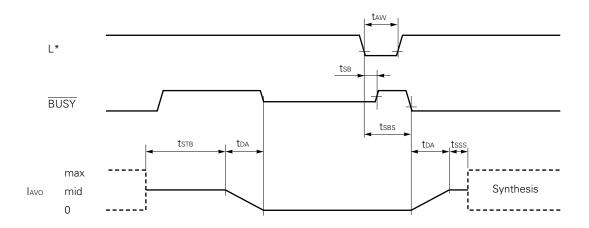

### 2.3 STANDBY MODE

#### (1) TIMING REQUIREMENTS

| Parameters                                              | Symbol | Conditions                                      | MIN. | TYP. | MAX. | Unit |

|---------------------------------------------------------|--------|-------------------------------------------------|------|------|------|------|

| Standby escape signal<br>L <sup>*Note</sup> pulse width | taw    | $V_{\text{DD}} = 5 \text{ V} \pm 10 \text{ \%}$ | 350  |      |      | ns   |

#### (2) SWITCHING CHARACTERISTICS

| Parameters                                 | Symbol | Conditions                                           | MIN. | TYP. | MAX. | Unit |

|--------------------------------------------|--------|------------------------------------------------------|------|------|------|------|

| Operation mode hold time                   | tsтв   | after synthesis                                      |      | 2.9  | 3    | s    |

| D/A converter activate<br>/inactivate time | tda    |                                                      |      | 46.5 | 47   | ms   |

| BUSY set up time                           | tsв    | from L* ↓                                            |      | 6.25 | 10   | μs   |

| Synthesis start time                       | tsss   | after D/A converter activation                       |      | 2.1  | 2.2  | ms   |

| BUSY output delay                          | tsbs   | In standby mode, oscillation start time is included. |      | 4    | 80   | ms   |

**Note** L\*: Signal to release standby mode.

$= \begin{cases} \overline{CS} \land \overline{ST} &: \text{ When operation mode is stand alone mode.} \\ \overline{CS} \land \overline{WR} &: \text{ When operation mode is slave mode} \end{cases}$

#### TIMING CHART (Standby mode)

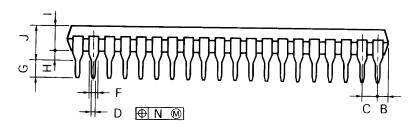

3. PACKAGE DRAWINGS

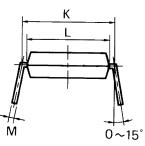

# 40PIN PLASTIC DIP (600 mil)

P40C-100-600A

#### NOTES

- Each lead centerline is located within 0.25 mm (0.01 inch) of its true position (T.P.) at maximum material condition.

- Item "K" to center of leads when formed parallel.

| ITEM | MILLIMETERS            | INCHES                            |

|------|------------------------|-----------------------------------|

| А    | 53.34 MAX.             | 2.100 MAX.                        |

| В    | 2.54 MAX.              | 0.100 MAX.                        |

| С    | 2.54 (T.P.)            | 0.100 (T.P.)                      |

| D    | 0.50 <sup>±0.10</sup>  | $0.020 \stackrel{+0.004}{-0.005}$ |

| F    | 1.2 MIN.               | 0.047 MIN.                        |

| G    | 3.6 <sup>±0.3</sup>    | $0.142^{\pm 0.012}$               |

| н    | 0.51 MIN.              | 0.020 MIN.                        |

| 1    | 4.31 MAX.              | 0.170 MAX.                        |

| J    | 5.72 MAX.              | 0.226 MAX.                        |

| к    | 15.24 (T.P.)           | 0.600 (T.P.)                      |

| L    | 13.2                   | 0.520                             |

| М    | $0.25^{+0.10}_{-0.05}$ | 0.010+0.004<br>-0.003             |

| Ν    | 0.25                   | 0.01                              |

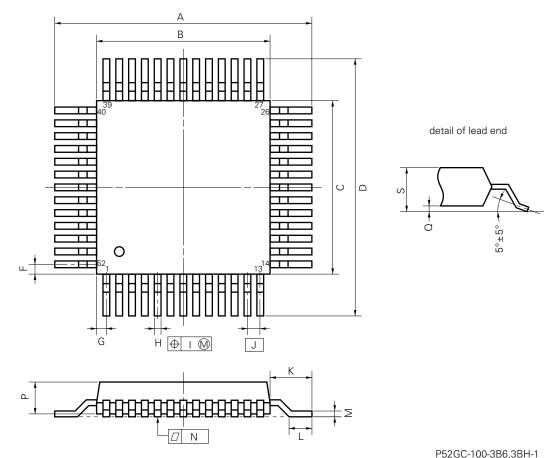

# ★ 52 PIN PLASTIC QFP (□14)

NOTE

Each lead centerline is located within 0.20 mm (0.008 inch) of its true position (T.P.) at maximum material condition.

| ITEM | MILLIMETERS            | INCHES                           |

|------|------------------------|----------------------------------|

|      |                        |                                  |

| A    | 17.6±0.4               | 0.693±0.016                      |

| В    | 14.0±0.2               | $0.551^{+0.009}_{-0.008}$        |

| С    | 14.0±0.2               | $0.551^{+0.009}_{-0.008}$        |

| D    | 17.6±0.4               | 0.693±0.016                      |

| F    | 1.0                    | 0.039                            |

| G    | 1.0                    | 0.039                            |

| Н    | 0.40±0.10              | $0.016\substack{+0.004\\-0.005}$ |

| I    | 0.20                   | 0.008                            |

| J    | 1.0 (T.P.)             | 0.039 (T.P.)                     |

| K    | 1.8±0.2                | $0.071^{+0.008}_{-0.009}$        |

| L    | 0.8±0.2                | 0.031+0.009                      |

| М    | $0.15^{+0.10}_{-0.05}$ | 0.006 <sup>+0.004</sup> -0.003   |

| N    | 0.12                   | 0.005                            |

| Р    | 2.7                    | 0.106                            |

| Q    | 0.1±0.1                | 0.004±0.004                      |

| S    | 3.0 MAX.               | 0.119 MAX.                       |

### 4. RECOMMENDED SOLDERING CONDITIONS

The following conditions (see tables below) must be met when soldering the  $\mu$ PD7759. Please consult with our sales offices in case other soldering process is used, or in case soldering is done under different conditions.

For more details, refer to our document "SEMICONDUCTOR DEVICE MOUNTING TECHNOLOGY MANUAL" (IEI-1207).

#### **O TYPE OF SURFACE MOUNT DEVICE**

#### $\mu$ PD7759GC-3BH:52-pin plastic QFP ( $\Box$ 14 mm)

| Soldering Process      | Soldering Conditions                                                                                                                                                            | Symbol    |

|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| Wave Soldering         | Solder temperature: 260 °C or below,<br>Flow time: 10 seconds or below,<br>Temperature of pre-heat: 120 °C or below (Plastic surface temperature),<br>Number of flow process: 1 | WS60-00-1 |

| Infrared Ray Reflow    | Peak package's surface temperature: 230 °C or below,<br>Reflow time: 30 seconds or below (210 °C or higher),<br>Number of reflow process: 1                                     | IR30-00-1 |

| VPS                    | Peak package's temperature: 215 °C or below,<br>Reflow time: 40 seconds or below (200 °C or higher),<br>Number of reflow process: 1                                             | VP15-00-1 |

| Partial Heating Method | Terminal temperature: 300 °C or below,<br>Time: 3 seconds or below (Per one side of the device)                                                                                 | _         |

Caution Do not apply more than one soldering method at any one time, except for "Partial heating method".

# $\odot\,$ Type of through hole device

#### $\mu \text{PD7759C:40-pin}$ plastic DIP (600mil)

| Soldering Process                  | Soldering Conditions                                                  |

|------------------------------------|-----------------------------------------------------------------------|

| Wave Soldering<br>(only lead part) | Solder Temperature: 260 °C or below<br>Flow time: 10 seconds or below |

| Partial Heating Method             | Terminal temperature: 260 °C or below<br>Time: 10 seconds or below    |

Caution Do not jet molten solder on the surface of package.

The  $\mu \text{PD7759}$  has the following user's manual as a separate volume.

Please use it for reference.

• μPD7755 family User's Manual: IEU-1218

No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Corporation. NEC Corporation assumes no responsibility for any errors which may appear in this document.

NEC Corporation does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from use of a device described herein or any other liability arising from use of such device. No license, either express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC Corporation or others.

The devices listed in this document are not suitable for use in aerospace equipment, submarine cables, nuclear reactor control systems and life support systems. If customers intend to use NEC devices for above applications or they intend to use "Standard" quality grade NEC devices for applications not intended by NEC, please contact our sales people in advance.

Application examples recommended by NEC Corporation

Standard: Computer, Office equipment, Communication equipment, Test and Measurement equipment, Machine tools, Industrial robots, Audio and Visual equipment, Other consumer products, etc.

Special: Automotive and Transportation equipment, Traffic control systems, Antidisaster systems, Anticrime systems, etc.