**TENTATIVE**

TOSHIBA CCD LINEAR IMAGE SENSOR CCD(Charge Coupled Device)

# TCD1502C

The TCD1502C is a high sensitive and low dark current 5000 elements CCD image sensor.

The sensor is designed for facsimile, imagescanner and OCR.

The device contains a row of 5000 elements photodiodes which provide a 16 lines/mm (400DPI) across a A3 size paper. The device is operated by 5V (pulse), and 12V power supply.

### **FEATURES**

Number of Image Sensing Elements: 5000 elements

Image Sensing Element Size

:  $7\mu \text{m}$  by  $7\mu \text{m}$  on  $7\mu \text{m}$  centers

Photo Sensing Region : High sensitive and low voltage

dark signal pn photodiode

Clock : 2 phase (5V)Package : 22pin DIP

Weight: 5.4g (Typ.)

### **MAXIMUM RATINGS** (Note 1)

| CHARACTERISTIC        | SYMBOL           | RATING         | UNIT |

|-----------------------|------------------|----------------|------|

| Clock Pulse Voltage   | Vφ               |                | ٧    |

| Shift Pulse Voltage   | V <sub>SH</sub>  | -0.3~8         |      |

| Reset Pulse Voltage   | VRS              | 0.5            |      |

| Clamp Pulse Voltage   | VCP              |                |      |

| Power Supply Voltage  | V <sub>OD</sub>  | -0.3~15        |      |

| Operating Temperature | T <sub>opr</sub> | - 25~60        | °C   |

| Storage Temperature   | T <sub>stg</sub> | <b>-40∼100</b> | °C   |

(Note 1) All voltage are with respect to SS terminals (Ground).

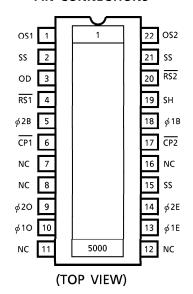

### **PIN CONNECTIONS**

#### 961001EBA2

● TOSHIBA is continually working to improve the quality and the reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to observe standards of safety, and to avoid situations in which a malfunction or failure of a TOSHIBA product could cause loss of human life, bodily injury or damage to property. In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent products specifications. Also, please keep in mind the precautions and conditions set forth in the TOSHIBA Semiconductor Reliability Handbook.

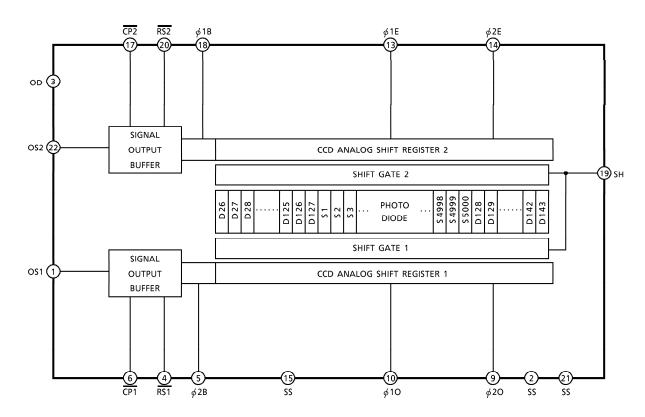

### **CIRCUIT DIAGRAM**

### **PIN NAME**

| φ1E, O        | Clock (Phase 1)             |

|---------------|-----------------------------|

| φ2E, <b>O</b> | Clock (Phase 2)             |

| φIB           | Final Stage Clock (Phase 1) |

| <i>∲</i> 2B   | Final Stage Clock (Phase 2) |

| SH            | Shift Gate                  |

| RS            | Reset Gate                  |

| СР            | Clamp Gate                  |

| OS1           | Signal Output 1             |

| OS2           | Signal Output 2             |

| OD            | Power                       |

| SS            | Ground                      |

| NC            | Non Connection              |

961001EBA2'

The products described in this document are subject to foreign exchange and foreign trade control laws.

The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA CORPORATION for any infringements of intellectual property or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any intellectual property or other rights of TOSHIBA CORPORATION or others.

The information contained herein is subject to change without notice.

### **OPTICAL / ELECTRICAL CHARACTERISTICS**

(Ta = 25°C,  $V_{OD}$  = 12V,  $V_{\phi}$  =  $V_{\overline{SS}}$  =  $V_{\overline{CP}}$  = 5V,  $f_{\phi}$  = 1MHz,  $t_{INT}$  (INTEGRATION TIME) = 10ms, LIGHT SOURCE = DAYLIGHT FLUORESCENT LAMP, LOAD RESISTANCE = 100k $\Omega$ )

| CHARACTERISTIC                | SYMBOL           | MIN.     | TYP. | MAX. | UNIT                                  | NOTE     |

|-------------------------------|------------------|----------|------|------|---------------------------------------|----------|

| Sensitivity                   | R                | 7.2      | 9    | 10.8 | V/lx·s                                |          |

| Photo Response Non Uniformity | PRNU             | _        | _    | 10   | %                                     | (Note 2) |

|                               | PRNU (3)         | <u> </u> | 4    | 8    | mV                                    | (Note 8) |

| Saturation Output Voltage     | V <sub>SAT</sub> | 1.5      | 2    | _    | V                                     | (Note 3) |

| Saturation Exposure           | SE               | 0.14     | 0.22 | _    | lx•s                                  | (Note 4) |

| Dark Signal Voltage           | VDRK             | _        | 1    | 2.5  | mV                                    | (Note 5) |

| Dark Signal Non Uniformity    | DSNU             | _        | 1    | 2.5  | mV                                    | (Note 5) |

| DC Power Dissipation          | PD               | _        | 300  | 364  | mW                                    |          |

| Total Transfer Efficiency     | TTE              | 92       | _    | _    | %                                     |          |

| Output Impedance              | Z <sub>O</sub>   | _        | 0.5  | 1    | kΩ                                    |          |

| Dynamic Range                 | DR               | _        | 2000 | _    | _                                     | (Note 6) |

| DC Signal Output Voltage      | Vos1             | 3.5      | 4.5  | 6    | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ | (Nets 7) |

|                               | V <sub>OS2</sub> | 3.5      | 4.5  | 6    | V                                     | (Note 7) |

| DC Differential Error Voltage | VOS1-VOS2        | <b> </b> | _    | 300  | mV                                    |          |

(Note 2) Measured at 50% of SE (Typ.)

Definition of PRNU : PRNU =  $-\frac{\Delta \chi}{\overline{\chi}}$  × 100 (%)

Where  $\overline{\chi}$  is average of total signal outputs and  $\Delta\chi$  is maximum deviation from  $\overline{\chi}$  under uniform illumination. (Channel 1)

In the case of 2500 elements (Channel 2), the condition is the same as above too.

(Note 3) V<sub>SAT</sub> is defined as minimum saturation output voltage of all effective pixels.

(Note 4) Definition of SE : SE =

$$\frac{V_{SAT}}{R}$$

(Ix·s)

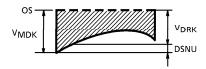

(Note 5)  $V_{DRK}$  is defined as average dark signal voltage of all effective pixels. DSNU is defined as different voltage between  $V_{DRK}$  and  $V_{MDK}$  when  $V_{MDK}$  is maximum dark signal voltage.

(Note 6) Definition of DR : DR =  $\frac{V_{SAT}}{V_{DRK}}$

$V_{DRK}$  is proportional to  $t_{INT}$  (Integration Time). So the shorter  $t_{INT}$  condition makes wider DR values.

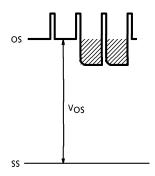

(Note 7) DC signal output voltage and DC compensation output voltage are defined as follows:

(Note 8) PRNU (3) is defined as maximum voltage with next pixel, where measured 5% of SE (Typ.)

### **OPERATING CONDITION**

| CHARACTERISTIC            |           | SYMBOL           | MIN. | TYP. | MAX. | UNIT |

|---------------------------|-----------|------------------|------|------|------|------|

| Clock Pulse Voltage       | "H" Level | V¢1E, O          | 4.5  | 5    | 5.5  | V    |

|                           | "L" Level | $V_{\phi}$ 2E, O | 0    | _    | 0.5  | V    |

| Final Stage Clock Voltage | "H" Level | V                | 4.5  | 5    | 5.5  | >    |

|                           | "L" Level | Vø2B             | 0    | _    | 0.5  | V    |

| Shift Pulse Voltage       | "H" Level | Vari             | 4.5  | 5    | 5.5  | >    |

|                           | "L" Level | V <sub>SH</sub>  | 0    | _    | 0.5  | V    |

| Reset Pulse Voltage       | "H" Level | V <sub>RS1</sub> | 4.5  | 5    | 5.5  | ٧    |

|                           | "L" Level | V <del>RS2</del> | 0    | _    | 0.5  | V    |

| Clamp Pulse Voltage       | "H" Level | V <del>CP1</del> | 4.5  | 5    | 5.5  | V    |

|                           | "L" Level | V <del>CP2</del> | 0    | _    | 0.5  | V    |

| Power Supply Voltage      |           | V <sub>OD</sub>  | 11.4 | 12.0 | 13.0 | V    |

### **CLOCK CHARACTERISTICS** (Ta = 25°C)

| CHARACTERISTIC                | SYMBOL          | MIN. | TYP. | MAX. | UNIT |

|-------------------------------|-----------------|------|------|------|------|

| Clock Pulse Frequency         | fø              | _    | 1    | 10   | MHz  |

| Reset Pulse Frequency         | fRS             | _    | 1    | 10   | MHz  |

| Clark Compaitons              | C∳E             | _    | 350  | 450  | pF   |

| Clock Capacitance             | C∮O             |      | 350  | 450  |      |

| Final Stage Clock Capacitance | C∮B             | _    | 10   | 20   | pF   |

| Shift Gate Capacitance        | C <sub>SH</sub> |      | 10   | 20   | рF   |

| Reset Gate Capacitance        | CRS             | _    | 10   | 20   | рF   |

| Clamp Gate Capacitance        | CCP             | _    | 10   | 20   | pF   |

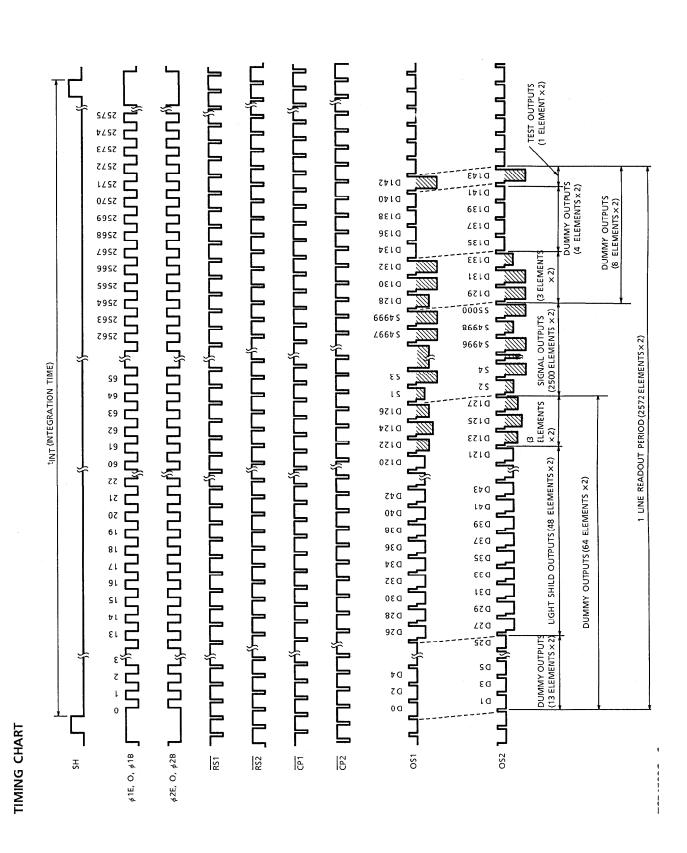

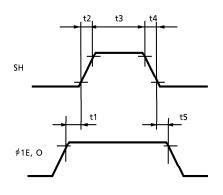

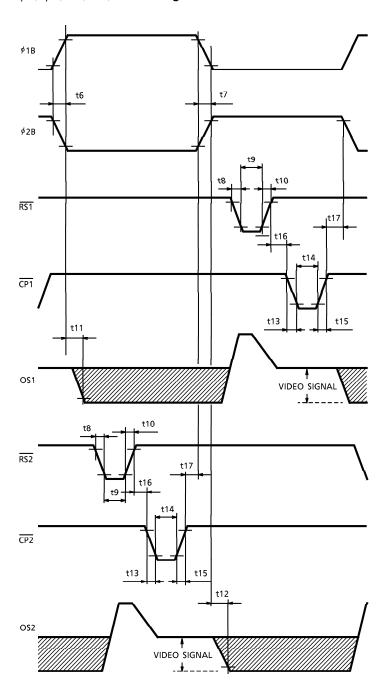

### TIMING REQUIREMENTS

SH,  $\phi$ 1 Timing

$\phi$ 1,  $\phi$ 2,  $\overline{RS}$ ,  $\overline{CP}$ , OS Timing

| CHARACTERISTIC                                           | SYMBOL   | MIN. | TYP.<br>(Note 9) | MAX. | UNIT |

|----------------------------------------------------------|----------|------|------------------|------|------|

| Pulse Timing of SH and $\phi$ 10, E                      | t1, t5   | 100  | 300              | _    | ns   |

| SH Pulse Rise Time, Fall Time                            | t2, t4   | 0    | 50               | _    | ns   |

| SH Pulse Width                                           | t3       | 500  | 1000             | _    | ns   |

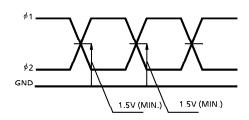

| $\phi$ 1, $\phi$ 2 Pulse Rise Time, Fall Time            | t6, t7   | 0    | 100              | _    | ns   |

| RS Pulse Rise Time, Fall Time                            | t8, t10  | 0    | 20               | _    | ns   |

| RS Pulse Width                                           | t9       | 20   | 250              |      | ns   |

| Video Data Delay Time (Note 10)                          | t11, t12 | _    | 20               | _    | ns   |

| CP Pulse Rise Time, Fall Time                            | t13, t15 | 0    | 20               | _    | ns   |

| CP Pulse Width                                           | t14      | 20   | _                | _    | ns   |

| Pulse Timing of RS and CP                                | t16      | 0    | _                | _    | ns   |

| Pulse Timing of $\phi$ 1B, $\phi$ 2B and $\overline{CP}$ | t17      | 0    | _                | _    | ns   |

(Note 9) TYP. is the case of fRS = 1.0MHz (Note 10) Load Resistance is  $100k\Omega$

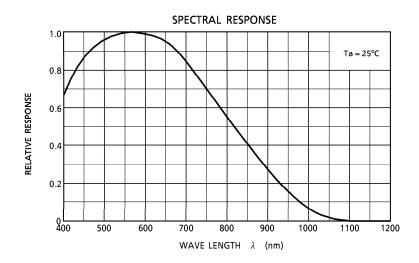

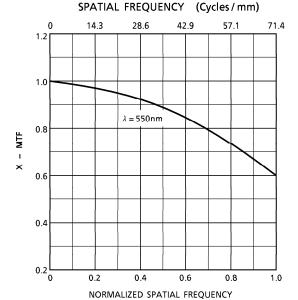

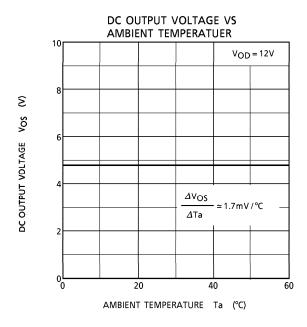

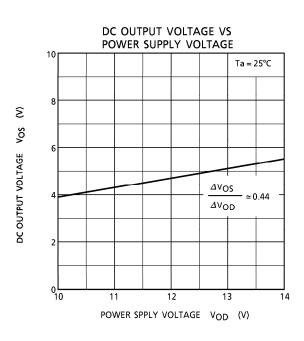

### **TYPICAL PERFORMANCE CURVES**

MODULATION TRANSFER FUNCTION OF X-DIRECTION

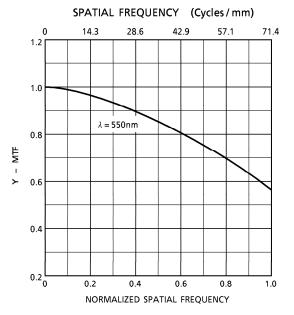

## MODULATION TRANSFER FUNCTION OF Y-DIRECTION

### TYPICAL PERFORMANCE CURVES (Cont'd)

#### **CAUTION**

### 1. Window Glass

The dust and stain on the glass window of the package degrade optical performance of CCD sensor. Keep the glass window clean by saturating a cotton swab in alcohol and lightly wiping the surface, and allow the glass to dry by blowing with filtered dry N<sub>2</sub>.

Care should be taken to avoid mechanical or thermal shock because the glass window is easily to damage.

### 2. Electrostatic Breakdown

Store in shorting clip or in conductive foam to avoid electrostatic breakdown.

### 3. Incident Light

CCD sensor is sensitive to infrared light.

Note that infrared light component degrades resolution and PRNU of CCD sensor.

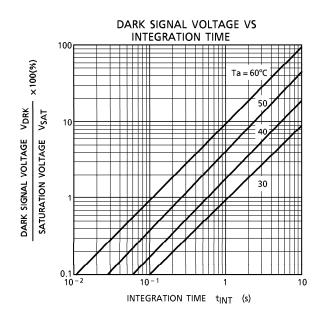

### **PACKAGE OUTLINE**

WDIP22-C-400-2.54B (A)

Unit in mm

(Note 1) No. 1 SENSOR ELEMENT (S1) TO EDGE OF PACKAGE.

(Note 2) TOP OF CHIP TO BOTTOM OF PACKAGE.

(Note 3) GLASS THICKNES (n = 1.5)

Weight: 5.4g (Typ.)