### **OVERVIEW**

The SM5829P is a variable-length shift register fabricated in Molybdenum-gate CMOS. The length can be set to any value between 2 and 129.

The SM5829P features a maximum operating frequency of 25.0 MHz (2 to 65 steps) and 33.3 MHz (66 to 129 steps), and static registers for data retention during periods when the shift clock is halted, making it ideal for digital video processing and similar applications.

## FEATURES

- 2- to 129-step selectable length

- 8-bit (1-byte) parallel input/output

- Uses static registers

- 33.3 MHz (max) operating frequency (66 to 129 steps) and 25.0 MHz (max) operating frequency (2 to 65 steps)

- Shift rotate/non-rotate select function

- · Data reset function

- TTL-compatible input/outputs

- 5 ±0.25 V power supply

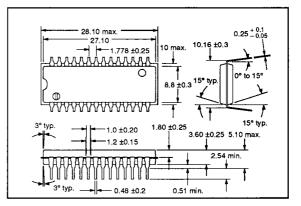

- 30-pin shrink DIP

- Molybdenum-gate CMOS process

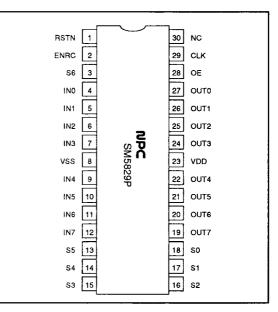

## PINOUT

SM5829P

## PACKAGE DIMENSIONS

Unit: mm

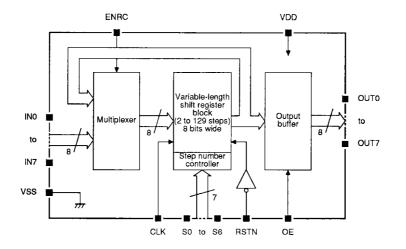

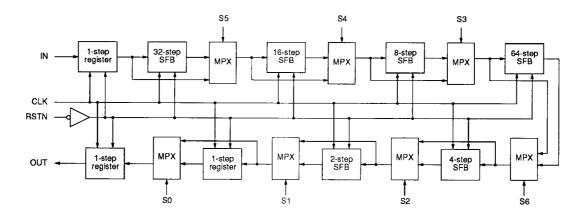

## **BLOCK DIAGRAM**

## **PIN DESCRIPTION**

| Number | Name | ١⁄٥ | Description                      |  |  |  |

|--------|------|-----|----------------------------------|--|--|--|

| 1      | RSTN | I   | Data reset                       |  |  |  |

| 2      | ENRC | I   | Data rotation control            |  |  |  |

| 3      | S6   | I   | Register step select bit 6 (MSB) |  |  |  |

| 4      | INO  | l   | Data input bit 0 (LSB)           |  |  |  |

| 5      | IN1  | l   | Data input bit 1                 |  |  |  |

| 6      | IN2  | I   | Data input bit 2                 |  |  |  |

| 7      | IN3  | I   | Data input bit 3                 |  |  |  |

| 8      | VSS  |     | Ground (0 V)                     |  |  |  |

| 9      | IN4  | I   | Data input bit 4                 |  |  |  |

| 10     | IN5  | I   | Data input bit 5                 |  |  |  |

| 11     | IN6  | I   | Data input bit 6                 |  |  |  |

| 12     | IN7  | I   | Data input bit 7                 |  |  |  |

| 13     | S5   | I   | Register step select bit 5       |  |  |  |

| 14     | S4   | ļ   | Register step select bit 4       |  |  |  |

| 15     | S3   | I   | Register step select bit 3       |  |  |  |

| 16     | S2   | I   | Register step select bit 2       |  |  |  |

| 17     | S1   |     | Register step select bit 1       |  |  |  |

| 18     | SO   | 1   | Register step select bit 0 (LSB) |  |  |  |

| 19     | OUT7 | 0   | Data output bit 7                |  |  |  |

| 20     | OUT6 | 0   | Data output bit 6                |  |  |  |

| 21     | OUT5 | 0   | Data output bit 5                |  |  |  |

| 22     | OUT4 | 0   | Data output bit 4                |  |  |  |

| 23     | VDD  |     | 5 V (typ) supply                 |  |  |  |

| 24     | OUT3 | 0   | Data output bit 3                |  |  |  |

NIPPON PRECISION CIRCUITS-2

#### SM5829P

| Number | Name | I/O | Description             |  |  |  |

|--------|------|-----|-------------------------|--|--|--|

| 25     | OUT2 | 0   | Data output bit 2       |  |  |  |

| 26     | OUT1 | 0   | Data output bit 1       |  |  |  |

| 27     | OUTO | 0   | Data output bit 0 (LSB) |  |  |  |

| 28     | OE   | -   | Output enable           |  |  |  |

| 29     | CLK  | I   | Clock input             |  |  |  |

| 30     | NC   |     | No connection           |  |  |  |

## SPECIFICATIONS

## **Absolute Maximum Ratings**

$V_{ss} = 0 V$

| Parameter                 | Symbol           | Rating                       | Unit   |

|---------------------------|------------------|------------------------------|--------|

| Supply voltage range      | V <sub>DD</sub>  | 0.3 to 7.0                   | V      |

| Input voltage range       | Vin              | -0.3 to V <sub>DD</sub> +0.3 | V      |

| Power dissipation         | PD               | 750                          | mW     |

| Storage temperature range | T <sub>stg</sub> | -40 to 125                   | deg. C |

| Soldering temperature     | T <sub>sld</sub> | 255                          | deg. C |

| Soldering time            | tsid             | 10                           | s      |

## **Recommended Operating Conditions**

$V_{ss} = 0 V$

| Parameter                   | Symbol          | Rating       | Unit   |

|-----------------------------|-----------------|--------------|--------|

| Supply voltage              | V <sub>DD</sub> | 4.75 to 5.25 | V      |

| Operating temperature range | Topr            | 20 to 70     | deg. C |

## **DC Electrical Characteristics**

$T_a = -20$  to 70 deg. C,  $V_{DD} = 4.75$  to 5.25 V,  $V_{SS} = 0$  V unless otherwise noted

| Parameter                                                                   | Symbol Condition |                              |     | Unit        |     |      |  |

|-----------------------------------------------------------------------------|------------------|------------------------------|-----|-------------|-----|------|--|

| Falameter                                                                   | Symbol           | Condition                    | min | min typ max |     | onin |  |

| Standby supply current                                                      | Ist              | $V_{DD} = 5.25 V$            | -   | 1           | 100 | μA   |  |

| Operating current consumption                                               | lod              |                              | _   | _           | 110 | mA   |  |

| IN0 to IN7, S0 to S6, ENRC,<br>CLK, RSTN and OE HIGH-level<br>input voltage | VIH              | See note 1.                  | 2.4 |             | _   | ٧    |  |

| INO to IN7, S0 to S6, ENRC,<br>CLK, RSTN and OE LOW-level<br>input voltage  | VIL              | See note 1.                  |     | -           | 0.5 | v    |  |

| OUT0 to OUT7 HIGH-level output voltage                                      | V <sub>OH</sub>  | юн = -0.4 mA.<br>See note 2. | 2.5 | -           | -   | v    |  |

| S | M5 | 82 | 9 | Ρ |

|---|----|----|---|---|

|---|----|----|---|---|

| Parameter                                                                | Symbol          | Condition                                        | Rating |     |     | - Unit |

|--------------------------------------------------------------------------|-----------------|--------------------------------------------------|--------|-----|-----|--------|

| r aranneter                                                              | Symbol          | Condition                                        | min    | typ | max |        |

| OUT0 to OUT7 LOW-level output voltage                                    | VoL             | lo <sub>L</sub> = 1.6 mA.<br>See note 2.         | -      | _   | 0.4 | v      |

| INO to IN7, S0 to S6, ENRC,<br>CLK, RSTN and OE input current            | Ι <sub>IL</sub> | V <sub>IN</sub> = 0 V. See note 1.               | _      | 10  | 20  | μΑ     |

| INO to IN7, S0 to S6, ENRC,<br>CLK, RSTN and OE input leakage<br>current | եր              | $V_{IN} = V_{DD}$ . See note 1.                  | _      | _   | 1   | μА     |

| OUT0 to OUT7 high-impedance<br>output HIGH-level leakage current         | lzH             | V <sub>OUT</sub> = V <sub>DD</sub> . See note 2. | _      | -   | 5   | μΑ     |

| OUT0 to OUT7 high-impedance<br>output LOW-level leakage current          | IzL             | V <sub>OUT</sub> = 0 V. See note 2.              | -      | -   | 5   | μΑ     |

#### Notes

1. Pins INO to IN7, S0 to S6, ENRC, CLK, RSTN and OE are inputs with internal pull-up resistances.

2. Pins OUT0 to OUT7 are tristate outputs.

## **AC Electrical Characteristics**

$T_a$  = -20 to 70 deg. C,  $V_{DD}$  = 4.75 to 5.25 V,  $V_{SS}$  = 0 V unless otherwise noted

| Parameter                                               | Symbol               | Condition                                        |     | Rating  |      | Unit  |

|---------------------------------------------------------|----------------------|--------------------------------------------------|-----|---------|------|-------|

|                                                         | Symbol               | Condition                                        | min | min typ |      |       |

| Clock frequency (2 to 65 steps)                         |                      | V <sub>IH</sub> = 2.4 V, V <sub>II</sub> = 0.5 V | -   | -       | 25.0 | N411- |

| Clock frequency (66 to 129 steps)                       | fclk                 | $V_{\rm H} = 2.4  V,  V_{\rm IL} = 0.5  V$       | _   | -       | 33.3 | MHz   |

| Clock rise time                                         | t <sub>or</sub>      |                                                  | _   | _       | 100  | ns    |

| Clock fall time                                         | tcf                  |                                                  | _   | -       | 100  | ns    |

| Clock HIGH-level pulsewidth                             | twн                  |                                                  | 13  | -       | -    | ns    |

| Clock LOW-level pulsewidth                              | twL                  |                                                  | 13  | -       | _    | ns    |

| INO to IN7 input setup time                             | ts1                  |                                                  | 13  | _       | -    | ns    |

| S0 to S6 input setup time                               | ts2                  |                                                  | 50  | -       | -    | ns    |

| ENRC input setup time                                   | ts3                  |                                                  | 20  | -       | -    | ns    |

| INO to IN7 and ENRC input hold time                     | t <sub>H1</sub>      |                                                  | 0   | _       | _    | ns    |

| S0 to S6 input hold time                                | t <sub>H2</sub>      |                                                  | 5   | -       | -    | ns    |

| OE to OUT <i>n</i> output enable delay time             | <sup>t</sup> OEN0, 1 | See note 4.                                      | -   | _       | 25   | ns    |

| OE to OUT <i>n</i> output disable delay time            | todeo, 1             | See note 4.                                      | -   | _       | 25   | ns    |

| CLK to OUT <i>n</i> output data hold time               | tонı                 | See note 3.                                      | 10  | _       | _    | ns    |

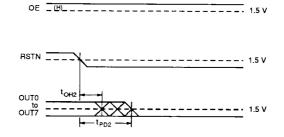

| RSTN to OUT <i>n</i> output data hold time              | toh2                 | See note 3.                                      | 10  | _       | _    | ns    |

| CLK to OUT <i>n</i> output data propagation delay time  | tPD1                 | See note 3.                                      | -   | -       | 28   | ns    |

| RSTN to OUT <i>n</i> output data propagation delay time | t <sub>PD2</sub>     | See note 3.                                      | _   | -       | 28   | ns    |

| Parameter                                                            | Symbol | rmbol Condition                  |     | Rating |     |      |  |

|----------------------------------------------------------------------|--------|----------------------------------|-----|--------|-----|------|--|

| i didireter                                                          | Symbol | Condition                        | min | typ    | max | Unit |  |

| INO to IN7, S0 to S6, ENRC,<br>CLK, RSTN and OE input<br>capacitance | Cin    | f = 1 MHz                        | _   | -      | 10  | pF   |  |

| OUT0 to OUT7 output capacitance                                      | Cout   | f = 1 MHz, V <sub>OE</sub> = 0 V | _   | -      | 20  | pF   |  |

#### Notes

1. Pins INO to IN7, S0 to S6, ENRC, CLK, RSTN and OE are inputs with internal pull-up resistances.

2. Pins OUT0 to OUT7 are tristate outputs.

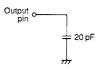

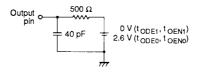

3. Measurement circuit 1

4. Measurement circuit 2

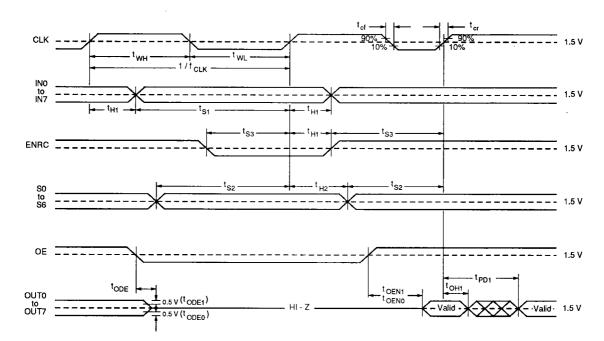

#### **Timing Diagrams**

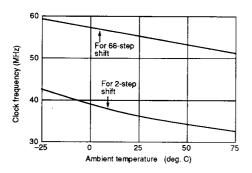

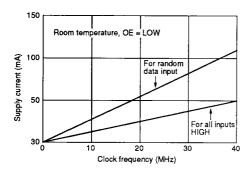

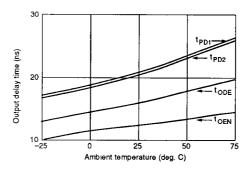

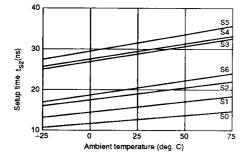

## **Typical Performance Characteristics**

Typical values at  $V_{DD}$  = 5.0 V

Maximum clock frequency vs. ambient temperature

# Operating supply current vs. clock frequency

Output delay time vs. ambient temperature

Minimum setup time vs. ambient temperature 1

ł

Minimum setup time vs. ambient temperature 2

#### Notes

1.  $t_{s1}$  and  $t_{s3}$  do not vary with the length of the shift register.

#### FUNCTIONAL DESCRIPTION

#### **Register Step Selection**

#### **Register operation**

The internal structure of the shift register is shown in the following figure. Inputs S0 to S6 select or bypass the outputs of their corresponding shift register blocks. Combinations of S0 to S6 thus select the shift register length of betwwen 2 and 129. Note that the first and last registers are always enabled.

#### **Register length select**

The S0 to S6 inputs select the register length. The length is given by the decimal value (S6 is MSB) plus 2.

Length =  $64 \cdot (S6) + 32 \cdot (S5) + 16 \cdot (S4) + 8 \cdot (S3) + 4 \cdot (S2) + 2 \cdot (S1) + (S0) + 2$

| Step number | S6   | S5   | <b>S</b> 4 | S3   | \$2  | S1   | SO   |

|-------------|------|------|------------|------|------|------|------|

| 129         | HIGH | HIGH | HIGH       | HIGH | HIGH | HIGH | HIGH |

| 128         | HIGH | HIGH | HIGH       | HIGH | нідн | HIGH | LOW  |

| 127         | HIGH | HIGH | HIGH       | HIGH | Нідн | LOW  | HIGH |

| 126         | HIGH | HIGH | HIGH       | HIGH | нідн | LOW  | LOW  |

- 2.  $t_{s_2}$  varies with the length of the shift register. All values are measured under worst conditions.

- a. All step select inputs are LOW except the one being measured.

- b. The value of  $t_{s_2}$  of the measured step select input may be less than the value shown if any other step select input is HIGH, except for S0 which is not affected by other step select inputs.

NIPPON PRECISION CIRCUITS-7

SM5829P

| Step number | S6   | S5   | S4   | S3   | S2   | S1   | S0   |

|-------------|------|------|------|------|------|------|------|

|             | :    | :    | ;    | :    | :    | :    | :    |

| 67          | HIGH | LOW  | LOW  | LOW  | LOW  | LOW  | нідн |

| 66          | HIGH | LOW  | LOW  | LOW  | LOW  | LOW  | LOW  |

| 65          | LOW  | HIGH | HIGH | HIGH | HIGH | HIGH | HIGH |

| ÷           | :    | :    | :    | :    | :    | :    | :    |

| 4           | LOW  | LOW  | LOW  | LOW  | LOW  | HIGH | LOW  |

| 3           | LOW  | LOW  | LOW  | LOW  | LOW  | LOW  | HIGH |

| 2           | LOW  |

#### Note

Pins S0 to S6 have internal pull-up resistances. Therefore, only LOW-level pins need be tied to ground. However, it is recommended that HIGH-level inputs be tied to VDD for applications using fixed-length shifting.

#### Input/Output Control

|      | Ir   | nputs       |      |                             | Outputs        |

|------|------|-------------|------|-----------------------------|----------------|

| RSTN | ENRC | CLK         | OE   | Shift register (internal) — | OUT0 to OUT7   |

| ×    | ×    | ×           | LOW  |                             | High impedance |

| ×    | ×    | ×           | HIGH |                             | Enable         |

| HIGH | HIGH | LOW-to-HIGH | ×    | Rotate shift                |                |

| HIGH | LOW  | LOW-to-HIGH | ×    | Non-rotate shift            |                |

| LOW  | ×    | ×           | ×    | Reset                       |                |

Note

$\times = don't care$

NIPPON PRECISION CIRCUITS LTD. reserves the right to make changes to the products contained in this data sheet in order to improve the design or performance and to supply the best possible products. Nippon Precision Circuits Ltd. assumes no responsibility for the use of any circuits shown in this data sheet, conveys no license under any patent or other rights, and makes no claim that the circuits are free from patent infringement. Applications for any devices shown in this data sheet are for illustration only and Nippon Precision Circuits Ltd. makes no claim or warranty that such applications will be suitable for the use specified without further testing or modification.

#### NIPPON PRECISION CIRCUITS LTD.

Shuwa Sakurabashi Building 5–4, Hachobori 4-chome Chuo-ku, Tokyo 104 Japan Telephone: 03-3555-7521 Facsimile: 03-3555-7528

NC9108AE 1993.08