# SC4510 High Performance Synchronous Buck Controller With Reference Tracking

# POWER MANAGEMENT

#### Description

The SC4510 can be configured as a synchronous buck convertor capable of sourcing and sinking current from load without losing output regulation. The output can be set to track an internal reference or an external voltage. The actual reference used by the error amplifier is buffered and brought out as a reference. It is the ideal choice for externally referenced or tracking buck convertors such as those for DDR memory applications.

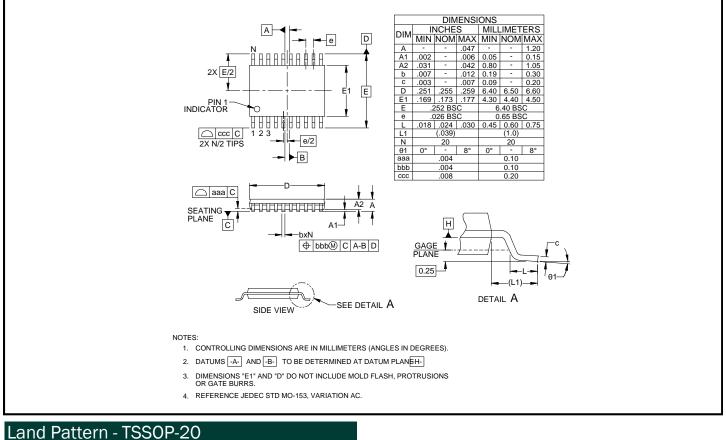

The controller is also designed for point of use DC-DC convertors with 2.5-16V power sources with a Vcc of 4.5V or higher. Soft start, current limit, programmable oscillator and external compensation functions are provided to ensure high degree of integration and low external component count. Semetch's patented Combi-Sense™ technique is utilised for lossless current sening and maximising efficiency. Both high and low side MOSFET drivers are built in and rated for substantial peak currents to minimise switching losses. The SC4510 is offered in a space saving TSSOP-20 package.

#### Features

- Synchronous buck operation with current sink or source without loss of regulation

- Output can track internal or external reference

- Buffered reference output from external reference

- Combi-Sense mode lossless current sensing

- 2.5V to 16V operation with 4.75V minimum V<sub>cc</sub>

- Direct drive for high side N-channel MOSFETs with diode and capacitor bootstrap

- Undervoltage lockout, Soft Start, Enable and Power Good functions

- Fast transient response with external compensation

- Current mode control with transconductance error amplifier

- Programmable oscillator frequency with external sync

#### Applications

- Externally referenced buck convertors

- DDR memory terminators

- Point of use power supplies

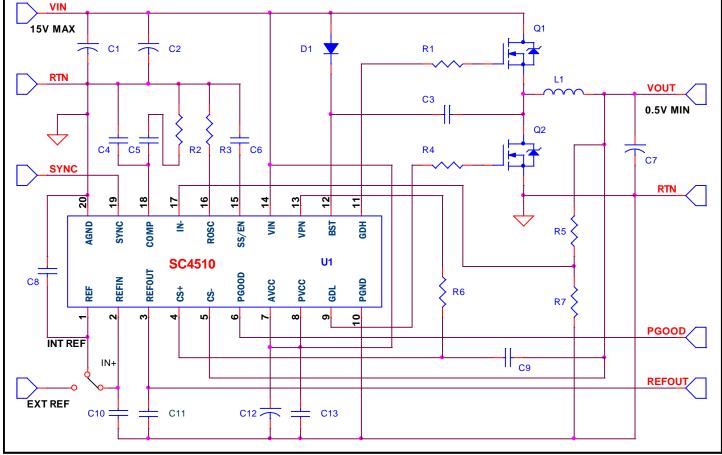

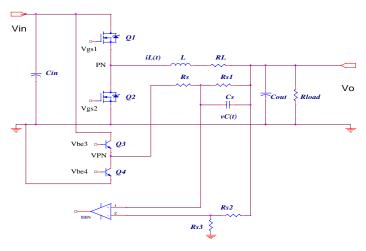

# **Typical Application Circuit**

SC4510

# **POWER MANAGEMENT**

## Absolute Maximum Ratings

SEMTECH

Exceeding the specifications below may result in permanent damage to the device, or device malfunction. Operation outside of the parameters specified in the Electrical Characteristics section is not implied. Exposure to Absolute Maximum rated conditions for extended periods of time may affect device reliability.

| Symbol | Maximum                                     | Units                                                                              |

|--------|---------------------------------------------|------------------------------------------------------------------------------------|

|        | -0.3 to 32 (steady state)                   |                                                                                    |

|        | -0.3 to 40<br>(for < 10ns @ freq. < 500kHz) | V                                                                                  |

|        | -0.3 to 16                                  | V                                                                                  |

|        | ±0.3                                        | V                                                                                  |

|        | -0.3 to AVCC                                | V                                                                                  |

|        | -0.3 to 6                                   | V                                                                                  |

|        | 0 to 3.0                                    | V                                                                                  |

|        | <u>+</u> 0.75                               | А                                                                                  |

|        | <u>+</u> 1                                  | А                                                                                  |

|        | -60 to +150                                 | °C                                                                                 |

|        | -40 to +125                                 | °C                                                                                 |

|        | 260                                         | °C                                                                                 |

|        | 2                                           | kV                                                                                 |

|        | Symbol                                      | -0.3 to 32 (steady state)         -0.3 to 40         (for < 10ns @ freq. < 500kHz) |

Unless specified: T<sub>A</sub> = T<sub>J</sub> = -40°C to +85°C, AVCC/PVCC = 12V, Fosc = 300 kHz, SS/EN = 5V

| Parameter               | Symbol               | Test Conditions        | Min  | Тур | Max | Unit |

|-------------------------|----------------------|------------------------|------|-----|-----|------|

| Power Supply            |                      |                        |      | •   |     | •    |

| Operating Current       |                      | No load on GDL and GDH |      | 8   | 12  | mA   |

| Analog Supply Input     | AVCC                 | VIN > 2.5V             | 4.75 |     | 16  | V    |

| Drive Supply Input      | PVCC                 | VIN > 2.5V             | 4.75 |     | 16  | V    |

| Convertor Power Input   | VIN                  |                        | 2.5  |     | 16  | V    |

| Undervoltage Lockout    |                      |                        |      |     |     |      |

| Start Threshold         | AVCC <sub>MIN</sub>  |                        | 4.2  | 4.5 | 4.7 | V    |

| UVLO Hysteresis         | AVCC <sub>HYST</sub> |                        |      | 0.2 |     | V    |

| Soft Start and Shudown  |                      | •                      |      | •   |     | •    |

| Charge Current          | I <sub>SSCHG</sub>   |                        |      | 2   |     | μA   |

| Discharge Current       |                      |                        |      | 1   |     | μΑ   |

| Output Enable Threshold | V <sub>ENTH</sub>    |                        | 2.0  |     |     | V    |

| Shutdown Threshold      | V <sub>SSTH</sub>    |                        |      |     | 0.6 | V    |

#

Unless specified:  $T_A = T_J = -40^{\circ}$ C to +85°C, AVCC/PVCC = 12V, Fosc = 300 kHz, SS/EN = 5V

| Parameter                           | Symbol              | Test Conditions                                            | Min  | Тур        | Max                           | Unit             |

|-------------------------------------|---------------------|------------------------------------------------------------|------|------------|-------------------------------|------------------|

| Error Amplifier                     |                     |                                                            |      |            |                               |                  |

| Input Bias Current                  |                     |                                                            |      | 0.4        | 0.7                           | μA               |

| Input Offset Voltage                |                     |                                                            |      |            | 2.5                           | mV               |

| Transconductance Gain               | G <sub>M</sub>      | Output Source Mode<br>Output Sink Mode                     |      | 275<br>375 |                               | $\mu\Omega^{-1}$ |

| Unity Gain Bandwidth <sup>(1)</sup> |                     |                                                            |      | 3          |                               | MHz              |

| Output Sink/Source Current          |                     | $V_{COMP} = 2.5V$                                          |      | 15         |                               | μA               |

| Buffered Reference                  |                     |                                                            |      |            |                               |                  |

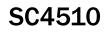

| Internal reference                  | V <sub>REF</sub>    | -40C to +85C                                               | 0.49 | 0.5        | 0.51                          | V                |

| Line regulation                     |                     | 5V < AVCC < 15V                                            |      | 0.02       |                               | %/V              |

| External reference input range      | V <sub>REFIN</sub>  |                                                            | 0.3  |            | 3.0                           | V                |

| Tracking accuracy                   | V <sub>REFOUT</sub> | With respect to V <sub>REFIN</sub><br>(Greater of the two) |      |            | <u>+</u> 0.5<br><u>+</u> 10.0 | %<br>mV          |

| Reference output current            | I <sub>REFOUT</sub> |                                                            |      | 5          |                               | mA               |

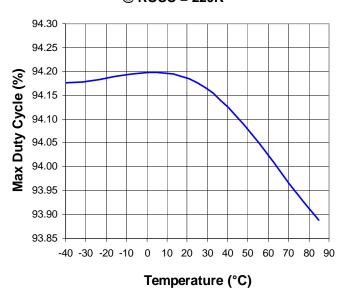

| Oscillator and Synchronisatio       |                     | 1 1                                                        |      | 1          | !!                            |                  |

| Frequency range                     | Fosc                |                                                            | 0.1  |            | 1                             | MHz              |

| Frequency setting                   | Fosc                | ROSC = 221K                                                | 270  | 300        | 330                           | KHz              |

| Sync input High voltage             |                     |                                                            | 1.5  |            |                               | V                |

| Sync input Low voltage              |                     |                                                            |      |            | 0.5                           | V                |

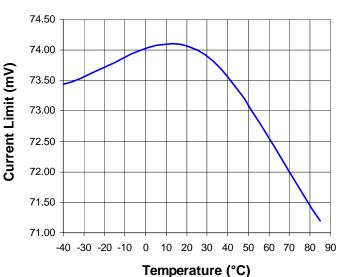

| Duty Cycle                          |                     | · · ·                                                      |      |            |                               |                  |

| Maximum Duty Cycle                  |                     | Fosc = 1 MHz                                               |      | 70         |                               | %                |

|                                     |                     | Fosc = 300 kHz                                             |      | 90         |                               | %                |

| Minimum Duty Cycle                  |                     | Fosc = 100 kHz                                             |      | 5          |                               | %                |

| Minimum pulse width                 |                     | Fosc = 0.1 to 1 MHz                                        |      | 250        |                               | nS               |

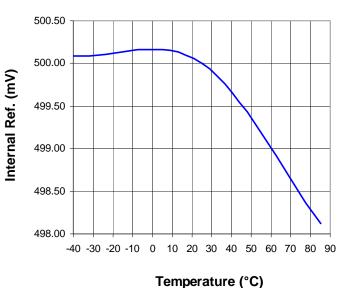

| Current Limit                       |                     |                                                            |      |            |                               |                  |

| Current limit sense threshold       | V <sub>CSLIM</sub>  | Output source mode                                         | 60   | 75         | 90                            | mV               |

|                                     |                     | Output sink mode                                           | -85  | -110       | -130                          | mV               |

| Delay to Output <sup>(1)</sup>      | t <sub>CSDLY</sub>  | 10 mV Overdrive                                            |      | 50         |                               | nS               |

# Electrical Characteristics (Cont.)

EMTECH

Unless specified:  $T_A = T_J = -40^{\circ}$ C to +85°C, AVCC/PVCC = 12V, Fosc = 300 kHz, SS/EN = 5V

| Parameter                    | Symbol            | Test Conditions                                                          | Min | Тур | Max | Unit   |

|------------------------------|-------------------|--------------------------------------------------------------------------|-----|-----|-----|--------|

| Power Good Output            |                   | •                                                                        |     | •   | •   |        |

| Overvoltage sense threshold  | V <sub>OVTH</sub> | REFIN = 2.5V                                                             |     | 2.8 |     | V      |

| Undervoltage sense threshold | V <sub>UVTH</sub> | REFIN = 2.5V                                                             |     | 2.2 |     | V      |

| Power Good voltage           | V <sub>PG</sub>   | I <sub>PG</sub> = 5 mA<br>I <sub>PG</sub> = 2.5 mA<br>Output under fault |     | 1.5 | 0.4 | V<br>V |

| Output Drive                 |                   |                                                                          | •   | •   |     |        |

| High Side Gate Drive         | I <sub>GDH</sub>  | Source or sink                                                           |     | 1   |     | А      |

| Low Side Gate Drive          | I <sub>GDL</sub>  | Source or sink                                                           |     | 1   |     | А      |

| Dead Time Between Drives     |                   |                                                                          | 60  | 90  | 120 | nS     |

| Rise Time                    |                   | С <sub>оит</sub> = 1000 рF                                               |     | 20  |     | nS     |

| Fall Time                    |                   | С <sub>оит</sub> = 1000 рF                                               |     | 20  |     | nS     |

4

Note:

(1) Guaranteed by design. Not tested in production.

### **Ordering Information**

| Part Number                 | Package <sup>(1)</sup> | Temp. Range (T <sub>J</sub> ) |  |  |

|-----------------------------|------------------------|-------------------------------|--|--|

| SC4510ITSTR                 | TSSOP-20               | -40°C to +85°C                |  |  |

| SC4510ITSTRT <sup>(2)</sup> | 1330F-20               | -40 C 10 +83 C                |  |  |

Notes:

(1) Only available in tape and reel packaging.

A reel contains 2500 devices.

(2) Lead free product. This product is fully WEEE and RoHS compliant.

#### **Pin Configuration** TOP VIEW REF C AGND 1 20 REFIN 2 19 SYNC REFOUT 3 18 COMP CS+ 17 IN-4 CS-5 16 ROSC PGOOD SS/EN 6 15 AVCC 14 VIN 7 PVCC VPN 8 13 GDL 🗔 BST 9 12 PGND 10 11 GDH (20 Pin TSSOP)

SEMTECH

# **Pin Descriptions**

| Pin # | Pin Name | Pin Function                                                                                                                                                                                                            |

|-------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | REF      | Internal 0.5V bandgap reference                                                                                                                                                                                         |

| 2     | REFIN    | Non inverting input of the error amplifier. Can be connected to REF pin or an external voltage such as VDDQ/2. Maximum input range is 3V                                                                                |

| 3     | REFOUT   | Buffered reference output fro external use. Tracks the REFIN voltage                                                                                                                                                    |

| 4     | CS+      | Current sense input +ve                                                                                                                                                                                                 |

| 5     | CS-      | Current sense input -ve. Typically connected to the VOUT end of the output inductor.                                                                                                                                    |

| 6     | PGOOD    | Power Good output signal. Open collector output goes low under fault and sinks up to 5 mA. Monitors the output at thresholds of $\pm$ 12% with respect to REFIN voltage.                                                |

| 7     | AVCC     | Supply voltage for internal analog circuits.                                                                                                                                                                            |

| 8     | PVCC     | Supply voltage for output drivers. Bypass with a large ceramic capacitor to PGND.                                                                                                                                       |

| 9     | GDL      | Gate drive output for the low side N-Channel MOSFET.                                                                                                                                                                    |

| 10    | PGND     | Power ground for returning the drive currents.                                                                                                                                                                          |

| 11    | GDH      | Gate drive output for the high side N-Channel MOSFET.                                                                                                                                                                   |

| 12    | BST      | Boost capacitor connection for the high side gate drive.<br>Connect an external capacitor and a diode as shown in the Typical Application Circuit.                                                                      |

| 13    | VPN      | Virtual Phase Node. Auxiliary pin used for virtual current sense.Connect an RC between this pin and the VOUT end of the output inductor to sense the integrated current feedback signal.                                |

| 14    | VIN      | Input supply for the virtual current sense circuit.<br>This should be at the same potential as the drain of the high side power MOSFET.                                                                                 |

| 15    | SS/EN    | Soft Start and Enable pin. Grounding the pin shuts down the controller. Connect a capacitor to soft start the output. The output will start switching when the SS pin voltage goes above 0.5V.                          |

| 16    | ROSC     | Connect a resistor to AGND to program the oscillator frequency.                                                                                                                                                         |

| 17    | IN-      | Inverting feedback input for the error amplifier. Follows the reference input provided at the REFIN pin. Maximum voltage range is 3V.                                                                                   |

| 18    | COMP     | Error amplifier output for compensation.                                                                                                                                                                                |

| 19    | SYNC     | Pin for external synchronisation signal input                                                                                                                                                                           |

| 20    | AGND     | Analog signal ground. Return the ground connections of noise sensitive components such as ROSC, soft start capacitor, sync signal, feedback resistor chain and feedback compensation components separately to this pin. |

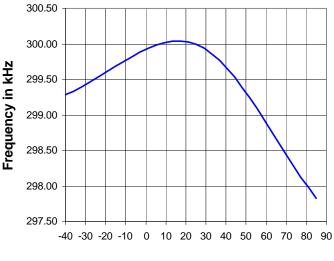

Internal Reference vs Temperature

**Current Limit vs Temperature**

Max Duty Cycle vs Temperature @ ROSC = 220K

Frequency vs Temperature @ ROSC = 220K

Temperature (°C)

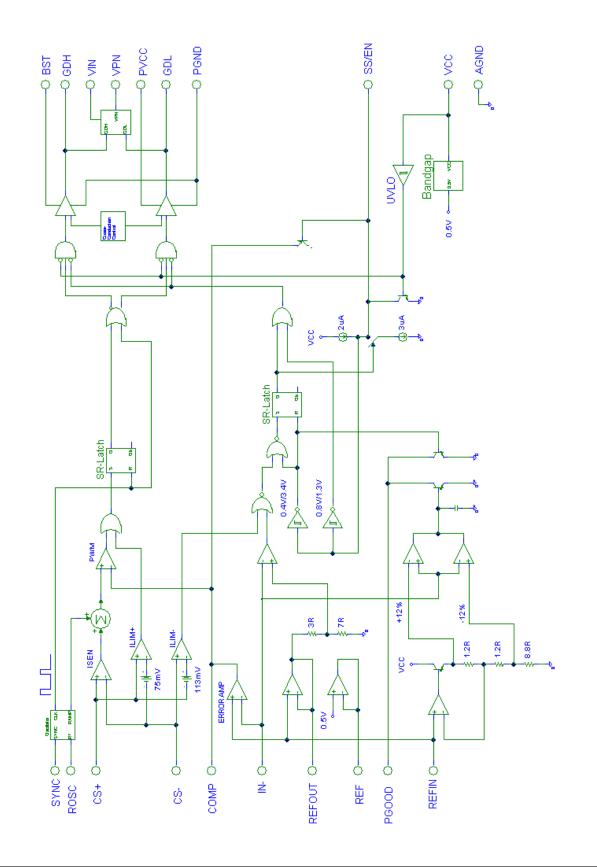

Block Diagram

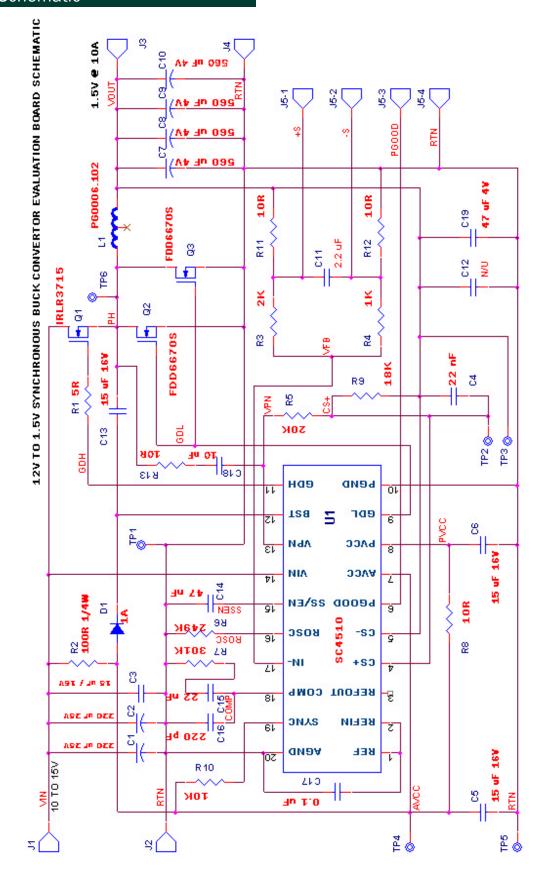

# Application Schematic

# Functional Description

# INTRODUCTION

The SC4510 is designed to control and drive N-Channel MOSFET synchronous rectified buck convertors. It has additional features such as reference tracking, buffered REFOUT that make it particularly attractive for tracking output applications such as DDR memories. It can operate the convertor in both the source and sink modes. The switching frequency is programmable to optimize design. The current mode switching regulator section features Semtech's patented Combi Sense technique for lossless current sensing and provides a hiccup mode overcurrent protection.

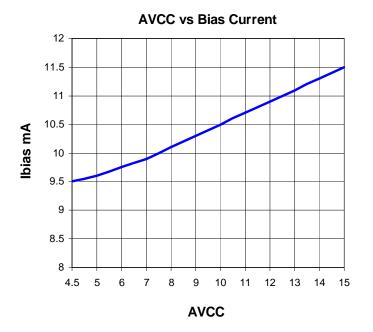

## POWERING THE CONTROLLER

Supplies VIN, PVCC and AVCC from the input source are used to power the SC4510. The AVCC and PVCC can be tied to VIN supply or can be from separate source to optimise efficiency. The AVCC supply provides the bias for the oscillator, PWM switcher, voltage feedback, current sense and the Power OK circuitry. PVCC is used to drive the low and high side MOSFET gates. Minimum operating limit for VIN is 2.5V typical. However, PVCC and AVCC have higher UVLO limits as explained below. Maximum range for all of the input and supply voltages is 16V.

# STARTUP AND ENABLE

Startup is inhibited until AVCC input reaches its UVLO threshold . The UVLO limit is 4.5V typical. When AVCC is below the UVLO threshold, the soft start pin is pulled low and output drivers are turned off. The power up sequence is initiated by a 2 uA current source charging the soft start capacitor connected to the SS pin. When the SS pin reaches 0.5V, the convertor will start switching. The reference input of the error amplifier is ramped up with the soft-start signal. The soft start duration is controlled by the value of the SS cap. The soft start pin also functions as an enabler with TTL compatible input thresholds. If the SS/EN pin is pulled below 0.6V, the SC4510 is disabled and draws very low current.

# REFERENCE INPUT AND BUFFERED OUTPUT

The SC4510 comes with a low level built in reference of 0.5V. The non inverting input of the error amplifier is brought out to provide additional flexibility and output tracking functions. In the basic operation, the REF and REFIN pins may be shorted together and the output voltage feedback is provided at IN- pin.

In tracking applications such as DDR memories an external reference may be brought in and applied at REFIN pin. The range of applicable external voltage is up to 3V. The UV and OV sensing thresholds for PGOOD output are centered  $\pm 12\%$  around REFIN voltage.

The voltage at REFIN pin is buffered and put out as REFOUT. This output tracks REFIN accurately within  $\pm$  10 mV offset or 0.5% of REFIN, whichever is higher. It can also source up to 5 mA current. The REFOUT output is particularly useful in DDR memory termination applications.

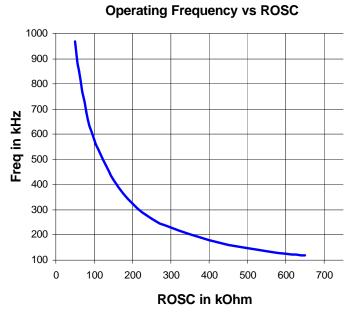

### OSCILLATOR

The switching frequency  $\rm F_{OSC}$  of the SC4510 is set by an external resistor using the following formula:

$$R_{OSC}$$

= 66,000 /  $F_{OSC}$

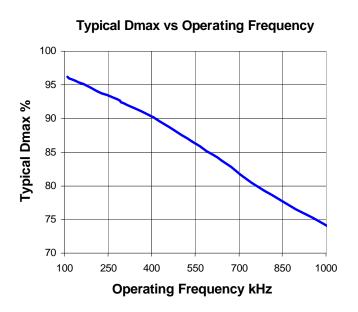

$R_{OSC}$  is in k $\Omega$  and  $F_{OSC}$  is in kHz. The nominal range for the oscillator frequency is from 100 kHz to 1 MHz. The maximum duty cycle available at any given frequency is limited by minimum pulse width requirement which is typically 250 nS. This gives a typical Dmax of 70% at the highest frequency of 1 MHz or about 90% at 300 kHz.

The oscillator can be synchronised to an external clock that is nominally *faster* than the internal frequency set by  $R_{osc.}$ The synchronising signal should be TTL compatible, with transitions above 2.0V and below 0.6V. The external voltage level applied should be lower than AVCC of the device.

#### GATE DRIVERS

The low side gate driver is supplied from PVCC and provides a peak source/sink current of 1A. The high side gate drive is capable of sourcing and sinking peak currents of 0.75A. Protection logic provides a typical dead time of 90 nS to ensure both the upper and lower MOSFETs will not turn on simultaneously and cause a shoot through condition.

The high side Mosfet gate drive can be derived from the PVCC supply using the classical bootstrap technique as illustrated in the applications circuits. A bootstrap capacitor is connected from BST to the Phase node while PVCC is connected through a low  $V_F$  Schottky or an ultrafast diode to the BST. This will provide a gate to source voltage approximately equal to the (VCC - Vfwd).

#### **Functional Description**

Alternately if an external 12V supply is available it can be directly connected between BST and GND. The actual gate to source voltage of the upper Mosfet will then be approximately be equal to (12V - VIN). This technique is useful if the input voltage is 5V but a 12V supply is also available in the system.

#### POWER GOOD MONITOR

The PGOOD circuitry monitors the FB input of the convertor error amplifier. If the voltage on this input goes above +12%or below -12% of the REFIN voltage the PGOOD pin is pulled low. The PGOOD is an open drain output and can sink up to 5 mA. The PGOOD pin is held low during the startup sequence.

#### ERROR AMPLIFIER

The SC4510 is a current mode controller and operates by matching the peak of the sensed inductor current to the output of the voltage error amplifier. The error amplifier is transconductance type and should be compensated accordingly. It has a transconductance gain of 275  $\mu\Omega^{-1}$  in the source mode. Current is sensed losslessly by taking the weighted average of both the MOSFET drops and adding it to the DC voltage drop across the inductor. More information on this patented Combi Sense technique is provided in the next section.

Current mode controllers are inherently unstable at duty ratios above 50% and need some form of slope compensation to operate correctly. This slope compensation is built into the architecture of SC4510 where a portion of the ramp is internally added to the current sense signal. The amount of added ramp is optimised and varies with the operating duty cycle. Larger duty ratios result in larger ramps being added to the current sense signal. Note that the uncorrected current signal is used for overcurrent comparator. The current limit point is unaffected by the slope compensation.

www.semtech.com

SC4510

#### COMBI-SENSE OPERATION AND CURRENT LIMIT

EMTECH

Effective current sensing is important for the current mode control of power convertors. Instead of using the traditional lossy resistive current sense scheme, a novel lossless Combi-Sense technique is used in SC4510. This SEMTECH proprietary technology has the advantages of

1) lossless current sensing,

POWER MANAGEMENT

Application Information

- 2) bigger signal-to-noise ratio, and

- 3) thermal run-away prevention.

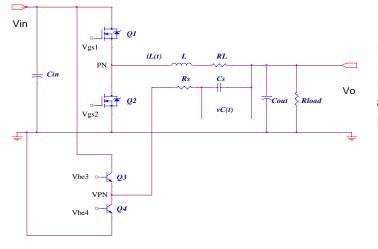

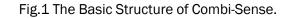

The basic structure of the Combi-Sense is shown in Fig.1. Where  $R_L$  is the equivalent resistance of the output inductor. The added  $R_s$  and  $C_s$  form the RC branch in "parallel" with the output inductor for inductor current sensing. This branch works with a small signal totem pole (Q3 and Q4) integrated in SC4510 in order to improve the signal-to-noise ratio. The base signals Vbe3 and Vbe4 are designed to closely follow the gate signals Vgs1 and Vgs2, respectively. Ideally, the leading and falling edges of the Virtual Phase Node (VPN) follow that of the Phase Node (PH) when Q1~Q4 switch in perfect synchronism.

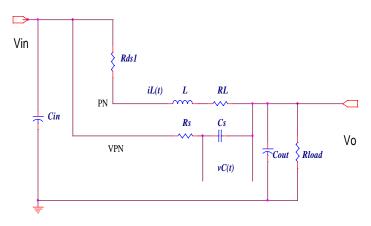

When Q1/Q3 turn ON and Q2/Q4 turn OFF, the equivalent circuit of Fig.1 is shown in Fig. 2a). Where, *Rds1* is the onresistance of the top MOSFET. The two branches, consisting of {(*Rds1+RL*), *L*} and {*R<sub>s</sub>*, *C<sub>s</sub>*}, are in parallel. The DC voltage drop (*Rds1+RL*)*I*<sub>o</sub> equals *V<sub>cs</sub>*. In this way, the output current is sensed from *V<sub>cs</sub>* when (*Rds1+RL*) is known.

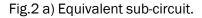

When Q1/Q3 turn OFF and Q2/Q4 turn ON, the equivalent circuit of Fig.1 becomes the sub-circuit as shown in Fig. 2b). Where Rds2 is the channel resistance of the bottom MOSFET. In this case, the branch  $\{R_s, C_s\}$  is in parallel with  $\{(Rds2+RL), L\}$  and  $V_{cs}=(Rds2+RL)I_o$ .

When averaged over a complete cycle,

$$V_{cs} = [D(Rds1+RL)+(1-D)(Rds2+RL)]I_{o}$$

= [D Rds1+(1-D)Rds2+RL]I\_{o}

= R\_{eq}I\_{o}.

D is the operating duty ratio. It is noted that the average DC value in  $V_{cs}$  is independent of the value of L,  $R_s$  and  $C_s$ . If only the average load current information is needed (such as in average current mode control), this current sensing method is effective without further requirements.

Fig.2 b) Equivalent sub-circuit.

SEMTECH

#### **POWER MANAGEMENT**

#### Application Information (Contd.)

In peak current mode control as in SC4510, the voltage ripple on  $C_{\rm s}$  is critical for PWM operation. In fact, the peakto-peak value of the voltage ripple across  $V_{\rm cs}$  (denoted as  $\Delta V_{\rm cs}$ ) directly affects the signal-to-noise ratio of the PWM operation. In general, smaller  $\Delta V_{\rm cs}$  leads to small signal-tonoise ratio and more noise sensitive operation. Larger  $\Delta V_{\rm cs}$  leads to more circuit (power stage) parameter sensitive operation. A good engineering compromise is to make

$$\Delta V_{\rm Cs} \sim R_{\rm eg} \Delta I_{\rm c}$$

Where  $\Delta I_{o}$  is the peak to peak ripple current in the inductor. The prerequisite for such relation is the so called time constant matching condition

$$\frac{L}{R_{eq}} \approx R_s C_s$$

When Rds1 = Rds2, the above approximations become precise equalities. For the example in the Application Circuit shown on p9 the inductor value is 1 uH,

$\textit{RL}\texttt{=}~\texttt{1.4}~\text{m}\Omega$  ,  $\textit{Rd}\texttt{s1}\texttt{=}~\texttt{11}~\text{m}\Omega$  and  $\textit{Rd}\texttt{s2}\texttt{=}~\texttt{3}~\text{m}\Omega$

Since the operating duty ratio is very small the effective Rds is determined mostly by Rds2. The time constant  $R_s C_s$  should be set close to 0.2 mS. Since the effective value of  $R_s$  is 20 k $\Omega$  // 18 k $\Omega$  = 9.5 k $\Omega$ ,  $C_s$  = 22 nF was chosen .

#### CURRENT LIMIT SCALING

In SC4510, the current limiting is performed on cycle-bycycle basis. When the voltage difference between CS+ and CS- exceeds 65 mV, the top MOSFET duty ratio is clipped in order to limit the output source current. Similarly, when the voltage difference between CS- and CS+ exceeds 113 mV, the bottom MOSFET duty ratio is clipped in order to limit the sink current. For the configuration in Fig.1, the convertor output current limit is set around

$$I_{LMcp} = \frac{75 \ mV}{R_{eq}},$$

for the current sourcing mode and

$$I_{LMcn} = -\frac{110 \ mV}{R_{eq}}$$

for the current sinking mode.

In the application circuit,  $R_{eq}$ =5.6 m $\Omega$ . However the peak value of the sensed current is not exact for a number of reasons. Though the Phase Node PH and Virtual Phase Node VPN voltages are assumed to be identical, there will be some offset between them which adds to the average value of the current feedback signal. This is particularly true during the switching transitions where rise and fall times of the true Phase Node are dependent on the power MOSFET characteristics. The peak value of the signal also includes the ripple current  $\Delta I_o$  riding on the output DC current. In addition, the signal level is subject to variations with respect to input and PVCC voltages. The difference between sensed current magnitude and the actual current gets more pronounced for low output voltages where the operating duty is also low.

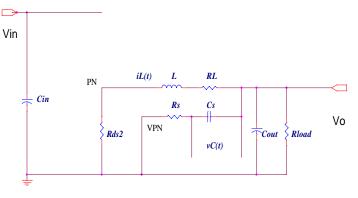

Given these differences, some amount of scaling the current sense signal is required to adjust the current limit in most applications. This can be accomplished easily by simple resistor networks and the possible configurations are shown in Fig.3.

a) When the required current limit value  $I_{LM}$  is greater than  $I_{LMcp}$ , remove  $R_{s3}$  and solve for for  $R_{s2} = R_{seq}$  and

$$R_{seq} C_s = \frac{L}{R_{eq}}$$

$R_{seq}$  is the parallel combination of  $R_s$  and  $R_{s1}$  as shown in Fig 3).  $R_{s2}$  helps to reduce the offset at the input of current sense amplifier inside SC4510.

Fig.3 Current limit scaling.

# Application Information (Contd.)

For simplicity  ${\it R}_{\rm s2}$  can be omitted and the current limit can be estimated from

$$I_{LM} R_{eq} = 75 \ mV \times \frac{\frac{R_s + R_{s1}}{R_{s1}}}{R_{s1}}$$

In the application circuit the current feedback signal had to be halved to account for variations explained above and ensure that the current limit is at least 20% above nominal at minimum input.

b) When the required current limit value  $I_{_{LM}}$  is less than  $I_{_{LMcp}}$  remove  $R_{_{\rm S1}}$  solve

$$R_{s}C_{s} = \frac{L}{R_{eq}}$$

for  $R_s$  and solve

$$I_{LM}R_{eq} + \frac{R_s}{R_{s3}}V_o = 75 \ mV$$

to set the current limit.

Similar steps and equations apply to the current limit setting and scaling for current sinking mode.

#### OVERCURRENT PROTECTION AND HICCUP MODE

In addition to the current limit capability, SC4510 provides overcurrent protection in case the convertor output is shorted to ground. If this fault condition happens, the controller senses the output voltage via voltage feedback pin IN-. When the sensed voltage is below 70% of the normal feedback voltage, the controller shuts down both top and bottom MOSFETs. At the same time, a current sink of 1  $\mu$ A discharges the soft start capacitor  $C_{ss}$  connected to the SS/EN pin.

When the capacitor is discharged until its voltage reaches 0.4V, the controller initiates the soft start process. If the short circuit fault persists, the controller shuts down the convertor again when the voltage across the soft start capacitor reaches 3.4V. This hiccup process repeats until the fault condition is removed. Under this situation, it is important to make sure that the convertor does not fail. One important parameter is the convertor thermal condition which is directly related to the effective inductor and MOSFETs current. The effective currents in inductor and MOSFETs can be estimated using the following equations.

a) The time it takes to discharge the capacitor from 3.4 V to 0.4 V

SC4510

$$t_{ssf} = C_{SS} \times \frac{(3.4 - 0.4)V}{1 \, \text{mA}}.$$

In the application circuit,  $C_{ss}$ = 47 nF and  $t_{ssf}$  is calculated as 140 mS.

b) The time interval of the soft start process from 0.4V to  $3.4\mathrm{V}$

$$t_{ssr} = C_{SS} \times \frac{(3.4 - 0.4) V}{2 m A}.$$

When  $C_{ss} = 47$  nF,  $t_{sr}$  is calculated as 70 mS.

Notice that during the soft start process, the convertor only starts switching when the voltage at SS/EN exceeds 1.3V. Then,

c) The effective operation time interval

$$t_{sso} = C_{SS} \times \frac{(3.4 - 1.3) V}{2 mA}.$$

This is the interval where the gate drive outputs are active and current builds up in the inductor.

The effective inductor current is then

$$I_{Leff} = I_{LMcp} \ \frac{t_{sso}}{t_{ssf} + t_{ssr}}.$$

It turns out that *ILeff* is independent of the soft start capacitor value and is determined as  $0.3I_{LMcp}$ . This should lead to a reasonable thermal condition in the convertor hiccup operation. Note that *ILeff* calculated is not the true average value of the inductor current since the convertor is still in the soft start mode during the *tsso* interval.

# SC4510

POWER MANAGEMENT

# Application Information (Contd.)

EMTECH

### PCB LAYOUT FOR SC4510

Careful attention to layout requirements is necessary for successful implementation of the SC4510 PWM controller. High switching currents with fast rise and fall times are present in the application and their effect on ground plane voltage differentials must be understood and minimized. A good layout with minimum parasitic loop areas will

#### a) reduce EMI

b) lower ground injection currents, resulting in electrically "cleaner" grounds for the rest of the system and

c) minimize source ringing, resulting in more reliable gate switching signals.

#### LAYOUT GUIDELINES

In the following  $Q_{_{\rm T}}$  and  $Q_{_{\rm B}}$  denote the high side and low side MOSFETs respectively.

1) A ground plane should be used. The number and position of ground plane interruptions should be minimised so as not to compromise ground plane integrity. Isolated or semiisolated areas of the ground plane may be deliberately introduced to constrain ground currents into particular paths, such as the output capacitor or the  $Q_{\rm B}$  source.

2) The high power, high current parts of the circuit should be laid out first. The on time loop formed by the input capacitor Cin, the high side FET  $Q_{T}$  the output inductor and the output capacitor bank Cout must be kept as small as possible. Another loop area to minimise is formed by low side FET  $Q_{B}$ , the output inductor and the output capacitor bank Cout during the off period. These loops contain all the high current, fast transition switching. Connections should be as wide and as short as possible to minimize loop inductance.

3) The connection between the junction of  $Q_{\tau}$ ,  $Q_{B}$  and the output inductor should be a wide trace or copper region. It should be as short as practical. Since this connection has fast voltage transitions, keeping this connection short will minimize EMI. Also keep the Phase connection to the IC short. The top FET gate charge currents flow in this trace.

4) The output capacitor Cout should be located as close to the load terminals as possible. Fast transient load currents are supplied by Cout and connections between Cout and the load must be kept short with wide copper areas to minimize inductance and resistance. This will improve the transient response to step loads. 5) The SC4510 is best placed over a quiet ground plane area. Avoid pulse currents of the Cin,  $Q_T$ ,  $Q_B$  loop flowing in this area. This analog ground plane should be connected to the power ground plane at a "quiet" point near the input capacitor. Under no circumstance should it be returned to a point inside the Cin,  $Q_T$ ,  $Q_B$ , Cout power ground loops.

6) The SC4510 AGND pin is connected to the separate analog ground plane with minimum lead length . All analog grounding paths including decoupling capacitors, feedback resistors, compensation components, soft start capacitor, frequency and current-limit setting resistors should be connected to the same plane.

7) Locate the critical filtering capacitors as close as possible to their respective device. This is particularly true for the current feedback filtering capacitor connected between CS+ and CS-. A high value ceramic capacitor is also recommended between PVCC and PGND pins close to the device.

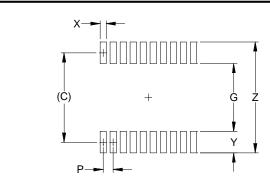

# **Outline Drawing - TSSOP-20**

|     | DIMENSIONS |             |  |  |  |

|-----|------------|-------------|--|--|--|

| DIM | INCHES     | MILLIMETERS |  |  |  |

| С   | (.222)     | (5.65)      |  |  |  |

| G   | .161       | 4.10        |  |  |  |

| Р   | .026       | 0.65        |  |  |  |

| Х   | .016       | 0.40        |  |  |  |

| Y   | .061       | 1.55        |  |  |  |

| Ζ   | .283       | 7.20        |  |  |  |

NOTES:

1. THIS LAND PATTERN IS FOR REFERENCE PURPOSES ONLY. CONSULT YOUR MANUFACTURING GROUP TO ENSURE YOUR COMPANY'S MANUFACTURING GUIDELINES ARE MET.

# **Contact Information**

Semtech Corporation **Power Management Products Division** 200 Flynn Road, Camarillo, CA 93012 Phone: (805)498-2111 FAX (805)498-3804