## ICs for Communications

Analog Line Interface Solution ALIS V3

PSB 4595 Version 2.1 PSB 4596 Version 3.1

Product Overview 06.98

| ALIS<br>Revision History:        |                             | Current Version: 06.98                       |

|----------------------------------|-----------------------------|----------------------------------------------|

| Previous Ver                     | rsion:                      |                                              |

| Page<br>(in previous<br>Version) | Page<br>(in new<br>Version) | Subjects (major changes since last revision) |

|                                  |                             |                                              |

|                                  |                             |                                              |

For questions on technology, delivery and prices please contact the Semiconductor Group Offices in Germany or Siemens Companies and Representatives worldwide: please also see our webpage at :

http://www.siemens.de/Semiconductor/address/address.htm.

#### Edition 06.98

This edition was realized using the software system FrameMaker®.

#### Published by Siemens AG, HL AT © Siemens AG 1998.

#### All Rights Reserved.

#### Attention please!

As far as patents or other rights of third parties are concerned, liability is only assumed for components, not for applications, processes and circuits implemented within components or assemblies.

The information describes the type of component and shall not be considered as assured characteristics.

Terms of delivery and rights to change design reserved.

For questions on technology, delivery and prices please contact the Semiconductor Group Offices in Germany or the Siemens Companies and Representatives worldwide (see address list).

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Siemens Office, Semiconductor Group.

Siemens AG is an approved CECC manufacturer.

#### Packing

Please use the recycling operators known to you. We can also help you – get in touch with your nearest sales office. By agreement we will take packing material back, if it is sorted. You must bear the costs of transport.

For packing material that is returned to us unsorted or which we are not obliged to accept, we shall have to invoice you for any costs incurred.

#### Components used in life-support devices or systems must be expressly authorized for such purpose!

Critical components<sup>1</sup> of the Semiconductor Group of Siemens AG, may only be used in life-support devices or systems<sup>2</sup> with the express written approval of the Semiconductor Group of Siemens AG.

- 1 A critical component is a component used in a life-support device or system whose failure can reasonably be expected to cause the failure of that life-support device or system, or to affect its safety or effectiveness of that device or system.

- 2 Life support devices or systems are intended (a) to be implanted in the human body, or (b) to support and/or maintain and sustain human life. If they fail, it is reasonable to assume that the health of the user may be endangered.

| Table of                                          | of Contents P                                                                                                                                                                                     | age                        |

|---------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| <b>1</b><br>1.1                                   | Overview                                                                                                                                                                                          |                            |

| 2                                                 | Block Diagram                                                                                                                                                                                     | 8                          |

| <b>3</b><br>3.1<br>3.2<br>3.3                     | Pin Configuration and DefinitionsPin ConfigurationPin Definitions of PSB 4595Pin Definitions of PSB 4596                                                                                          | 9<br>10                    |

| <b>4</b><br>4.1<br>4.2<br>4.3<br>4.4              | Typical ApplicationsThe ALIS V3 Chip Set with Digital Signal Processor(DSP)-based ModemThe ALIS V3 Chip Set with Host-based Software ModemHybrid Modem (ISDN plus Analog)Modem plus Speaker Phone | 14<br>15<br>16             |

| <b>5</b><br>5.1<br>5.2<br>5.2.1<br>5.2.2<br>5.2.3 | Functional Description         Functional Block Diagram         Basic Functionality         Receiving and Transmitting Data         Input Impedance         Caller ID                             | 18<br>19<br>19<br>19<br>19 |

| <b>6</b><br>6.1<br>6.2<br>6.3<br>6.4              | Interfaces Overview                                                                                                                                                                               | 20<br>20<br>22             |

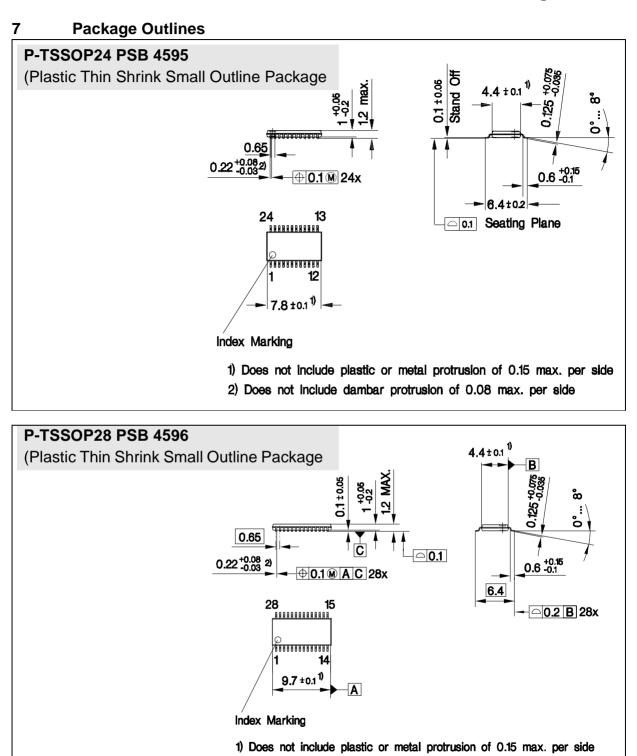

| 7                                                 | Package Outlines                                                                                                                                                                                  | 26                         |

| 8                                                 | Glossary                                                                                                                                                                                          | 27                         |

#### 1 Overview

#### Overview

ALIS V3 is a chip set used to connect analog phone lines to digital equipment such as fax machines. Its technology and design make it especially suitable for use throughout the world in:

- V.34 modems

- V.90 modems

- Fax machines

The ALIS V3 chip set is an ideal front end for modems and fax machines because these pieces of equipment have to convert digital information into analog signals and vice versa for communications via telephone lines. ALIS V3 bridges the gap between a digital data pump and an analog phone line.

Reliability in digital processing is much better than in analog communications. The new design of the ALIS V3 chip set has transferred processing that was previously done on the analog side across to the digital part. Digital filters ensure great precision and virtually no fluctuation. They also provide maximum autonomy between the filter blocks.

Many manufacturers are concerned that when standards change, they will have to update the hardware. The ALIS V3 chip set removes this concern by integrating as many setting options as possible on the digital side in the form of software algorithms. Should standards change, all that equipment manufacturers need to do to modify their equipment is download or enter new coefficients. For example, V.34 sampling rates, including 16 kHz, are fully programmable.

The use of digital filter processing in combination with software algorithms ensures excellent transmission performance and adaptability. The ALIS V3 chip set is adaptable worldwide. International coefficient sets can be downloaded to the ALIS V3 chip set to comply with all specifications throughout the world.

Previous equipment had to operate in conjunction with external components in order to comply with local stringent requirements for communications equipment. One of these requirements can be for isolation between the analog and the digital signals for example. In the past, this was achieved using transformers, but they were awkward and heavy. They were especially a problem on PC Cards in notebooks. ALIS V3 has built-in isolation in the interface between digital and analog signals. In this overview, this is referred to as the "capacitor interface". The capacitor interface (patents pending) is an effective, lightweight solution which isolates digital from analog signals without a transformer. This also allows very flat frequency response over the entire voice band even at low frequencies.

#### Overview

The Data Access Arrangement (DAA) is no longer necessary as a number of separate components. Precision has not been lost but gained since more processing, such as equalization and gain adjustment, is now done by digital filters.

As a result of the Analog-to-Digital Converter (ADC) and Digital-to-Analog Converter (DAC) technology used, the linearity of the ALIS V3 chip set is limited only by second-order parasitic effects.

The components and functions are described in more detail in the other chapters of this overview but the key technical data is also briefly mentioned here. A complete list of features follows in the next chapter, "Features".

The main components of ALIS V3 are:

- Data Access Arrangement (DAA)

- Coder /Decoder (Codec)

- Hybrid circuit

The technology used for the two chips is:

- PSB 4595 (analog) low-power 0.8µm BiCMOS

- PSB 4596 (digital) 0.35 μm CMOS

Siemens offers a range of reference and evaluation tools for the ALIS V3 chip set. For appropriate tools, please contact your nearest Siemens representative.

## Analog Line Interface Solution ALIS

#### PSB 4595 PSB 4596

#### CMOS

#### 1.1 Features

• The ALIS V3 chip set replaces the traditional Data Access Arrangement (DAA), codec and hybrid components.

#### International features:

Programmable ring detection: international levels, and frequency coefficients are downloadable

Caller ID: detection, decoding and storage is now on-chip and programmable internationally

Programmable international DC characteristics

The ALIS V3 chip set complies with ETS 300 001, TBR21 and FCC requirements.

#### • Modem features:

**P**rogrammable sampling rates in conformance with V.34, plus future-proof 16 kHz and 32 kHz sampling rates with one fixed master clock

High performance analog-to-digital and digital-to-

analog conversion

Dual-line modem support

Voice modem with speaker phone and handset support Output pin for line monitoring.

- Isolation by means of newly developed digital capacitor interface.

- Digital interface implemented with an interface processor; SIEMENS provides configuration support upon request.

| Туре          | Ordering Code | Package   |

|---------------|---------------|-----------|

| PSB 4595 V2.1 |               | P-TSSOP24 |

| PSB 4596 V3.1 |               | P-TSSOP28 |

P-TSSOP28

#### Overview

- Analog part powered from the Tip/Ring line by an integrated voltage regulator.

- Wake-up function to support PC power management, different operating modes (sleep, conversation, ring) to cut power consumption to a minimum.

- Two-chip solution: the P-TSSOP24 and P-TSSOP28 package is PC Card compliant.

- General purpose I/O pins.

- 3 V technology Output pins are TTL compatible Input pins are 5 V tolerant.

**Block Diagram**

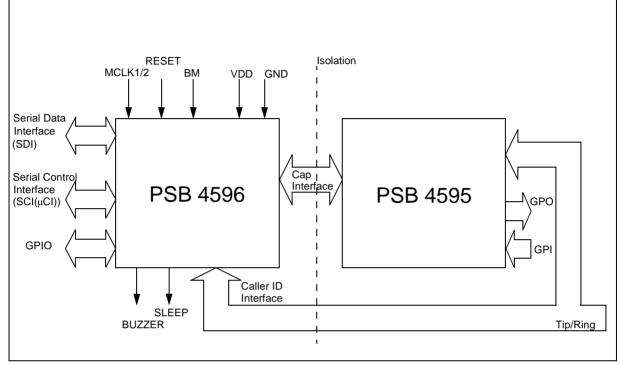

#### 2 Block Diagram

For explanation of abbreviations, see "Pin Configuration and Definitions" on page 9

Figure 1 Block Diagram of the ALIS V3 Chip Set

The Block Diagram is described in more detail in the Functional Description.

#### PSB 4595 / PSB 4596 Analog Line Interface Solution

#### **Pin Configuration and Definitions**

#### 3 Pin Configuration and Definitions

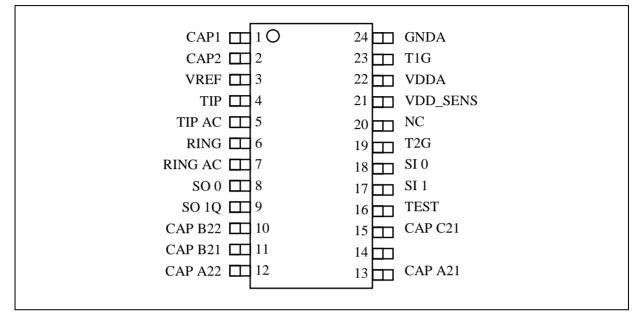

#### 3.1 Pin Configuration

Figure 2 Pin Configuration of PSB 4595 (Top View)

|                | [     | -                    |

|----------------|-------|----------------------|

| CAP_A12        | 1 O 2 | $8 \square CAP_A 11$ |

| CAP_B11        | 2 2   | $7 \square CAP_C12$  |

| CAP_B12        | 3 2   | 6 CAP_C11            |

| ID_Ain         | 4 2   | 5 VDD                |

| ID_Bin         | 5 2   | 4 GND                |

| SLEEP          | 6 2   | 3 RESET              |

| ВМ 🗖           | 7 2   | 2 GPO                |

| GPIO 🗖         | 8 2   | 1 MCLK1              |

| BUZZER         | 9 2   | $0 \prod MCLK2$      |

| SCI_CS / SWAP  | 10 1  | 9 FSC2               |

| SCI_CLK / MODE | 11 1  | 8 DAT_CLK            |

| SCI_IN         | 12 1  | 7 DAT_IN             |

| SCI_OUT        | 13 1  | 6 DAT_OUT            |

| INT 🗖          | 14 1. | 5 FSC                |

|                |       |                      |

|                |       |                      |

Figure 3 Pin Configuration of PSB 4596 (Top View)

#### PSB 4595 / PSB 4596 Analog Line Interface Solution

#### **Pin Configuration and Definitions**

#### 3.2 Pin Definitions of PSB 4595

#### Table 1 PSB 4595 Pin Definitions

| Pin No. | Symbol   | Function | Descriptions                                                                                           |

|---------|----------|----------|--------------------------------------------------------------------------------------------------------|

| 22      | VDDA     | Power    | Programmable supply for the circuitry                                                                  |

| 24      | GNDA     | Power    | Analog ground:<br>all signals are referenced to this pin                                               |

| 4       | TIP      | I        | Tip AC + DC sense input                                                                                |

| 5       | TIP_AC   |          | Tip AC sense input                                                                                     |

| 6       | RING     | I        | Ring AC + DC sense input                                                                               |

| 7       | RING_AC  | l        | Ring AC sense input                                                                                    |

| 23      | T1G      | 0        | Gate for external transistor T1 (AC/DC control)                                                        |

| 19      | T2G      | 0        | Gate for external transistor T2 (VDDA control)                                                         |

| 21      | VDD_SENS |          | VDDA sense input                                                                                       |

| 3       | VREF     | I/O      | Reference voltage: must be connected to GNDA via an external capacitor of more than 10 nF (typ. 15 nF) |

| 1       | CAP1     | I/O      | Pin for external capacitor of more than 1 $\mu$ F for DC filtering to pin CAP2                         |

| 2       | CAP2     | I/O      | See CAP1                                                                                               |

| 18      | SI_0     |          | Auxiliary input pin 0                                                                                  |

| 17      | SI_1     | I        | Auxiliary input pin 1                                                                                  |

| 8       | SO_0     | 0        | Auxiliary output pin 0                                                                                 |

| 9       | SO_1Q    | 0        | Auxiliary output pin 1                                                                                 |

| 16      | TEST     | I        | Must be connected permanently to GNDA.                                                                 |

| 13      | CAP_A21  | I        | Must be connected via a capacitor of more than 5pF to CAP_A11 (PSB 4596).                              |

| 12      | CAP_A22  | I        | Must be connected via a capacitor of more than 5pF to CAP_A12 (PSB 4596).                              |

| 11      | CAP_B21  | 0        | Must be connected via a capacitor of more than 5pF to CAP_B11 (PSB 4596).                              |

#### **Pin Configuration and Definitions**

| Pin No. | Symbol  | Function | Descriptions                                                              |

|---------|---------|----------|---------------------------------------------------------------------------|

| 10      | CAP_B22 | 0        | Must be connected via a capacitor of more than 5pF to CAP_B12 (PSB 4596)  |

| 15      | CAP_C21 | 1        | Must be connected via a capacitor of more than 5pF to CAP_C11(PSB 4596).  |

| 14      | CAP_C22 | 1        | Must be connected via a capacitor of more than 5pF to CAP_C12 (PSB 4596). |

| 20      | NC      |          | Not Connected.                                                            |

#### Table 1 PSB 4595 Pin Definitions

#### 3.3 Pin Definitions of PSB 4596

#### Table 2 PSB 4596 Pin Definitions

| Pin No. | Symbol | Function | Description                                                                                                                                                                        |

|---------|--------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 25      | VDD    | Power    | +3.3 Volt supply for the digital circuitry.                                                                                                                                        |

| 24      | GND    | Power    | Ground digital:<br>all signals are referenced to this pin.                                                                                                                         |

| 21      | MCLK1  | 1        | Master Clock1: one pin of a 16.384-MHz-<br>to-50-MHz crystal is connected. This pin<br>can also be driven by an external clock.                                                    |

| 20      | MCLK2  | 0        | Master Clock2: other pin of crystal is<br>connected. When MCLK1 is driven by an<br>external clock, this pin should be left open.                                                   |

| 23      | RESET  | I        | Reset input: resets the device (low active).                                                                                                                                       |

| 15      | FSC    | IO       | As input: Frame Synchronization Clock,<br>identifies the beginning of the frame, FSC<br>must be synchronous with DAT_CLK.<br>As output: indicates the beginning of a<br>new frame. |

| 17      | DAT_IN | 1        | Serial Data Interface (SDI) : receive data<br>Parallel Mode:16-bit line data<br>MUX Mode: 16-bit line data plus 16-bit<br>control data every FSC.                                  |

#### Pin Configuration and Definitions

| Pin No. | Symbol           | Function | Description                                                                                                                                                                    |

|---------|------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 16      | DAT_OUT          | 0        | Serial Data Interface (SDI) : transmit data,<br>tristate if not active<br>Parallel Mode: 16-bit line data<br>MUX Mode: 16-bit line data plus 16-bit<br>control data every FSC. |

| 18      | DAT_CLK          | Ю        | Data clock 256 to 2048 kHz: determines<br>the rate at which data is transferred to and<br>from the serial data interface (SDI).                                                |

| 19      | FSC2             | 0        | Second FSC to synchronize slave devices.                                                                                                                                       |

| 14      | INT              | 0        | Interrupt output pin (open drain, low active).                                                                                                                                 |

| 7       | BM               | 1        | Bus Master pin (master or slave mode).<br>'1' at the rising edge of RESET activates<br>Master Mode.                                                                            |

| 6       | SLEEP            | 0        | Indicates that PSB 4596 is in the Deep Sleep Mode.                                                                                                                             |

| 11      | SCI_CLK/<br>MODE | 1        | Serial Control Interface (SCI): clock for<br>control data.<br>'1' at the rising edge of RESET activates<br>MUX Mode.                                                           |

| 10      | SCI_CS/<br>SWAP  | 1        | Parallel Mode: Serial Control Interface<br>(SCI): chip select<br>MUX Mode: to swap 16-bit control data<br>with 16-bit line data.                                               |

| 12      | SCI_IN           | 1        | Serial Control Interface (SCI): receive control data from the $\mu$ C/DSP (not used in MUX Mode).                                                                              |

| 13      | SCI_OUT          | 0        | Serial Control Interface (SCI): transmit control data to the $\mu$ C/DSP (not used in MUX Mode).                                                                               |

| 4       | ID_Ain           | I        | Input for Caller ID comparator A (connection to TIP).                                                                                                                          |

| 5       | ID_Bin           | I        | Input for Caller ID comparator B (connection to RING).                                                                                                                         |

| 9       | BUZZER           | 0        | Output for line monitoring.                                                                                                                                                    |

#### Table 2 PSB 4596 Pin Definitions

#### PSB 4595 / PSB 4596 Analog Line Interface Solution

#### **Pin Configuration and Definitions**

| Pin No. | Symbol  | Function | Description                                                               |

|---------|---------|----------|---------------------------------------------------------------------------|

| 28      | CAP_A11 | 0        | Must be connected via a capacitor of more than 5pF to CAP_A21 (PSB 4595). |

| 1       | CAP_A12 | 0        | Must be connected via a capacitor of more than 5pF to CAP_A22 (PSB 4595). |

| 2       | CAP_B11 | I        | Must be connected via a capacitor of more than 5pF to CAP_B21 (PSB 4595). |

| 3       | CAP_B12 | I        | Must be connected via a capacitor of more than 5pF to CAP_B22 (PSB 4595). |

| 26      | CAP_C11 | 0        | Must be connected via a capacitor of more than 5pF to CAP_C21 (PSB 4595). |

| 27      | CAP_C12 | 0        | Must be connected via a capacitor of more than 5pF to CAP_C22 (PSB 4595). |

| 22      | GPO     | 0        | General purpose output pin.                                               |

|         |         |          | (e.g. to control the hook switch)                                         |

| 8       | GPIO    | IO       | General purpose I/O pin.                                                  |

#### Table 2 PSB 4596 Pin Definitions

Note: All unused input pins should be connected either to GND or VDD

#### 4 Typical Applications

As mentioned in the introduction, the ALIS V3 chip set is typically implemented in modems and fax machines.

We present below four different types of modem where the ALIS V3 chip set is an ideal solution:

- DSP-based modem (V.34, V.90)

- Host-based software modem (V.34, V90 on the host)

- Hybrid modem

- Modem with speaker path

In all the typical implementations, the innovative capacitor interface renders a transformer redundant, cutting weight and space requirements in the modems.

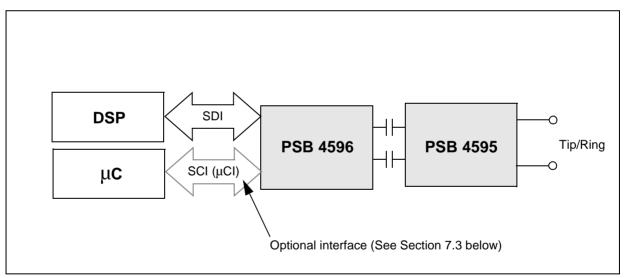

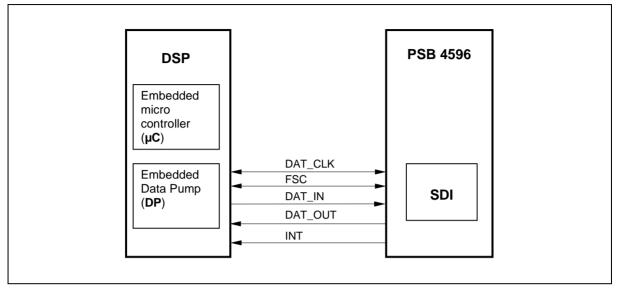

#### 4.1 The ALIS V3 Chip Set with Digital Signal Processor(DSP)-based Modem

The ALIS V3 chip set forms the front end between a DSP-based modem and the Tip/ Ring line.

Legend:

SDI: Serial Data Interface

SCI: Serial Control Interface (= µCI: Microcontroller Interface)

#### Figure 4 DSP-based Modem Application

The DSP data pump is both source and destination of digital signals which are transferred to and from the digital chip PSB 4596 via the Serial Data Interface (SDI) and Serial Control Interface (SCI). The optional SCI enables external control of the ALIS V3 chip set (see also Section 7.3 below). The SCI gives transparent access to ALIS V3 commands and signaling pins so that precalculated coefficient sets can be downloaded

from the system to the on-chip coefficient RAM (CRAM, located in the DSP) to program the filters.

Digital signals are then converted by oversampling converters to analog signals. Oversampling converters ensure the required conversion accuracy. The converted signals are applied to the capacitor interface which transfers them to the analog chip PSB4595 and thus to the Tip/Ring wires in the telephone line. Since the capacitor interface means there is no longer a transformer, it is now possible to achieve a very flat frequency response over the entire voice band, even at low frequencies. The process is reversed for incoming analog signals from the Tip/Ring wires.

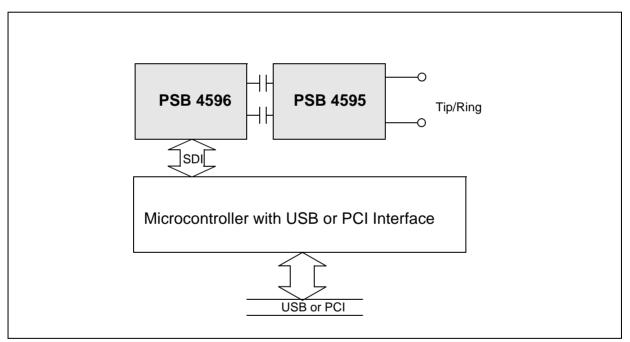

#### 4.2 The ALIS V3 Chip Set with Host-based Software Modem

The ALIS V3 chip set can also be used as a front end between V.34 and V.90 software modem applications running on a host and the Tip/Ring wires in a telephone line.

Figure 5 Software Modem Application

The digital signals travel on the USB or PCI bus and then via a FIFO structure to an SDI which carries signals to and from the digital chip PSB 4596. The digital signals are then converted by oversampling converters, as above for a DSP-based modem, and on to the Tip/Ring wires in the telephone line. The process is reversed for incoming analog signals from the Tip/Ring wires.

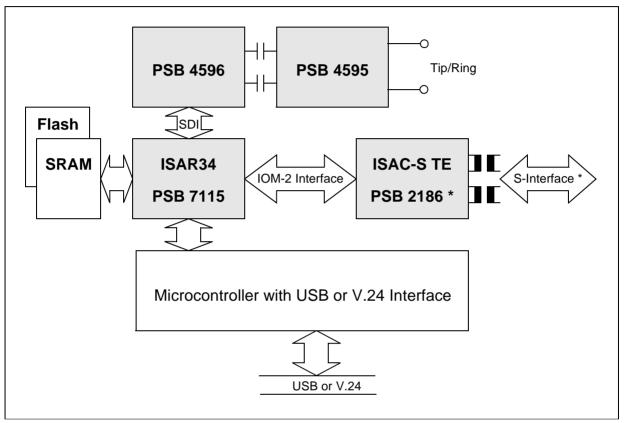

#### 4.3 Hybrid Modem (ISDN plus Analog)

The ALIS V3 chip set can be combined with a ISDN chip set to support hybrid modems, with both Tip/Ring and ISDN (S- or U-interface) connections.

Figure 6 Hybrid Modem Application, with ISDN S-Interface

The example above is shown with the ISAR34 Enhanced Data Access Controller (PSB 7115) and the ISAC-S TE ISDN Access Controller (PSB 2186) for an S-bus.

Note: If you use an ISDN U-Interface instead of an ISDN S-Interface, you must change over the ISDN chips. Replace chip ISAC-S TE PSB 2186 with IEC-Q TE PSB 2191.

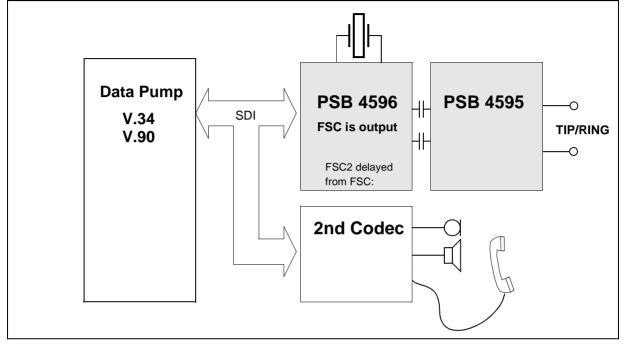

#### 4.4 Modem plus Speaker Phone

The ALIS V3 chip set could be applied as the front end for a modem plus speaker phone.

Figure 7 Application with Speaker Phone

The example here includes an 2nd Codec connected on the same SDI as the PSB 4596. This Codec is synchronised by the FSC2 (further explanation see section "Host Interface" on page 22).

#### **Functional Description**

#### 5 Functional Description

The functional description consists of a block diagram with explanation of the building blocks followed by a description of the chip set's basic principles of operation.

#### 5.1 Functional Block Diagram

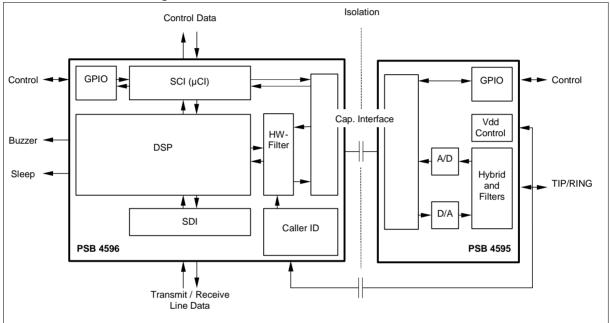

The chip set consists of two chips, PSB 4595 and PSB 4596. The following illustration shows the main building blocks:

#### Figure 8 Functional Block Diagram of the PSB 4596/4595 Chip Set

At PSB 4595 (on the right of the diagram), the Tip/Ring line interfaces with:

**VDD Control:** this sets the level of the supply voltage for the PSB 4595. The level is selected via a program.

**Hybrid and Filters:** the hybrid provides two-wire to four-wire conversion, and the analog anti-aliasing pre-filters and smoothing post-filters provide signal conditioning.

The line data path is routed from the filters to the capacitor interface through the **Analogto-Digital** (A/D) or the **Digital-to-Analog** (D/A) converters. These are over-sampling converters, to ensure the required conversion accuracy.

Capacitor Interface isolates PSB 4596 from PSB 4595.

There are two pairs of general purpose I/Os (GPIOs) at PSB 4595.

At PSB 4596, the Tip/Ring interfaces through two capacitors to the **Caller ID** input pins.

The **hardware filters** (HW Filter) handle interpolation and decimation for both Caller ID and data, before these signals travel to the digital filter structure (located in the DSP) which does equalization, gain adjustment, impedance matching, and other DAA

#### **Functional Description**

functions, in accordance with the downloaded coefficient set.

Transmit and Receive data are transferred between the PSB 4596 and the data pump through the Serial Data Interface (**SDI**).

The Serial Control Interface (**SCI**) allows external control of the ALIS V3 features and provides transparent access to ALIS V3 commands and signaling pins, so that precalculated coefficient sets can be downloaded from the system to the on-chip Coefficient RAM (CRAM, located in the DSP) to program the filters.

There is one General Purpose Output pin (**GPO**) to control the hook switch and one General Purpose IO (**GPIO**) pin.

The SLEEP pin indicates that the PSB 4596 is in the Sleep Mode.

With the BUZZER pin an external Buzzer can be connected to monitor the TIP/RING line.

#### 5.2 Basic Functionality

#### 5.2.1 Receiving and Transmitting Data

The analog voltage at Tip/Ring is converted to a 1-bit data stream in the ADC (line data). After decimation in hardware filters, the line data passes to a programmable filter structure in a DSP. These filters are programmable to international standards by downloading different national sets of coefficients. The line data is then transferred to the SDI.

When transmitting the line data to the SDI, it is also processed by programmable filters for the different national requirements before it is interpolated in a hardware filter structure and converted to an analog signal by the D/A converter.

#### 5.2.2 Input Impedance

The input impedance is also generated digitally. On the Tip/Ring side, ALIS V3 applies voltage sensing and current feeding. There is a feedback loop between the receive and the transmit path to synthesize input impedance. This means the digitized voltage is multiplied by a transfer function, converted back to analog and fed back as a current to the line. This transfer function synthesizes the ALIS V3 input impedance.

#### 5.2.3 Caller ID

The Caller ID receiver meets Bellcore specifications TR-NWT-000030 and SR-TSV-002476 for Caller IDs. In this service, the calling party's information (Calling Line Identification Presentation (CLIP)) is transmitted in the silent interval between the first and second ring. The ALIS V3 receives and stores up to 64 bytes of the 1200 baud FSK signal in a dual-paged buffer. The de-coding scheme meets the Bell 202 and ITU-T V.23 specifications.

**Interfaces Overview**

#### 6 Interfaces Overview

#### 6.1 Clocking

Any master clock frequency within the range 16.384 MHz to 50 MHz can be input to PSB 4596. Siemens recommends a a clock frequency of 24.567 MHz.

#### 6.2 Sampling Frequency

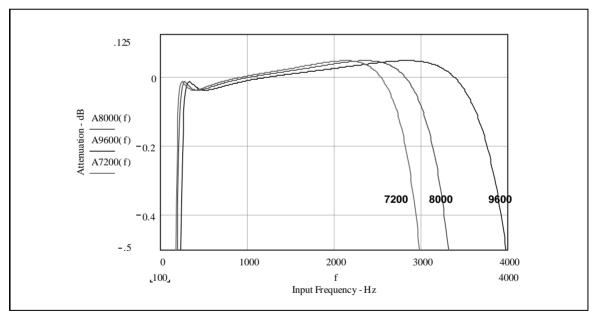

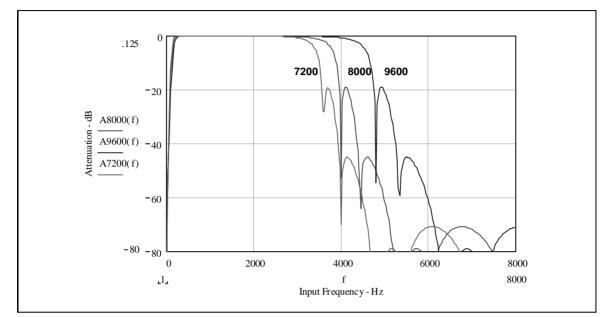

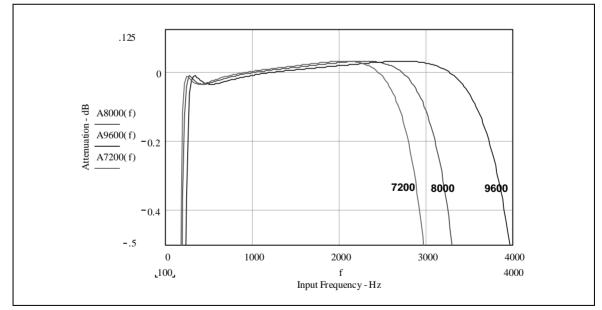

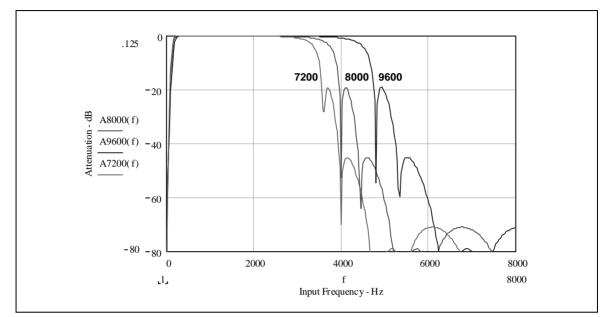

The sampling frequency can be programmed within the range 7.2 kHz to 16 kHz, accurate to less than 1 Hz. When programming different sampling frequencies, the passband behavior will also change relative to the frequency.

The diagrams below show this behavior for three example sample frequencies of 7200 Hz, 8000 Hz and 9600 Hz. (High-pass filter enabled).

Note: In V.90 modem applications, the 50/60 Hz high-pass filter can be turned off.

Figure 9 Receive Filter Passband Ripple

#### PSB 4595 / PSB 4596 Analog Line Interface Solution

**Interfaces Overview**

Figure 10 Receive Filter Response

Figure 11 Transmit Filter Passband Ripple

#### PSB 4595 / PSB 4596 Analog Line Interface Solution

**Interfaces Overview**

Figure 12 Transmit Filter Response

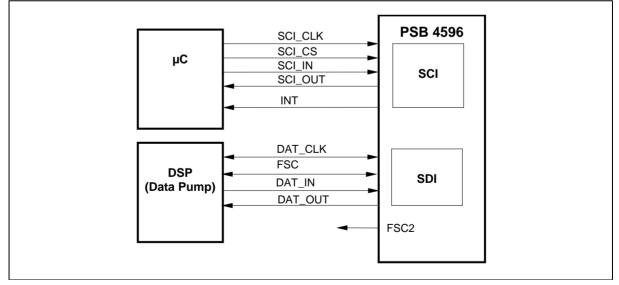

#### 6.3 Host Interface

PSB 4596 uses 5 lines to communicate with the DSP. The direction of DAT\_CLK and Frame Synchronization Clock (FSC) can be programmed by the Bus Master (BM) pin during RESET to become input or output. For modems using DSPs with embedded  $\mu$ C these lines are also used for control data.

*Note:* The ALIS V3 chip set also can also be programmed to flatten gain down to 20 Hz by switching off the high pass and by using different coefficients

#### PSB 4595 / PSB 4596 Analog Line Interface Solution

#### **Interfaces Overview**

Figure 13 Connection to a DSP

For modems with an external  $\mu$ C, or for test purposes, PSB 4596 can be programmed to use different pins for control data and line data (Parallel Mode). In this mode, the control data is transferred via the Serial Control Interface (SCI) using 4 pins. The line data is transferred via the Serial Data Interface (SDI).

Figure 14 Connection to a DSP and a  $\mu\text{C}$  using Parallel Mode

PSB 4596 can be programmed to send out a secondary frame sync pulse (pin FSC2) to indicate to a 2nd device that communication at the SDI has ended. This sync pulse is high active with a duration of 1 DAT\_CLK.

#### PSB 4595 / PSB 4596 Analog Line Interface Solution

**Interfaces Overview**

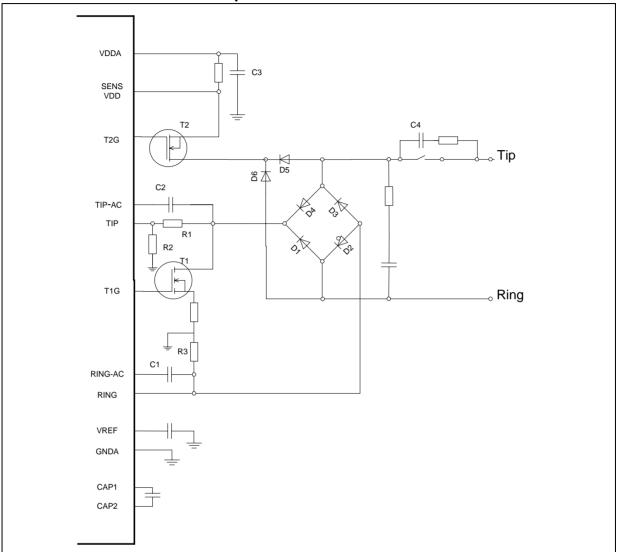

#### 6.4 Connection to the Telephone Line

#### Figure 15 Connection of PSB 4595 to the Telephone Line

As shown in the figure, PSB 4595 requires minimum components to complete the DAA circuit:

- Bridge: using Schottky diodes D1, D2, D3, D4, D5 & D6 will improve the performance at low feeding conditions. Recommended: Dual Schottky diode SIEMENS BAT 240A.

- Resistors R1, R2 & R3 for current sensing.

- Capacitors C1 & C2 for AC coupling, C3 for VDD buffering and C4 as ring capacitor. Additional Capacitors for stabilizing.

- Two transistors T1 & T2 to handle the line current. T2 must be a depletion type to handle start-up. Recommended transistors: T1: SIEMENS BSP 88; T2: SIEMENS BSP 129.

- Components for EMC protection: not shown, depending on the board layout.

#### PSB 4595 / PSB 4596 Analog Line Interface Solution

**Interfaces Overview**

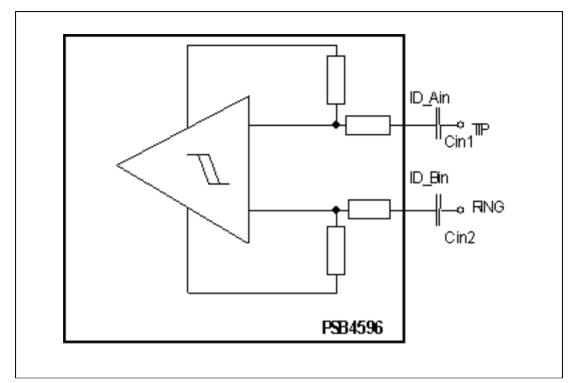

Figure 16 Caller-ID Interface Connection of the PSB 4596 to Tip/Ring

The PSB 4596 can optionally be connected to the Tip/Ring line to provide Caller-ID (CID) functions. The CID circuit requires two external capacitors.

#### PSB 4595 / PSB 4596 Analog Line Interface Solution

**Package Outlines**

Packaging

Packaging outlines for tubes, trays etc. are found in our Data Book "Package Information".

SMD = Surface Mounted Device

Dimensions are in mm

2) Does not include dambar protrusion

#### PSB 4595 / PSB 4596 Analog Line Interface Solution

#### Glossary

| 8 Glossary |                                                   |

|------------|---------------------------------------------------|

| ADC        | Analog-to-Digital Converter                       |

| ALIS V3    | Analog Line Interface Solution V3                 |

| CID        | Caller ID                                         |

| CODEC      | Coder / Decoder                                   |

| CRAM       | Coefficient RAM                                   |

| DAC        | Digital-to-Analog Converter                       |

| DSP        | Digital Signal Processing                         |

| EMC        | Electromagnetic Compatibility                     |

| ETS        | European Telecommunication Standards              |

| FCC        | Federal Communications Commission                 |

| FIFO       | First-In, First-Out                               |

| GPIO       | General Purpose Input Output                      |

| MUX        | Multiplexer                                       |

| PCI        | Peripheral Component Interface                    |

| PCM        | Pulse Code Modulation                             |

| PC Card    | Personal Computer Card (former PCMCIA)            |

| SCI        | Serial Control Interface (equivalent to $\mu$ CI) |

| SDI        | Serial Data Interface                             |

| TBR        | Technical Bases for Regulation                    |

| VDD        | Voltage Drain Drain                               |

| μCI        | Microcontroller Interface (equivalent to SCI)     |

Please see also the abbreviations in the Pin Definition Tables.