FLAT-BASE TYPE INSULATED TYPE

#### PS11011

#### INTEGRATED FUNCTIONS AND FEATURES

- Converter bridge for 3 phase AC-to-DC power conversion.

- Circuit for dynamic braking of motor regenerative energy.

- 3-phase IGBT inverter bridge configured by the latest 3rd. generation IGBT and diode technology.

- Inverter output current capability Io (Note 1):

| Type Name | 100% load  | 150% over load   |

|-----------|------------|------------------|

| PS11011   | 0.8A (rms) | 1.2A (rms), 1min |

(Note 1) : The inverter output current is assumed to be sinusoidal and the peak current value of each of the above loading cases is defined as : IoP = Io  $\times \sqrt{2}$

#### INTEGRATED DRIVE, PROTECTION AND SYSTEM CONTROL FUNCTIONS:

- For inverter side upper-leg IGBTs: Drive circuit, High voltage isolated high-speed level shifting, Short circuit protection (SC).

- Bootstrap circuit supply scheme (single drive power supply) and Under voltage protection (UV).

- For inverter side lower-leg IGBTs: Drive circuit, Short circuit protection (SC).

- Control supply circuit under- & over- voltage protection (OV/UV).

- System over temperature protection (OT). Fault output signaling circuit (Fo) and Current limit warn-

- ing signal output (CL).

- For Brake circuit IGBT : Drive circuit

- · Warning and Fault signaling:

- Fo1: Short circuit protection for lower-leg IGBTs and Input interlocking against spurious arm shoot-through.

- Fo2: N-side control supply abnormality locking (OV/UV).

- Fo3: System over-temperature protection (OT).

- CL : Warning for inverter current overload condition

- For system feedback control: Analogue signal feedback reproducing actual inverter output phase currents (3\$\, 0\$).

- Input Interface: 5V CMOS/TTL compatible, Schmitt trigger input, and Arm-Shoot-Through interlock protection.

#### **APPLICATION**

Acoustic noise-less 0.1kW/AC200V class 3 phase inverter and other motor control applications

(Fig. 1)

# FLAT-BASE TYPE INSULATED TYPE

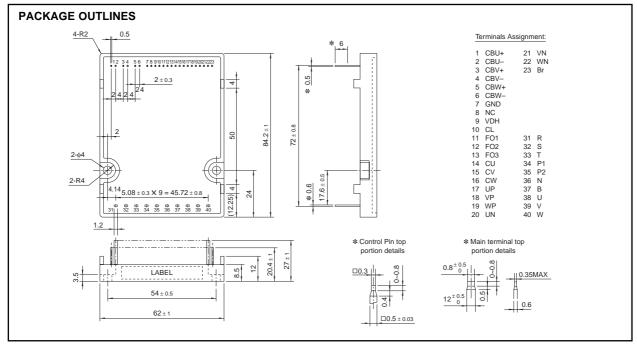

(Fig. 2)

# **MAXIMUM RATINGS** (Tj = 25°C)

# **INVERTER PART (Including Brake Part)**

| Symbol         | Item                                                       | Condition                                      | Ratings | Unit |

|----------------|------------------------------------------------------------|------------------------------------------------|---------|------|

| Vcc            | Supply voltage                                             | Applied between P2-N                           | 450     | V    |

| VCC(surge)     | Supply voltage (surge)                                     | Applied between P2-N, Surge-value              | 500     | V    |

| VP or VN       | Each output IGBT collector-emitter static voltage          | Applied between P-U, V, W, Br or U, V, W, Br-N | 600     | V    |

| VP(S) or VN(S) | Each output IGBT collector-emitter switching surge voltage | Applied between P-U, V, W, Br or U, V, W, Br-N | 600     | V    |

| ±IC(±ICP)      | Each output IGBT collector current                         | Tc = 25°C                                      | ±2 (±4) | Α    |

| IC(ICP)        | Brake IGBT collector current                               |                                                | 2 (4)   | Α    |

| IF(IFP)        | Brake diode anode current                                  | Note: "( )" means IC peak value                | 2 (4)   | Α    |

#### **CONVERTER PART**

| Symbol           | Item                                   | Condition                                  | Ratings | Unit             |

|------------------|----------------------------------------|--------------------------------------------|---------|------------------|

| VRRM             | Repetitive peak reverse voltage        |                                            | 800     | V                |

| Ea               | Recommended AC input voltage           |                                            | 220     | V                |

| lo               | DC output current                      | 3φ rectifying circuit                      | 25      | Α                |

| IFSM             | Surge (non-repetitive) forward current | 1 cycle at 60Hz, peak value non-repetitive | 138     | Α                |

| I <sup>2</sup> t | I <sup>2</sup> t for fusing            | Value for one cycle of surge current       | 80      | A <sup>2</sup> s |

### **CONTROL PART**

| Symbol   | Item                                      | Condition                                                | Ratings            | Unit |

|----------|-------------------------------------------|----------------------------------------------------------|--------------------|------|

| VDH, VDB | Supply voltage                            | Applied between VDH-GND, CBU+-CBU-, CBV+-CBV-, CBW+-CBW- | 20                 | V    |

| VCIN     | Input signal voltage                      | Applied between UP · VP · WP · UN · VN · WN · Br-GND     | <b>−</b> 0.5 ~ 7.5 | V    |

| VFO      | Fault output supply voltage               | Applied between Fo1 · Fo2 · Fo3-GND                      | <b>−</b> 0.5 ~ 7   | V    |

| IFO      | Fault output current                      | Sink current of F01 · F02 · F03                          | 15                 | mA   |

| VCL      | Current-limit warning (CL) output voltage | Applied between CL-GND                                   | <b>−</b> 0.5 ~ 7   | V    |

| ICL      | CL output current                         | Sink current of CL                                       | 15                 | mA   |

| Ico      | Analogue current signal output current    | Sink current of CU · CV · CW                             | ±1                 | mA   |

# FLAT-BASE TYPE INSULATED TYPE

### **TOTAL SYSTEM**

| Symbol | Item                              | Condition                                                                          | Ratings           | Unit  |

|--------|-----------------------------------|------------------------------------------------------------------------------------|-------------------|-------|

| Tj     | Junction temperature              | (Note 2)                                                                           | <b>−20 ~ +125</b> | °C    |

| Tstg   | Storage temperature               | _                                                                                  | <b>−40 ~ +125</b> | °C    |

| Tc     | Module case operating temperature | (Fig. 3)                                                                           | <b>−20 ~ +100</b> | °C    |

| Viso   | Isolation voltage                 | 60 Hz sinusoidal AC applied between all terminals and the base plate for 1 minute. | 2500              | Vrms  |

|        | Mounting torque                   | Mounting screw: M3.5                                                               | 0.78 ~ 1.27       | kg-cm |

Note 2) The item defines the maximum junction temperature for the power elements (IGBT/Diode) of the ASIPM to ensure safe operation. However, these power elements can endure junction temperature as high as 150°C instantaneously. To make use of this additional temperature allowance, a detailed study of the exact application conditions is required and, accordingly, necessary information is requested to be provided before use.

# CASE TEMPERATURE MEASUREMENT POINT (3mm from the base surface)

### THERMAL RESISTANCE

| Cumahad    | lta m                               | O and disting                                  |   | 1.1  |       |      |

|------------|-------------------------------------|------------------------------------------------|---|------|-------|------|

| Symbol     | Item                                | Condition                                      |   | Тур. | Max.  | Unit |

| Rth(j-c)Q  | Junction to case Thermal Resistance | Inverter IGBT (1/6)                            | _ | _    | 7.3   | °C/W |

| Rth(j-c)F  |                                     | Inverter FWDi (1/6)                            | _ | _    | 6.1   | °C/W |

| Rth(j-c)QB |                                     | Brake IGBT                                     | _ | _    | 7.3   | °C/W |

| Rth(j-c)FB |                                     | Brake FWDi                                     | _ | _    | 6.1   | °C/W |

| Rth(j-c)FR |                                     | Converter Di (1/6)                             | _ | _    | 4.8   | °C/W |

| Rth(c-f)   | Contact Thermal Resistance          | Case to fin, thermal grease applied (1 Module) | _ | _    | 0.053 | °C/W |

# **ELECTRICAL CHARACTERISTICS** (Tj = 25°C, VDH = 15V, VDB = 15V unless otherwise noted)

| Symbol     | Item                                                 | Condition                                                           |                                                             | Ratings                           |        |      |

|------------|------------------------------------------------------|---------------------------------------------------------------------|-------------------------------------------------------------|-----------------------------------|--------|------|

| Symbol     |                                                      |                                                                     |                                                             | Тур.                              | Max.   | Unit |

| VCE(sat)   | Collector-emitter saturation voltage                 | VDH = VDB = 15V, $Input = ON$ , $Tj = 25$ °C, $IC = 2A$             | — — 2.9                                                     |                                   |        | V    |

| VEC        | FWDi forward voltage                                 | $Tj = 25^{\circ}C$ , $IC = -2A$ , $Input = OFF$                     | _                                                           | _                                 | 2.9    | V    |

| VCE(sat)Br | Brake IGBT<br>Collector-emitter saturation voltage   | V <sub>DH</sub> = 15V, Input = ON, Tj = 25°C, IC = 2A               | _                                                           | _                                 | 3.5    | V    |

| VFBr       | Brake diode forward voltage                          | Tj = 25°C, IF = 2A, Input = OFF                                     | 2.9                                                         |                                   | V      |      |

| IRRM       | Converter diode reverse current                      | VR = VRRM, Tj = 125°C                                               | _                                                           | _                                 | 8      | mA   |

| VFR        | Converter diode voltage                              | Tj = 25°C, IF = 5A                                                  | <u> </u>                                                    |                                   | V      |      |

| ton        |                                                      | 1/2 Bridge inductive load, Input = ON                               | 0.3                                                         | 0.6                               | 1.5    | μs   |

| tc(on)     | Switching times                                      | Vcc = 300V, lc = 2A, Tj = 125°C                                     | _                                                           | 0.2                               | 0.6    | μs   |

| toff       | Ownering times                                       | VDH = 15V, VDB = 15V                                                | _                                                           | 1.1                               | 1.8    | μs   |

| tc(off)    |                                                      | Note : ton, toff include delay time of the internal control circuit |                                                             | 0.35                              | 1.0    | μs   |

| trr        | FWD reverse recovery time                            |                                                                     |                                                             | 0.1                               | _      | μs   |

|            | Short circuit endurance                              | Vcc ≤ 400V, Input = ON (one-shot)                                   | No destruction                                              |                                   |        |      |

|            | (Output, Arm, and Load,                              | Tj = 125°C start                                                    |                                                             | Fo output by protection operation |        |      |

|            | Short Circuit Modes) $13.5V \le VDH = VDB \le 16.5V$ |                                                                     |                                                             |                                   |        |      |

|            |                                                      | Vcc ≤ 400V, Tj ≤ 125°C,                                             | No destruction     No protecting operation     No Fo output |                                   |        |      |

|            | Switching SOA                                        | Ic < IoL(CL) operation level, Input = ON                            |                                                             |                                   | ration |      |

|            |                                                      | 13.5V ≤ VDH = VDB ≤ 16.5V                                           | 140100                                                      | Juipui                            |        |      |

# FLAT-BASE TYPE INSULATED TYPE

#### **ELECTRICAL CHARACTERISTICS** (Tj = 25°C, VDH = 15V, VDB = 15V unless otherwise noted)

| Symbol    | Item                                                   |               | Condition                                                               |                 | Ratings    |       |       | l lmit |     |

|-----------|--------------------------------------------------------|---------------|-------------------------------------------------------------------------|-----------------|------------|-------|-------|--------|-----|

| Symbol    |                                                        |               |                                                                         |                 | Min.       | Тур.  | Max.  | Unit   |     |

| IDH       | Circuit current                                        |               | VDH = 15V, VCIN = 5V                                                    |                 | _          | _     | 150   | mA     |     |

| Vth(on)   | Input on threshold voltage                             |               |                                                                         |                 |            | 8.0   | 1.4   | 2.0    | V   |

| Vth(off)  | Input off threshold voltage                            |               |                                                                         |                 |            | 2.5   | 3.0   | 4.0    | V   |

| Ri        | Input pull-up resistor                                 |               | Integrated between inpu                                                 |                 | 1          | _     | 150   | _      | kΩ  |

| fPWM      | PWM input frequency                                    |               | Tc ≤ 100°C, Tj ≤ 125°C                                                  |                 |            | 2     | _     | 20     | kHz |

| txx       | Allowable input on-pulse wi                            |               | $VDH = 15V, TC = -20^{\circ}C$                                          |                 | (Note 3)   | 1     | _     | 500    | μs  |

| tdead     | Allowable input signal dead blocking arm shoot-through |               | Relates to corresponding (Except brake part) Tc =                       |                 | 0          | 2.2   | _     | _      | μs  |

| tint      | Input inter-lock sensing                               |               | Relates to corresponding                                                | input (Except b | rake part) | _     | 65    | 100    | ns  |

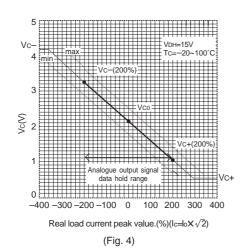

| Vco       |                                                        |               | Ic = 0A                                                                 | VDH = 15V       |            | 1.87  | 2.27  | 2.57   | V   |

| Vc+(200%) | Analogue signal linearity wi                           | th            | Ic = IOP(200%)                                                          | Tc = -20°C      | ~ +100°C   | 0.77  | 1.17  | 1.47   | V   |

| Vc-(200%) | output current                                         |               | Ic = -Iop(200%)                                                         |                 | (Fig. 4)   | 2.97  | 3.37  | 3.67   | V   |

| ΙΔVcol    | Offset change area vs temperature                      |               | VDH = 15V, Tc = -20°C ~ +100°C                                          |                 | _          | 15    | _     | mV     |     |

| VC+       | Analogue signal output voltage limit                   |               | Ic > IOP(200%), VDH =                                                   |                 |            | _     | _     | 0.7    | V   |

| Vc-       |                                                        |               | (Fig. 4)                                                                |                 | 4.0        | _     | _     | V      |     |

| ΔVc(200%) | Analogue signal over all linear variation              |               | Vco-Vc±(200%)                                                           |                 | _          | 1.1   | _     | V      |     |

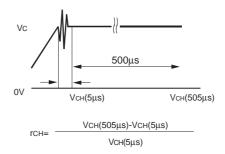

| гсн       | Analogue signal data hold accuracy                     |               | Correspond to max. 500μs data hold period only, Ic = IOP(200%) (Fig. 5) |                 | -5         | _     | 5     | %      |     |

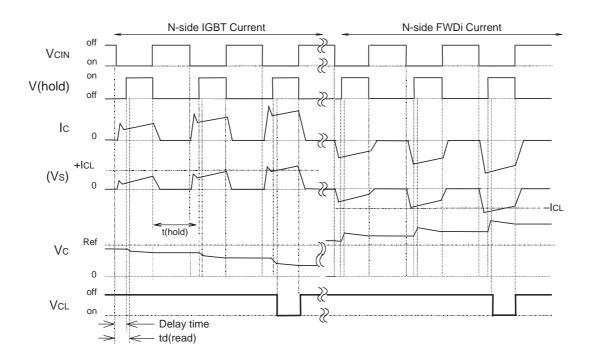

| td(read)  | Analogue signal reading tim                            | ne            | After input signal trigge                                               | r point         | (Fig. 8)   | _     | 3     | _      | μs  |

| ±loL      | Current limit warning (CL) op                          | eration level | VDH =15V, Tc = -20°C                                                    | ~ +100°C        | (Note 4)   | 2.64  | 3.10  | 3.60   | Α   |

| ICL(H)    | Signal output current of                               | Idle          | Open collector output                                                   |                 | _          | _     | 1     | μΑ     |     |

| ICL(L)    | CL operation                                           | Active        |                                                                         |                 | _          | 1     | _     | mA     |     |

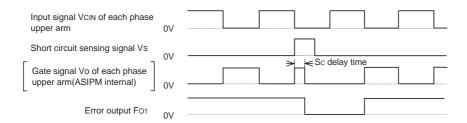

| SC        | Short circuit over current tri                         | p level       | Tj = 25°C                                                               | (Fig. 7)        | (Note 5)   | 3.50  | 6.00  | 9.60   | Α   |

| ОТ        |                                                        | Trip level    | , , , ,                                                                 |                 | 100        | 110   | 120   | °C     |     |

| OTr       | Over temperature protection                            | Reset level   | VDH =15V                                                                |                 |            | _     | 90    | _      | °C  |

| UVDH      |                                                        | Trip level    |                                                                         |                 |            | 11.05 | 12.00 | 12.75  | V   |

| UVDHr     |                                                        | Reset level   |                                                                         |                 |            | 11.55 | 12.50 | 13.25  | V   |

| OVDH      |                                                        | Trip level    |                                                                         |                 |            | 18.00 | 19.20 | 20.15  | V   |

| OVDHr     | Supply circuit under &                                 | Reset level   | $Tc = -20^{\circ}C \sim +100^{\circ}C$                                  |                 |            | 16.50 | 17.50 | 18.65  | V   |

| UVDB      | over voltage protection                                | Trip level    | Tj ≤ 125°C                                                              |                 |            | 10.0  | 11.0  | 12.0   | V   |

| UVDBr     |                                                        | Reset level   |                                                                         |                 |            | 10.5  | 11.5  | 12.5   | V   |

| tdV       |                                                        | Filter time   |                                                                         |                 |            | _     | 10    | _      | μs  |

| IFO(H)    |                                                        | Idle          |                                                                         |                 |            | _     | _     | 1      | μA  |

| IFO(L)    | Fault output current                                   | Active        | Open collector output                                                   |                 |            | _     | 1     | _      | mA  |

| J(L)      |                                                        | 150           |                                                                         |                 |            |       |       |        |     |

(Note 3): (a) Allowable minimum input on-pulse width: This item applies to P-side circuit only.

(b) Allowable maximum input on-pulse width: This item applies to both P-side and N-side circuits excluding the brake circuit.

(Note4): CL output: The "current limit warning (CL) operation circuit outputs warning signal whenever the arm current exceeds this limit. The circuit is reset automatically by the next input signal and thus, it operates on a pulse-by-pulse scheme.

(Note5): The short circuit protection works instantaneously when a high short circuit current flows through an internal IGBT rising up momentarily. The protection function is, thus meant primarily to protect the ASIPM against short circuit distraction. Therefore, this function is not recommended to be used for any system load current regulation or any over load control as this might, cause a failure due to excessive temperature rise. Instead, the analogue current output feature or the over load warning feature (CL) should be appropriately used for such current regulation or over load control operation. In other words, the PWM signals to the ASIPM should be shut down, in principle, and not to be restarted before the junction temperature would recover to normal, as soon as a fault is feed back from its Fo1 pin of the ASIPM indicating a short circuit situation.

#### **RECOMMENDED CONDITIONS**

| Symbol                       | Item                            | Condition                                                | Ratings    | Unit |

|------------------------------|---------------------------------|----------------------------------------------------------|------------|------|

| Vcc                          | Supply voltage                  | Applied across P2-N terminals                            | 400 (max.) | V    |

| VDH, VDB                     | Control supply voltage          | Applied between VDH-GND, CBU+-CBU-, CBV+-CBV-, CBW+-CBW- | 15±1.5     | V    |

| $\Delta V$ DH, $\Delta V$ DB | Supply voltage ripple           |                                                          | ±1 (max.)  | V/µs |

| VCIN(on)                     | Input on voltage                |                                                          | 0 ~ 0.3    | V    |

| VCIN(off)                    | Input off voltage               |                                                          | 4.8 ~ 5.0  | V    |

| fPWM                         | PWM Input frequency             | Using application circuit                                | 2 ~ 20     | kHz  |

| tdead                        | Arm shoot-through blocking time | Using application circuit                                | 2.2 (min.) | μs   |

FLAT-BASE TYPE INSULATED TYPE

Fig. 4 OUTPUT CURRENT ANALOGUE SIGNALING LINEARITY

Fig. 5 OUTPUT CURRENT ANALOGUE SIGNALING "DATA HOLD" DEFINITION

Note; Ringing happens around the point where the signal output voltage changes state from "analogue" to "data hold" due to test circuit arrangement and instrumentational trouble. Therefore, the rate of change is measured at a 5 µs delayed point.

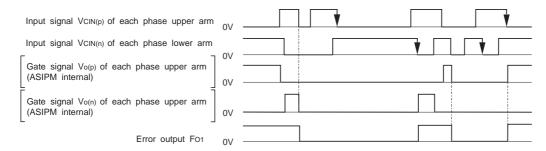

Fig. 6 INPUT INTERLOCK OPERATION TIMING CHART

Note: Input interlock protection circuit; It is operated when the input signals for any upper-arm / lower-arm pair of a phase are simultaneously in "LOW" level.

By this interlocking, both upper and lower IGBTs of this mal-triggered phase are cut off, and "Fo" signal is outputted. After an "input interlock" operation the circuit is latched. The "Fo" is reset by the high-to-low going edge of either an upper-leg, or a lower-leg input, whichever comes in later.

Fig. 7 TIMING CHART AND SHORT CIRCUIT PROTECTION OPERATION

Note: Short circuit protection operation. The protection operates with "Fo" flag and reset on a pulse-by-pulse scheme. The protection by gate shutdown is given only to the IGBT that senses an overload (excluding the IGBT for the "Brake").

FLAT-BASE TYPE INSULATED TYPE

Fig. 8 INVERTER OUTPUT ANALOGUE CURRENT SENSING AND SIGNALING TIMING CHART

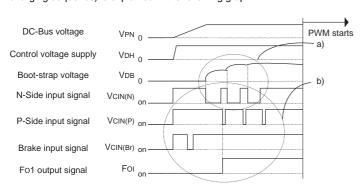

# Fig. 9 START-UP SEQUENCE

Normally at start-up, Fo and CL output signals will be pulled-up High to Supply voltage (OFF level); however, Fo1 output may fall to Low (ON) level at the instant of the first ON input pulse to an N-Side IGBT. This can happen particularly when the boot-strap capacitor is of large size. Fo1 resetting sequence (together with the boot-strap charging sequence) is explained in the following graph

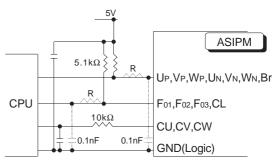

#### Fig. 10 RECOMMENDED I/O INTERFACE CIRCUIT

#### a) Boot-strap charging scheme :

Apply a train of short ON pulses at all N-IGBT input pins for adequate charging (pulse width = approx. 20μs number of pulses =10 ~ 500 depending on the boot-strap capacitor size)

#### b) Fo1 resetting sequence:

Apply ON signals to the following input pins : Br  $\to$  Un/Vn/Wn  $\to$  Up/Vp/Wp in that order.