# MICROSTEPPING MOTOR CONTROLLER WITH DUAL DAC

# ■ GENERAL DESCRIPTION

NJU39612 is a dual 7-bit+sign; Digital-to-Analog Converter (DAC) developed to be used in micro stepping applications together with the dual stepper motor driver. The NJU39612 has a set of input registers connected to an 8-bit data port for easy interfacing directly to a microprocessor. Two registers are used to store the data for each seven-bit DAC, the eighth bit being a sign bit (sign/magnitude coding).

■ PACKAGE OUTLINE

NJU39612E2

### ■ FEATURES

- Analog control voltages from 3V down to 0.0V

- High-speed microprocessor interface

- Full -scale error ±1 LSB

- Fast conversion speed 3 μs

- · Matches the dual stepper motor drivers

- Package EMP20

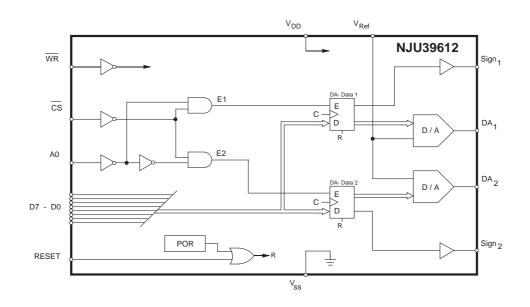

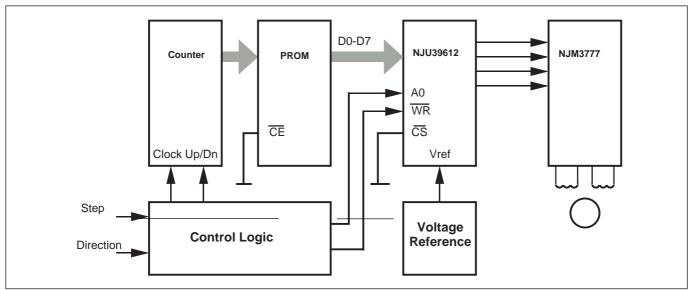

### BLOCK DIAGRAM

#### Figure 1. Block Diagram

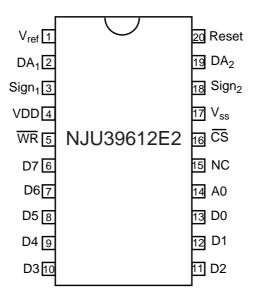

# ■ PIN CONFIGURATION

# Figure 2. Pin configuration

# ■ PIN DESCRIPTION

| EMP | Symbol                  | Description                                                                                                                               |

|-----|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | V <sub>Ref</sub>        | Voltage reference supply pin, 2.5 V nominal (3.0 V maximum)                                                                               |

| 2   |                         | Digital-to-Analog 1, voltage output. Output between 0.0 V and V <sub>ref</sub> - 1 LSB.                                                   |

| 3   | Sign                    | Sign 1, TTL/CMOS level. To be connected directly to NJM377x phase input. Databit D7 is transfered nor inverted from NJU39612 data input.  |

| 4   | V <sub>DD</sub>         | Voltage Drain-Drain, logic supply voltage. Normally +5 V.                                                                                 |

| 5   | WR                      | Write, TTL/CMOS level, input for writing to internal registers. Data is clocked into flip flops on positive edge.                         |

| 6   | D7                      | Data 7, TTL/CMOS level, input to set data bit 7 in data word.                                                                             |

| 7   | D6                      | Data 6, TTL/CMOS level, input to set data bit 6 in data word.                                                                             |

| 8   | D5                      | Data 5, TTL/CMOS level, input to set data bit 5 in data word.                                                                             |

| 9   | D4                      | Data 4, TTL/CMOS level, input to set data bit 4 in data word.                                                                             |

| 10  | D3                      | Data 3, TTL/CMOS level, input to set data bit 3 in data word.                                                                             |

| 11  | D2                      | Data 2, TTL/CMOS level, input to set data bit 2 in data word.                                                                             |

| 12  | D1                      | Data 1, TTL/CMOS level, input to set data bit 1 in data word.                                                                             |

| 13  | D0                      | Data 0, TTL/CMOS level, input to set data bit 0 in data word.                                                                             |

| 14  | A0                      | Address 0, TTL/CMOS level, input to select data transfer, A0 selects between cannel 1 (A0 = LOW) and channel 2 (A0 = HIGH).               |

| 15  | NC                      | Not connected                                                                                                                             |

| 16  | CS                      | Chip Select, TTL/CMOS level, input to select chip and activate data transfer from data inputs. LOW level = chip is selected.              |

| 17  | $V_{ss}$                | Voltage Source-Source. Ground pin, 0 V reference for all signals and measurements unless otherwise noted.                                 |

| 18  | $\operatorname{Sign}_2$ | Sign 2. TTL/CMOS level. To be connected directly to NJM377x phase input. Data bit D7 is transfered non-inverted from NJU39612 data input. |

| 19  | $DA_2$                  | Digital-to-Analog 2, voltage output. Output between 0.0 V and V <sub>ref</sub> - 1 LSB.                                                   |

| 20  | Reset                   | Reset, digital input resetting internal registers. HIGH level = Reset, $V_{Res} \ge 3.5 V = HIGH$ level. Pulled low internally.           |

### ■ DEFINITION OF TERMS

#### Resolution

Resolution is defined as the reciprocal of the number of discrete steps in the DAC output. It is directly related to the number of switches or bits within the DAC. For example, NJU39612 has 2<sup>7</sup>, or 128, output levels and therefor has 7 bits resolution. Remember that this is not equal to the number of microsteps available.

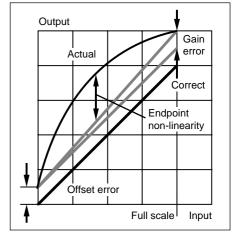

### **Linearity Error**

Linearity error is the maximum deviation from a straight line passing through the end points of the DAC transfer characteristic. It is measured after adjusting for zero and full scale. Linearity error is a parameter intrinsic to the device and cannot be externally adjusted.

#### **Power Supply Sensitivity**

Power supply sensitivity is a measure of the effect of power supply changes on the DAC full-scale output.

#### **Settling Time**

Full-scale current settling time requires zero-to-full-scale or full-scale-to-zero output change. Settling time is the time required from a code transition until the DAC output reaches within  $\pm 1/2$ LSB of the final output value.

#### **Full-scale Error**

Full-scale error is a measure of the output error between an ideal DAC and the actual device output.

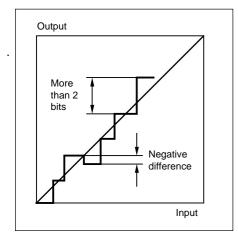

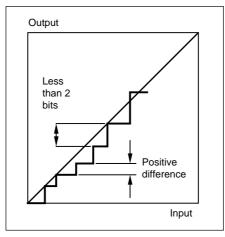

#### **Differential Non-linearity**

The difference between any two consecutive codes in the transfer curve from the theoretical 1LSB, is differential non-linearity

#### Monotonic

If the output of a DAC increases for increasing digital input code, then the DAC is monotonic. A 7-bit DAC which is monotonic to 7 bits simply means that increasing digital input codes will produce an increasing analog output. NJU39612 is monotonic to 7 bits.

### ■ FUNCTIONAL DESCRIPTION

Each DAC channel contains one register and a D/A converter. A block diagram is shown on the first page. The sign outputs generate the phase shifts, i.e., they reverse the current direction in the phase windings.

#### **Data Bus Interface**

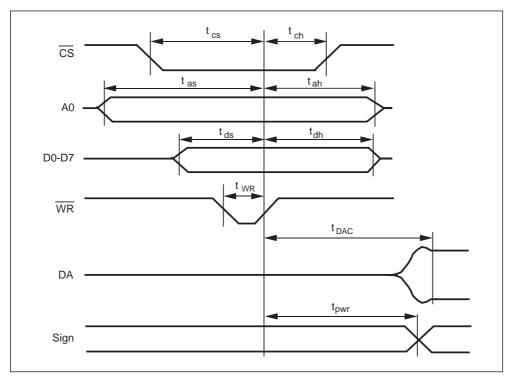

NJU39612 is designed to be compatible with 8-bit microprocessors such as the 6800, 6801, 6803, 6808, 6809, 8051, 8085, Z80 and other popular types and their 16/32 bit counter parts in 8 bit data mode. The data bus interface consists of 8 data bits, write signal, chip select, and two address pins. All inputs are TTL-compatible (except reset). The address pin control data transfer to the two internal D-type registers. Data is transferred according to figure 7 and on the positive edge of the write signal.

Figure 3. Errors in D/A conversion. Differential non-linearity of more than 1 bit, output is non-monotonic.

Figure 4. Errors in D/A conversion. Differential non-linearity of less than 1 bit, output is monotonic.

Figure 5. Errors in D/A conversion. Non-linearity, gain and offset errors.

New Japan Radio Co., Ltd.

# Current Direction, Sign, & Sign,

These bits are transferred from  $D_7$  when writing in the respective DA register.  $A_0$  must be set according to the data transfer table in figure 7.

### $DA_1$ and $DA_2$

These are the two outputs of DAC1 and DAC2. Input to the DACs are internal data bus  $(Q_{61} \dots Q_{01})$  and  $(Q_{62} \dots Q_{02})$ .

# Reference Voltage V<sub>Ref</sub>

$V_{\text{Ref}}$  is the analog input for the two DACs. Special care in layout, gives a very low voltage drop from pin to resistor. Any  $V_{\text{Ref}}$  between 0.0 V and  $V_{\text{DD}}$  can be applied, but output might be non-linear above 3.0 V.

#### **Power-on Reset**

This function automatically resets all internal flip flops at power-on. This results in  $V_{ss}$  voltage at both DAC outputs and all digital outputs.

#### Reset

If Reset is not used, leave it disconnected. Reset can be used to measure leakage currents from V\_DD.

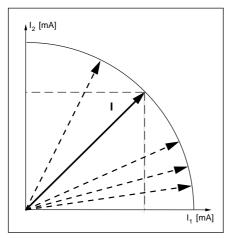

Figure 6a. Assuming that torque is proportional to the current in resp. winding it is possible to draw figure 8b.

Figure 6b. An example of accessible positions with a given torque deviation/fullstep. Note that 1:st  $\mu$ step sets highest resolution. Data points are exaggerated for illustration purpose. TNom = code 127.

| CS | A0 | Data Transfer                     |

|----|----|-----------------------------------|

| 0  | 0  | D7 —> Sign1, (D6—D0) —> (Q61—Q01) |

| 0  | 1  | D7 —> Sign2, (D6—D0) —> (Q62—Q02) |

| 1  | Х  | No Transfer                       |

Figure 7. Table showing how data is transfered inside NJU39612.

# ■ ABSOLUTE MAXIMUM RATINGS

| Parameter                     | Pin no. | Symbol           | Min  | Max                   | Unit |  |

|-------------------------------|---------|------------------|------|-----------------------|------|--|

| Voltage                       |         |                  |      |                       |      |  |

| Supply                        | 4       | V <sub>DD</sub>  | -    | 6                     | V    |  |

| Logic inputs                  | 5-14,16 | V                | -0.3 | V <sub>DD</sub> + 0.3 | V    |  |

| Reference input               | 1       | $V_{Ref}$        | -0.3 | V <sub>DD</sub> + 0.3 | V    |  |

| Current                       |         |                  |      |                       |      |  |

| Logic inputs                  | 5-14,16 | I,               | -0.4 | +0.4                  | mA   |  |

| Temperature                   |         |                  |      |                       |      |  |

| Storage temperature           |         | T <sub>stg</sub> | -55  | +150                  | °C   |  |

| Operating ambient temperature |         | T <sub>opr</sub> | -20  | +85                   | °C   |  |

# ■ RECOMMENDED OPERATING CONDITIONS

| Parameter                |                                 | Min  | Тур | Max  | Unit |

|--------------------------|---------------------------------|------|-----|------|------|

| Supply voltage           | V <sub>DD</sub>                 | 4.75 | 5.0 | 5.25 | V    |

| Reference voltage        | V <sub>Ref</sub>                | 0    | 2.5 | 3.8  | V    |

| Rise and fall time of WR | t <sub>r</sub> , t <sub>r</sub> | -    | -   | 1    | μs   |

# ■ ELECTRICAL CHARACTERISTICS

Electrical characteristics over recommended operating conditions.

| Parameter                       | Symbol            | Conditions                                                 | Min   | Тур | Max              | Unit |

|---------------------------------|-------------------|------------------------------------------------------------|-------|-----|------------------|------|

| Logic Input                     |                   |                                                            |       |     |                  |      |

| Reset logic HIGH input voltage  | V <sub>IHR</sub>  |                                                            | 3.5   | -   | -                | V    |

| Reset logic LOW input voltage   |                   |                                                            | -     | -   | 0.1              | V    |

| Logic HIGH input voltage        | V <sub>IH</sub>   |                                                            | 2.0   | -   | -                | V    |

| Logic LOW input voltage         | V <sub>IL</sub>   |                                                            | -     | -   | 0.8              | V    |

| Reset input current             | I <sub>IR</sub>   | $V_{ss} < V_{IR} < V_{DD}$                                 | -0.01 | -   | 1                | mΑ   |

| Input current, other inputs     | I,                | $V_{ss} < V_{I} < V_{DD}$                                  | -1    | -   | 1                | μA   |

| Input capacitance               |                   |                                                            | -     | 3   | -                | pF   |

| Internal Timing Characteristics |                   |                                                            |       |     |                  |      |

| Address setup time              | t <sub>as</sub>   | Valid for A0                                               | 60    | -   | -                | ns   |

| Data setup time                 | t <sub>ds</sub>   | Valid for D0 - D7                                          | 60    | -   | -                | ns   |

| Chip select setup time          | t <sub>cs</sub>   |                                                            | 70    | -   | -                | ns   |

| Address hold time               | t <sub>ah</sub>   |                                                            | -     | -   | 0                | ns   |

| Data hold time                  | t <sub>dh</sub>   |                                                            | -     | -   | 0                | ns   |

| Chip select hold time           | t <sub>ch</sub>   |                                                            | -     | -   | 0                | ns   |

| Write cycle length              | t <sub>wR</sub>   |                                                            | 50    | -   | -                | ns   |

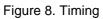

| Reset cycle length              | t <sub>res</sub>  |                                                            | 80    | -   | -                | ns   |

| Reference Input                 |                   |                                                            |       |     |                  |      |

| Input resistance                | $R_{ref}$         |                                                            | 6     | 9   | -                | kohm |

| Logic Outputs                   |                   |                                                            |       |     |                  |      |

| Logic HIGH output current       | I <sub>он</sub>   | $V_0 = 2.4 V$                                              | -     | -13 | -5               | mA   |

| Logic LOW output current        | I <sub>oL</sub>   | $V_0 = 0.4 V$                                              | 2     | 5   | -                | mA   |

| Write propagation delay         | t <sub>pwr</sub>  | From positive edge of WR.                                  | -     | 30  | 100              | ns   |

|                                 |                   | Outputs valid, C <sub>load</sub> = 120 pF                  |       |     |                  |      |

| Reset propagation delay         | t <sub>pres</sub> | From positive edge of Reset to                             | -     | 60  | 150              | ns   |

|                                 |                   | outputs valid, C <sub>load</sub> = 120 pF                  |       |     |                  |      |

| DAC Outputs                     |                   | Reset open, V <sub>Ref</sub> = 2.5 V                       |       |     |                  |      |

| Nominal output voltage          | V <sub>DA</sub>   |                                                            | 0     | -   | V <sub>Ref</sub> |      |

|                                 | 5,1               |                                                            |       |     | - 1LSB           | V    |

| Resolution                      |                   |                                                            | -     | 7   | -                | Bits |

| Offset error                    |                   |                                                            | -     | 0.2 | 0.5              | LSB  |

| Gain error                      |                   |                                                            | -     | 0.1 | 0.5              | LSB  |

| Endpoint nonlinearity           |                   |                                                            | -     | 0.2 | 0.5              | LSB  |

| Differential nonlinearity       |                   |                                                            | -     | 0.2 | 0.5              | LSB  |

| Load error                      |                   | (V <sub>DA</sub> , unloaded - V <sub>DA</sub> , loaded)    | -     | 0.1 | 0.5              | LSB  |

|                                 |                   | R <sub>load</sub> = 2.5 kohm, Code 127 to DAC              |       |     |                  |      |

| Power supply sensitivity        |                   | Code 127 to DAC                                            | -     | 0.1 | 0.3              | LSB  |

|                                 |                   | 4.75 V < V <sub>DD</sub> < 5.25 V                          |       |     |                  |      |

| Conversion speed                | t <sub>DAC</sub>  | For a full-scale transition to ±0.5 LSB                    | -     | 3   | 8                | μs   |

|                                 |                   | of final value, $R_{load} = 2.5$ kohm, $C_{load} = 50$ pF. |       |     |                  |      |

Figure 9. Timing of Reset

# APPLICATIONS INFORMATION

### How Many Microsteps?

The number of true microsteps that can be obtained depends upon many different variables, such as the number of data bits in the Digital-to-Analog converter, errors in the converter, acceptable torque ripple, single- or double-pulse programming, the motor's electrical, mechanical and magnetic characteristics, etc. Many limits can be found in the motor's ability to perform properly; overcome friction, repeatability, torque linearity, etc. It is important to realize that the number of current levels, 128 (2<sup>7</sup>), is *not* the number of steps available. 128 is the number of current levels (reference voltage levels) available from each driver stage. Combining a current level in one winding with any of 128 other current levels in the other winding will make up 128 current levels. So expanding this, it is possible to get 16,384 (128 • 128) combinations of different current levels in the two windings. Remember that these 16,384 micropositions are not all useful, the torque will vary from 100% to 0% and some of the options will make up the same position. For instance, if the current level in one winding is OFF (0%) you can still vary the current in the other winding in 128 levels. All of these combinations will give you the same position *but* a varying torque.

### **Typical Application**

The microstepper solution can be used in a system with or without a microprocessor.

Without a microprocessor, a counter addresses a ROM where appropriate step data is stored. Step and Direction are the input signals which represent clock and up / down of counter. This is the ideal solution for a system where there is no microprocessor or it is heavily loaded with other tasks.

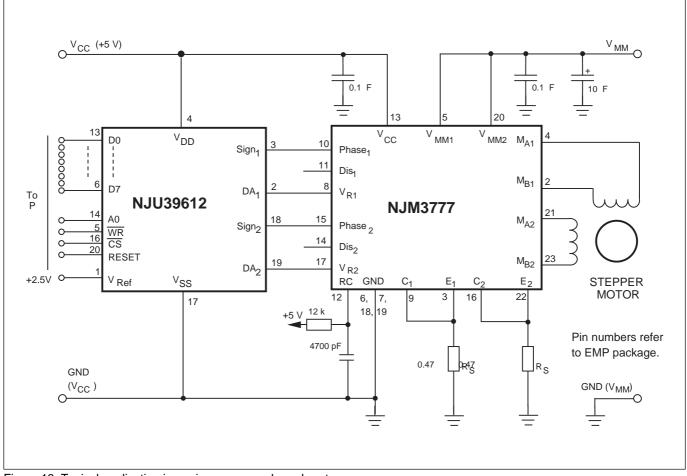

With a microprocessor, data is stored in ROM / RAM area or each step is successively calculated. NJU39612 is connected like any peripheral addressable device. All parts of stepping can be tailored for specific damping needs etc. This is the ideal solution for a system where there is an available microprocessor with extra capacity and low cost is more essential than simplicity. See typical application, figure 13.

### User Hints

Never disconnect ICs or PC Boards when power is supplied.

Select a motor that is rated for the current you need to establish desired torque. A high supply voltage will gain better stepping performance even if the motor is not rated for the  $V_{MM}$  voltage, the current regulation in the drivers from New JRC will take care of it. A normal stepper motor might give satisfactory result, but while microstepping, a "microstepping-adapted" motor is recommended. This type of motor has smoother motion due to two major differences, the stator / rotor teeth relationship is non-equal and the static torque is lower.

The NJU39612 can handle programs which generate microsteps at a desired resolution as well as quarter stepping, half stepping, full stepping, and wave drive.

### Ramping

Every drive system has inertia which must be considered in the drive system. The rotor and load inertia play a big role at higher speeds. Unlike the DC motor, the stepper motor is a synchronous motor and does not change its speed due to load variations. Examining a typical stepper motor's torque-versus-speed curve indicates a sharp torque drop-off for the "start-stop without error" curve. The reason for this is that the torque requirements increase by the cube of the speed change. For good motor performance, controlled acceleration and deceleration should be considered even though microstepping will improve overall performance.

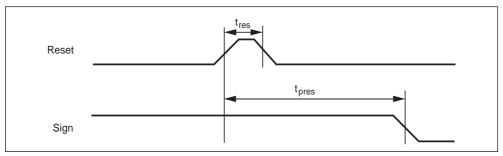

Figure 10. Double pulse programming, in- and output signals.

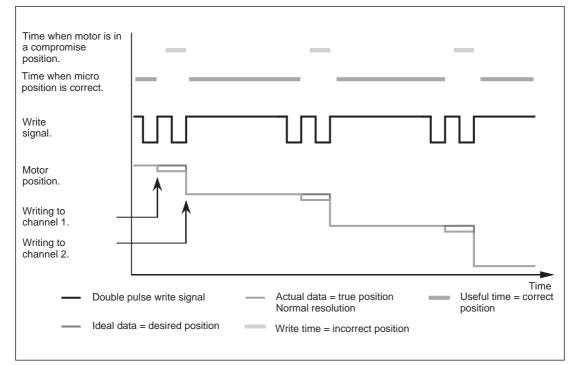

Figure 11. Single pulse programming, in- and output signals.

# Programming NJU39612

There are basically two different ways of programming the NJU39612. They are called "single-pulse programming" and "double-pulse programming." Writing to the device can only be accomplished by addressing one register at a time. When taking one step, at least two registers are normally updated. Accordingly there must be a certain time delay between writing to the first and the second register. This programming necessity gives some special stepping advantages.

# **Double-pulse Programming**

The normal way is to send two write pulses to the device, with the correct addressing in between, keeping the delay between the pulses as short as possible. Write signals will look as illustrated in figure10. The advantages are:

- low torque ripple

- correct step angles between each set of double pulses

- short compromise position between the two step pulses

- normal microstep resolution

# Single-pulse Programming

A different approach is to send one pulse at a time with an equally-spaced duty cycle. This can easily be accomplished and any two adjacent data will make up a microstep position. Write signals will look as in figure 11. The advantages are:

- higher microstep resolution

- smoother motion

The disadvantages are:

- higher torque ripple

- · compromise positions with almost-correct step angles

Figure 12. Typical blockdiagram of an application without a microprocessor.

Figure 13. Typical application in a microprocessor based system.

The specifications on this databook are only given for information, without any guarantee as regards either mistakes or omissions. The application circuits in this databook are described only to show representative usages of the product and not intended for the guarantee or permission of any right including the industrial rights.