# PRELIMINARY

# **4-BIT SINGLE CHIP MICRO CONTROLLER**

# GENERAL DESCRIPTION

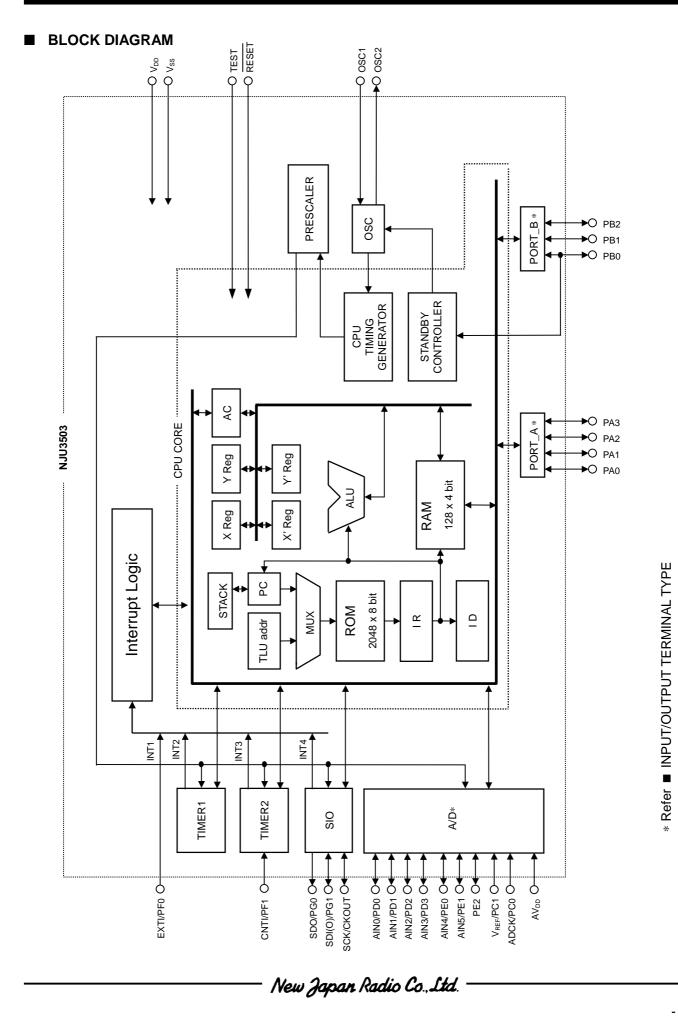

The **NJU3503** is the C-MOS 4-bit Single Chip Micro Controller consisting of the 4-bit CPU Core, Input / Output Selectable I/O ports, Program ROM, Data RAM, Dual Timer/Counter, 8-bit Serial Interface, 8-bit A/D Converter, and Oscillator Circuit (CR or Ceramic or X'tal). It realizes the control for home appliances or toys by only few external components.

The **NJU3503** is suitable for battery operated appliances because of low operating current, wide operating voltage range, and STANDBY function (HALT mode).

# FEATURES

#### 2048 X 8 bits Internal Program ROM 128 X 4 bits Internal Data RAM Input / Output Port 20 lines(MAX) / NJU3503L 20 lines(MAX) / NJU3503M 12 lines ... Input / Output direction of each bit is selected by the mask option. 8 lines ... Input / Output direction of each bit can be changed by the program. Additional functions by the mask option. **External Interrupt Terminal** : EXTI/PF0 External Clock Input Terminal for Timer2 : CNTI/PF1 Serial Interface Terminals : SDO/PL0, SDI(O)/PG1 A/D Converter Interface Terminals : ADCK/PC0, V<sub>RFF</sub>/PC1, AIN0-3/PD0-3, AIN4-5/PE0-1 High Output-Current terminal (11 lines) : PA0-PA3, PD0-PD3, PE0-PE2 N-Channel FET Open Drain Type (I<sub>OL</sub>) 15mA at V<sub>DD</sub>=5V Instruction Set 59 instructions Subroutine Nesting 8 levels Pulse Edge Detector The rising or falling edge of a pulse is selected by the mask option. Instruction Executing Time 6/fosc sec (1.5µsec at 4MHz) **Operating Frequency Range** 30kHz – 4MHz Internal Oscillator CR, or Ceramic, or X'tal oscillation and External clock input STANDBY function (HALT mode) Wide operating voltage range 2.4V - 5.5V 8-bit Serial Input / Output port Timer/Counter (Timer1 : 8-bit re-load type timer, Timer2 : 8-bit re-load type timer event counter) (Count clock : Timer1's clock is an internal one. Timer2's clock is an internal or external one.) 8-bit A/D converter (Multiplexed 6-channel input) 4 (external, timer1, timer2, serial Input / Output) Interrupt factor C-MOS technology Package outline SDIP28 / SDMP30

PACKAGE OUTLINE

NJU3503L

NJU3503M

11/May/2001

New Japan Radio Co., Ltd.

# NJU3503

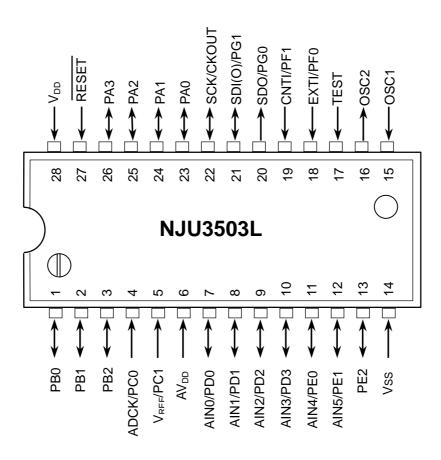

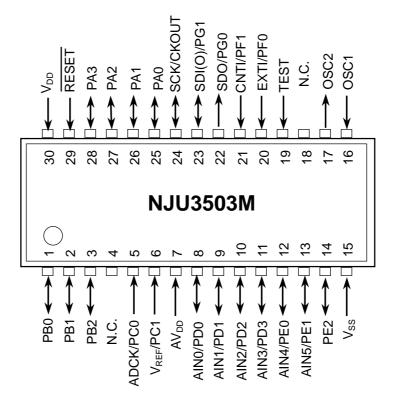

# PIN CONFIGURATION

SDIP28

SDMP30

New Japan Radio Co., Ltd.

# NJU3503

# ■ TERMINAL DESCRIPTION 1

| No.    |       |                          |                   |                                                                                                           |

|--------|-------|--------------------------|-------------------|-----------------------------------------------------------------------------------------------------------|

| NJU    | NJU   | SYMBOLS                  | INPUT/OUTPUT      | FUNCTIONS                                                                                                 |

| 3503M  | 3503L |                          |                   |                                                                                                           |

| 1      | 1     | PB0                      | INPUT/OUTPUT      |                                                                                                           |

| 2      | 2     | PB1                      | INPUT/OUTPUT      | Selects a terminal circuit for each port from the following                                               |

| 3      | 3     | PB2                      | INPUT/OUTPUT      | by the mask option.                                                                                       |

|        |       |                          |                   | •C-MOS Schmitt Trigger Input Terminal with Pull-up                                                        |

|        |       |                          |                   | Resistance (ISP)<br>•C-MOS Schmitt Trigger Input Terminal (IS)                                            |

|        |       |                          |                   | •C-MOS Output Terminal (OC)                                                                               |

|        |       |                          |                   | When the ports are selected as the input terminal, PB0                                                    |

|        |       |                          |                   | operates also as RESTART signal input terminal to return                                                  |

|        |       |                          |                   | from STANDBY mode, and PB1 operates also as the Edge                                                      |

|        |       |                          |                   | Detector Terminal.                                                                                        |

| 5      | 4     | ADCK / PC0               | INPUT             | 2-bit Input PORTC.                                                                                        |

| 6      | 5     | V <sub>REF</sub> / PC1   | INPUT             | Selects a function of either of 1) or 2) for PORTC by the                                                 |

|        |       |                          |                   | mask option.                                                                                              |

|        |       |                          |                   | 1) Input terminal for A/D Converter.                                                                      |

|        |       |                          |                   | External Clock Input Terminal : ADCK (ACP,AC)<br>Reference Voltage Input Terminal : V <sub>REF</sub> (AD) |

|        |       |                          |                   | Reference voltage input ferminal v <sub>REF</sub> (AD)                                                    |

|        |       |                          |                   | 2) 2-bit Input Terminals as PORTC.                                                                        |

|        |       |                          |                   | Selects a terminal circuit for each port from the following                                               |

|        |       |                          |                   | by the mask option.                                                                                       |

|        |       |                          |                   | <ul> <li>C-MOS Schmitt Trigger Input Terminal with Pull-up</li> </ul>                                     |

|        |       |                          |                   | Resistance (ISP)                                                                                          |

|        |       | A) (                     |                   | •C-MOS Schmitt Trigger Input Terminal (IS)                                                                |

| 7      | 6     | AV <sub>DD</sub>         | -                 | Analog Block Power source                                                                                 |

| 8      | 7     | AIN0 / PD0               | AIN0 – AIN3:      | Connect to V <sub>DD</sub> terminal when A/D converter is not used.<br>4-bit Input PORTD.                 |

| 9      | 8     | AIN0 / PD0<br>AIN1 / PD1 | INPUT             |                                                                                                           |

| 10     | 9     | AIN2 / PD2               |                   | mask option.                                                                                              |

| 11     | 10    | AIN3 / PD3               | PD0 – PD3:        | 1) 4-bit Analog Input to A/D Converter. (AD)                                                              |

|        |       |                          | INPUT/OUTPUT      |                                                                                                           |

|        |       |                          |                   | 2) 4-bit Input / Output Terminals as PORTD.                                                               |

|        |       |                          |                   | Selects a terminal circuit for each port from the following                                               |

|        |       |                          |                   | <ul> <li>by the mask option.</li> <li>C-MOS Input Terminal with Pull-up Resistance (ICP)</li> </ul>       |

|        |       |                          |                   | •C-MOS Input Terminal (IC)                                                                                |

|        |       |                          |                   | •Nch-FET Open-Drain Output Terminal with Pull-up                                                          |

|        |       |                          |                   | Resistance (ONP)                                                                                          |

|        |       |                          |                   | •Nch-FET Open-Drain Output Terminal (ON)                                                                  |

| Note ) | )     | INPUT/OUTF               | PUT : Input or Ou | utput is selected by the mask option.                                                                     |

| ,      |       | INOUT                    |                   | utput is changed by the program.                                                                          |

|        |       |                          | -                 |                                                                                                           |

# ■ TERMINAL DESCRIPTION 2

| N              | 0.             |                                 |                                        |                                                                                                                                                                                                                                                                                                                                                                                       |

|----------------|----------------|---------------------------------|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NJU            | NJU            | SYMBOL                          | INPUT/OUTPUT                           | FUNCTIONS                                                                                                                                                                                                                                                                                                                                                                             |

| 3503M          | 3503L          |                                 |                                        | 2 hit Input / Output DODTE                                                                                                                                                                                                                                                                                                                                                            |

| 12<br>13<br>14 | 11<br>12<br>13 | AIN4 / PE0<br>AIN5 / PE1<br>PE2 | AIN4, AIN5:<br>INPUT<br>PE0 – PE2:     | <ul> <li>3-bit Input / Output PORTE.</li> <li>Selects a function of either of 1) or 2) for PORTE by the mask option.</li> <li>1) 2bit Analog Input to A/D Converter. : AIN4,AIN5 (AD)</li> </ul>                                                                                                                                                                                      |

|                |                |                                 | INPUT/OUTPUT                           | <ul> <li>2) 3-bit Input / Output Terminals as PORTE.<br/>Selects a terminal circuit for each port from the following<br/>by the mask option.</li> <li>C-MOS Input Terminal with Pull-up Resistance (ICP)</li> <li>C-MOS Input Terminal (IC)</li> <li>Nch-FET Open-Drain Output Terminal with Pull-up<br/>Resistance (ONP)</li> <li>Nch-FET Open-Drain Output Terminal (ON)</li> </ul> |

| 15             | 14             | V <sub>SS</sub>                 | —                                      | Power Source ( 0V )                                                                                                                                                                                                                                                                                                                                                                   |

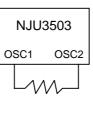

| 16<br>17       | 15<br>16       | OSC1<br>OSC2                    | INPUT<br>OUTPUT                        | Internal Oscillator Terminals.<br>Connects a device selected from the ceramic or the crystal<br>resonator, or the resistor, to these terminals for the internal<br>oscillator.<br>In the external clock operation, OSC1 is the external clock<br>input terminal and OSC2 is normally open terminal.                                                                                   |

| 19             | 17             | TEST                            | INPUT                                  | Maker Testing Terminal with Pull-down Resistance<br>The terminal is recommended to connect to GND.                                                                                                                                                                                                                                                                                    |

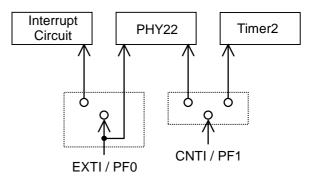

| 20<br>21       | 18<br>19       | EXTI / PF0<br>CNTI / PF1        | INPUT<br>INPUT                         | <ul> <li>2-bit Input PORTF.</li> <li>Selects a function of either of 1) or 2) for PORTF by the mask option.</li> <li>1) External Interrupt Input Terminal with Pull up resistance :EXTI (IIP,II)</li> <li>External Clock Input Terminal with Pull up resistance for Timer2 :CNTI (IIP,II)</li> </ul>                                                                                  |

|                |                |                                 |                                        | <ul> <li>2) 2-bit Input Terminals as PORTF.</li> <li>Selects a terminal circuit for each port from the following by the mask option.</li> <li>•C-MOS Schmitt Trigger Input Terminal with Pull-up Resistance (ISP)</li> <li>•C-MOS Schmitt Trigger Input Terminal (IS)</li> </ul>                                                                                                      |

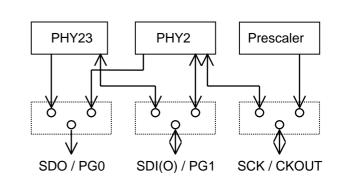

| 22             | 20             | SDO / PG0                       | SDO :OUTPUT<br>PG0 :OUTPUT             | 2-bit Input / Output PORTG.<br>Selects a function of either of 1) or 2) for PORTG by the mask option.                                                                                                                                                                                                                                                                                 |

| 23             | 21             | SDI(O)/ PG1                     | SDI(O) :INOUT<br>PG1 :<br>INPUT/OUTPUT | 1) Serial Interface Function<br>Serial Data Output Terminal : SDO (SO)<br>Serial Data Input-Output Terminal with Pull-up<br>Resistance : SDI(O) (SDP,SD)                                                                                                                                                                                                                              |

|                |                |                                 |                                        | <ul> <li>2) 2-bit Input / Output Terminals as PORTG.<br/>Selects a terminal circuit for each port from the following<br/>by the mask option.</li> <li>•C-MOS Input Terminal with Pull-up Resistance<br/>(ICP):PG1</li> <li>•C-MOS Input Terminal (IC) : PG1</li> <li>•C-MOS Output Terminal (OC) : PG0,PG1</li> </ul>                                                                 |

| Note)          |                | INPUT/OUTF<br>INOUT             |                                        | utput is selected by the mask option.<br>utput is changed by the program.                                                                                                                                                                                                                                                                                                             |

New Japan Radio Co.,Ltd. -

#### **TERMINAL DESCRIPTION 3**

| N     | 0.    |                 |                                 |                                                                                                                                                                                |

|-------|-------|-----------------|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NJU   | NJU   | SYMBOL          | INPUT/OUTPUT                    | FUNCTIONS                                                                                                                                                                      |

| 3503M | 3503L |                 |                                 |                                                                                                                                                                                |

| 24    | 22    | SCK/CKOUT       | SCK :INOUT<br>CKOUT :<br>OUTPUT | <ul> <li>Selects a function of either of 1) or 2) by the mask option.</li> <li>1) Serial Clock Input or Output Terminal with Pull-up<br/>Resistance. : SCK (SCP,SC)</li> </ul> |

|       |       |                 |                                 | <ul> <li>2) Clock Divided by Prescaler Output Terminal.</li> <li>Selects the dividing times of the clock in the prescaler by the mask option. : CKOUT</li> </ul>               |

| 25    | 23    | PA0             | INOUT                           | 4-bit Programmable Input / Output PORTA.                                                                                                                                       |

| 26    | 24    | PA1             | INOUT                           | These 4-bit terminals direction can be changed by the                                                                                                                          |

| 27    | 25    | PA2             | INOUT                           | program as each terminal of Input or Output.                                                                                                                                   |

| 28    | 26    | PA3             | INOUT                           | Use of Pull-up resistance for a terminal is in accordance with the mask option.(IOP,IO)                                                                                        |

|       |       |                 |                                 | •as Input : C-MOS Input Terminals                                                                                                                                              |

|       |       |                 |                                 | <ul> <li>as Output: Nch-FET Open-Drain Output Terminals</li> </ul>                                                                                                             |

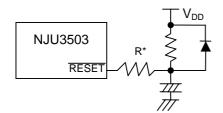

| 29    | 27    | RESET           | INPUT                           | RESET Terminal.<br>When the low level input-signal, the system is initialized.                                                                                                 |

| 30    | 28    | V <sub>DD</sub> | _                               | Power Source (2.4V – 5.5V)                                                                                                                                                     |

Note)

INPUT/OUTPUT : Input or Output is selected by the mask option.

INOUT : Input or Output is changed by the program. "ISP, IS, ICP, IC, IOP, IO, OC, ONP, ON, ACP, AC, AD, IIP, II, SO, SDP, SD, SCP, SC" are symbols using on MASK OPTION GENERATOR(MOG).

# ■ INTERNAL SYSTEM DESCRIPTION

The **NJU3503** is a C-MOS 4-Bit Single Chip Micro Controller consisted of Original CPU Core, Selectable Input-Output(I/O) Ports(MAX. 20 lines), Program ROM(2048 bytes), Data RAM(128 nibbles), 8-Bit A/D Converter, 8-bit Serial Interface, Dual 8-Bit Timer/Counter, Interrupt Control Circuit and Oscillator Circuit.

The CPU block in the **NJU3503** is consisted of ALU(Arithmetic Logic Unit) executing the binary adding, subtracting or logical calculating, AC(Accumulator), four Registers, STACK allowing the 8-level subroutinenesting or Interrupt operation, Program Counter indicating 2048 addresses sequentially, and Timing generator.

The **NJU3503** can be applied to the various markets because of the rich and efficient instruction set(59 instructions), wide operating voltage range(2.4V to 5.5V), low operating current, and STANDBY function reducing the power supply current.

# (1) INTERNAL REGISTER

# Accumulator(AC)

Accumulator(AC) is structured by the 4-bit register. It holds a data or a result of calculation, and executes the shift-operation (ROTATE) or the data transference between the other registers and Data Memory (RAM).

The accumulator condition is unknown on the "RESET" operation.

• X-register(X-reg)

X-register(X-reg) operates as the 4-bit register. X-reg operates also as the RAM address pointer with Y-register.

The X-reg condition is unknown on the "RESET" operation.

Y-register(Y-reg)

Y-register(Y-reg) operates as the 4-bit register or the RAM address pointer with X-reg. The Y-reg condition is unknown on the "RESET" operation.

X'-register(X'-reg)

X'-register(X'-reg) operates as the 4-bit register or a part of Program Memory(ROM) address pointer for looking data in the ROM(TRM instruction) up function.

The X'-reg condition is unknown on the "RESET" operation.

Y'-register(Y'-reg)

Y'-register(Y'-reg) operates as the 4-bit register or the peripheral register number(PHYn) pointer. The Y'-reg condition is unknown on the "RESET" operation.

# (2) INTERNAL FLAG

RPC flag(RPC)

RPC flag(RPC) changes the instruction table. Several instructions perform either of the dual tasks in accordance with the RPC flag condition. The RPC flag condition selects either of two couples of registers which are X- and Y- reg, or X'- and Y'-reg. X- or Y- reg is selected when the RPC flag condition is "0"(RPC=0). X'- or Y'- reg is selected when the RPC flag condition is "1"(RPC=1). The RPC flag condition is set to "1"(RPC=1) by SRPC instruction, and is set to "0"(RPC=0) by RRPC instruction. The RPC flag condition is set to "0" on the "RESET" operation.

CARRY flag(CY)

When the carry occurs after the adding calculation, the CARRY flag(CY) condition is set to "1"(CY=1), and when no carry, the CY flag condition is set to "0"(CY=0). When the borrow occurs after the subtracting calculation, the CY flag condition is set to "0"(CY=0), and when no borrow, the CY flag condition is set to "1"(CY=1). The bit-operation instruction operates the bit data rotation on the CY flag combined with the accumulator or the other register.

The CY flag condition is set to "1"(CY=1) by SEC instruction and is set to "0"(CY=0) by CLC instruction. The CY flag condition is kept until the end of the next instruction executing cycle. The CY flag condition is unknown on the "RESET" operation.

New Japan Radio Co., Ltd.

# • STATUS flag(ST)

STATUS flag(ST) is the conditional flag in accordance with the result of the instruction execution. Its condition is in accordance with follows:

- 1) to be same as CY flag condition.

- 2) to be set the condition to "0"(ST=0) when the result of the logical calculation(AND, OR, XOR, YNEA) is zero.

3) to be set the condition to "0"(ST=0) when the result of the comparison(CMP) is zero.

However, ST flag condition is always set to "1"(ST=1) except above three.

ST flag controls the branch operation. Branch instruction does not branch when ST flag condition is "0", and branches when ST flag condition is "1". ST flag condition is kept until the end of the next instruction executing cycle.

The ST flag condition is unknown on the "RESET" operation.

- (3) FUNCTIONAL BLOCK

- ARITHMETIC LOGIC UNIT(ALU)

ARITHMETIC LOGIC UNIT(ALU) is a 4-bit binary paralleled calculation circuit operating binary addition, binary subtraction, comparison, logical AND, logical OR, exclusive OR, and SHIFT(Rotation). And it also can detect CARRY, BORROW or ZERO in accordance with the result of each calculation.

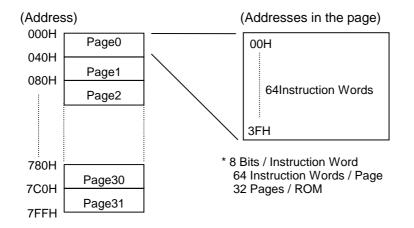

PROGRAM MEMORY(ROM)

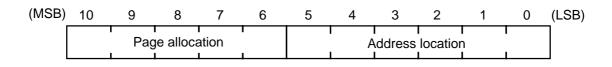

PROGRAM MEMORY(ROM) consists of 32 pages, and a page consists of 64 bytes memory capacity. Therefore the **NJU3503** prepares the 2048-byte ROM for the application program. The ROM address is indicated by the Program Counter(PC).

# [PROGRAM MEMORY AREA]

# PROGRAM COUNTER(PC)

PROGRAM COUNTER(PC) consisted of the 10-bit binary counter stores the address for the next operating instruction in ROM. Data figures limited from b0 to b5 on the PC indicate the address in a page, and data figures limited from b6 to b10 on the PC indicate the page in a bank. Although the ROM address can be indicated 2048 addresses continuously, the target address of JMP instruction is restricted by Paging structure in ROM. The target address of JPL or CALL instruction is restricted by Banking structure in ROM.

The PC condition is set to "0" on the "RESET" operation.

JMP instruction can branch to the optional address in the page. The target address is indicated by the data figures limited from b0 to b5 (6bits) on PC as shown in above. The paging structure can reduce the program size in ROM and the JMP instruction execution time against JPL instruction because JMP instruction is consisted of one byte (8bits) length. JPL and CALL instructions can branch to the optional address without considering the paging structure, because they consist of two bytes (16bits) length including the 11 bits of PC.

# • STACK

STACK consists of three types of registers which are the 8 by 11 bits, the 5 by 4 bits, and the 2 by 1 bit registers. The registers of STACK hold the data of PC automatically when the interrupt routine or the subroutine is called. The 5 by 4 bits registers of STACK hold the data of the internal registers automatically when the interrupt operation is executed. The 2 by 1 bit registers of STACK hold the data of the internal registers of the internal flag automatically when the interrupt operation is executed. In the return (RET or RETI) operation, PC, the internal registers, and the internal flags registers get the held data from STACK automatically.

# [For branch(CALL) and interrupt operation ] [For interrupt operation ]

# STACK POINTER(SP)

STACK POINTER(SP) consists of the 3 bits binary counter. SP indicates the number of next operating position in the STACK. It counts one up(increment) after the subroutine call(CALL) or the interrupt operation, and it counts one down(decrement) after the return(RET or RETI) operation.

Data storing operation to STACK after that SP overflowed (over than 7) or under flowed(under than 0), breaks the former held data in STACK. Therefore the subroutine nesting level must be cautioned in the application program.

SP condition is set to "0" on "RESET" operation.

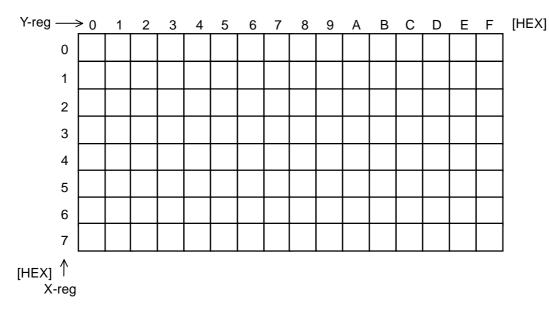

# DATA MEMORY(RAM)

DATA MEMORY(RAM) is formed with the 4-bit length a word. The **NJU3503** prepares 128 words(512 bits) RAM. The data formed with the 4-bit length a word can be read/written from/to RAM, and the data formed with the 1-bit length in a word can be set, reset, or tested by the bit-operation instruction.

The RAM address is indicated indirectly by X-reg and Y-reg. The lower 3 bits(b0,b1,b2) in X-reg are used as the RAM address pointer and higher a bit (b3) is not used.

# [RAM ADDRESS MAP]

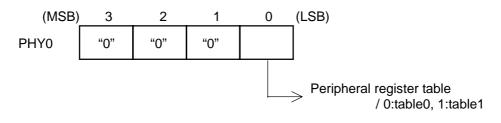

# PERIPHERAL REGISTERs(PH)

PERIPHERAL REGISTERs(PH) controlling I/O Ports or the ROM address are selected by the data in Y'reg.

Two Peripheral Register tables called as table0 and table1 in the NJU3503 consist of 32 registers totally. The Peripheral Register assigned for each I/O Port can get the signal data from the external application by reading operation, or can output the signal data to the external application by writing operation in accordance with the type of input or output selected by the mask option. Although the data can be read from the Peripheral Register assigned as the Output, it sometimes takes the incorrect data of the Output Port.

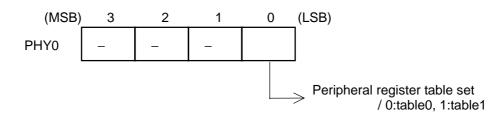

# <<Peripheral Register Table Change>>

When LSB(b0) of the peripheral register table change register(PHY0) is written "0", the table0 is selected. When LSB of PHY0 is written "1", the table1 is selected. The table0 is selected on "RESET" operation.

# [Reading from the Peripheral Register Table Change Register (PHY0)]

# [Writing to the Peripheral Register Table Change Register (PHY0)]

| Y'-register | Register No. | Peripheral Register Name                 |   | Write or<br>Read *1 |      | a in<br>set |

|-------------|--------------|------------------------------------------|---|---------------------|------|-------------|

| 0H          | PHY0         | Table Change Register                    | 1 | WR                  | 0    |             |

| 1H          | PHY1         | Serial Input/Output Control Register     | 3 | WR                  | 0    | *2          |

| 2H          | PHY2         | Serial Input/Output Shift Register       | 8 | WR                  | 0    | *2          |

| 3H          | PHY3         | Timer1/Prescaler Control Register        | 3 | WR                  | 0    |             |

| 4H          | PHY4         | Initial Value Register1 / Timer Counter1 | 8 | WR                  | 0    |             |

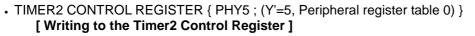

| 5H          | PHY5         | Timer2 Control Register                  | 4 | WR                  | 0    | *5          |

| 6H          | PHY6         | Initial Value Register2 / Timer Counter2 | 8 | WR                  | 0    |             |

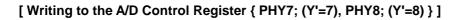

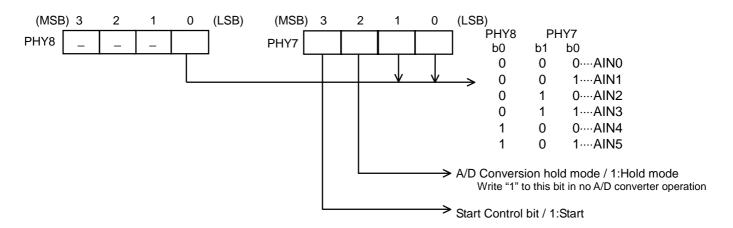

| 7H          | PHY7         | A/D Convertor Control Register           | 4 | WR                  | 0    | *3          |

| 8H          | PHY8         | A/D Convertor Control Register           | 1 | WR                  | 0    | *3          |

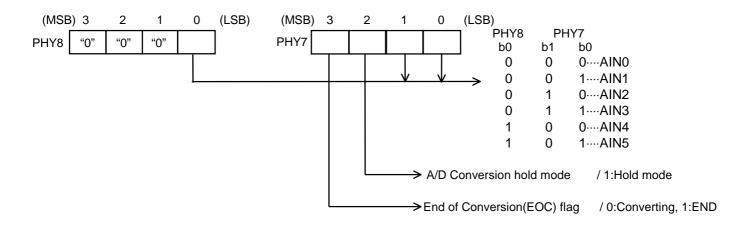

| 9H          | PHY9         | A/D Convertor Output Register            | 8 | R                   | 0    |             |

| AH          | PHY10        | Interrupt Control Register               | 4 | WR                  | 0    | *5          |

| BH          | PHY11        |                                          |   |                     |      |             |

| СН          | PHY12        |                                          |   |                     |      |             |

| DH          | PHY13        | ROM Addressing Register                  | 3 | WR                  | unkn | own         |

| EH          | PHY14        |                                          |   |                     |      |             |

| FH          | PHY15        |                                          |   |                     |      |             |

# [PERIPHERAL REGISTER TABLE0]

# [PERIPHERAL REGISTER TABLE1]

| Y'-register | Register No. | Peripheral Register Name                        |   | Write or<br>Read *1 | Data in<br>Reset |

|-------------|--------------|-------------------------------------------------|---|---------------------|------------------|

| 0H          | PHY0         | Table Change Register                           | 1 | WR                  | 0                |

| 1H          | PHY17        | PORTA Output or PORTA Input                     | 4 | WR                  | 0                |

| 2H          | PHY18        | PORTB Output or PORTB Input                     | 3 | W/R                 | 0                |

| ЗH          | PHY19        | PORTC Input                                     | 2 | R                   | 0 *4             |

| 4H          | PHY20        | PORTD Output or PORTD Input                     | 4 | W/R                 | 0 *3             |

| 5H          | PHY21        | PORTE Output or PORTE Input                     | 3 | W/R                 | 0 *3             |

| 6H          | PHY22        | PORTF Input                                     | 2 | R                   | 0 *5             |

| 7H          | PHY23        | PORTG Output or PORTG Input                     | 2 | W/R                 | 0 *2             |

| 8H          | PHY24        | Programmable Input/Output Port Control Register | 4 | WR                  | 0                |

| 9H          | PHY25        |                                                 |   |                     |                  |

| AH          | PHY26        |                                                 |   |                     |                  |

| BH          | PHY27        |                                                 |   |                     |                  |

| СН          | PHY28        |                                                 |   |                     |                  |

| DH          | PHY29        |                                                 |   |                     |                  |

| EH          | PHY30        |                                                 |   |                     |                  |

| FH          | PHY31        |                                                 |   |                     |                  |

\*1 W

: Write only : Read only R : Read and Write WR

: Fixed as Read or Write by the mask option W/R

# NJU3503

\*2 Wiring of terminals The mask option selects a terminal type from SDO/PG0, SDI(O)/PG1 or SCK/CKOUT as shown in right.

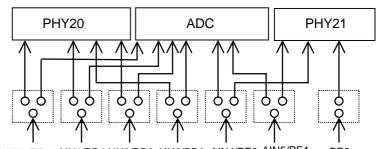

\*3 Wiring of terminals The mask option selects a terminal type from AIN0/PD0, AIN1/PD1, AIN2/PD2, AIN3/PD3, AIN4/PE0, AIN5/PE1, PE2 as shown in right.

AIN0/PD0 AIN1/PD1AIN2/PD2 AIN3/PD3 AIN4/PE0 AIN5/PE1 PE2

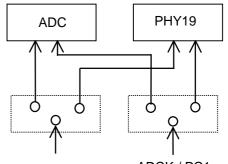

Wiring of terminals \*4 The mask option selects a terminal type from V<sub>REF</sub>/PJ0, or ADCK/PJ1 as shown in right.

V<sub>REF</sub> / PC0

\*5 Wiring of terminals The mask option selects a terminal type from EXTI/PF0, or CNTI/PF1 as shown in right.

ROM ADDRESSING REGISTER(PHY13)

ROM ADDRESSING REGISTER (PHY13) indicates the address of ROM with Accumulator and X'-reg for the data transference operation (TRM) from ROM to RAM.

The PHY13 condition are unknown on "RESET" operation. The lower 3 bits(b0,b1,b2) in PHY13 are used as the ROM ADDRESSING and higher a bit(b3) is not used,

# [ROM ADDRESSING ]

| no used | A10 | A9 | A8 | A7 | A6 | A5 | A4 | A3 | A2 | A1 | A0 |

|---------|-----|----|----|----|----|----|----|----|----|----|----|

| b3      | b2  | b1 | b0 | b3 | b2 | b1 | b0 | b3 | b2 | b1 | b0 |

| PHY13   |     |    |    | Х  | ,  |    |    | AC | 2  |    |    |

# INPUT OUTPUT PORT

The **NJU3503** prepares 8 Input-Output lines and 12 dual-function lines for the interface to an external application circuit. All lines are assigned to each Peripheral Register.

Data reading operation from the peripheral register can input the actual signals through the input terminal. Data writing operation to the peripheral register can output the actual signals through the output terminal.

|                | N TABLE ]                             |                                                     |

|----------------|---------------------------------------|-----------------------------------------------------|

| PORT NAME      | FUNCTION                              | INPUT/OUTPUT                                        |

| PORTA          | Input / Output port                   | Programmable Input / Output PORT(4-bit).            |

| PORTB          | Input / Output port                   | Input / Output selectable ports by the mask option. |

| PORTC(PC0)     | Input port or ADCK                    | Input                                               |

| PORTC(PC1)     | Input or V <sub>REF</sub>             | Input                                               |

| PORTD          | Input / Output port or<br>AIN0 – AIN3 | Input / Output selectable ports by the mask option  |

| PORTE(PE0,PE1) | Input / Output port or<br>AIN4 – AIN5 | Input / Output selectable ports by the mask option. |

| PORTE(PE2)     | Input / Output port                   | Input / Output selectable ports by the mask option. |

| PORTF(PF0)     | Input port or EXTI                    | Input                                               |

| PORTF(PF1)     | Input port or CNTI                    | Input                                               |

| PORTG(PG0)     | Output Port or SDO                    | output                                              |

| PORTG(PG1)     | Input / Output port or<br>SDI(O)      | Input / Output selectable ports by the mask option. |

[ PORT FUNCTION TABLE ]

Note1) Pull-up resistance is selected by the mask option.(refer ■INPUT OUTPUT TERMINAL TYPE)

(1) INPUT OUTPUT PORT

• PORTA(PA0 - PA3)

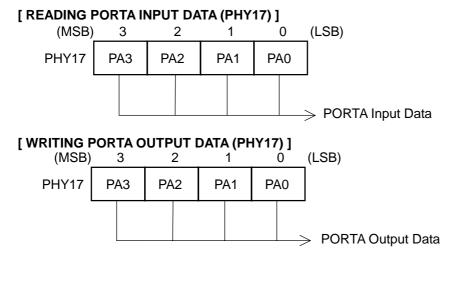

PORTA is a 4-bit programmable input-output PORT. The input or the output is selected for each bit by the programmable input/output control register (PHY24). It is set to "1" as the output, and is set to "0" as the input. When the PORT is set as the output, the 4-bit signals are output through the output terminals by writing data into the peripheral register assigned for PORTA (PHY17). PHY17 as the output register should be written the output data before the PORTA is set as the output by PHY24, because the conditions of the output terminals are unknown while the output data is not written in PHY17. When this PORT is set as the input, the 4-bit external signals are gotten directly through the input terminals by reading data from PHY17. PHY17 can be written or read independent of the state of PHY24 as the input or output.

Though the output circuit is Nch open drain type, the C-MOS input buffer is connected to the same terminal. Therefore, the operating current of the chip by the short circuit current when the middle level voltage between  $V_{DD}$  and  $V_{SS}$  is input to this terminal.

PORTA is set as the input in accordance with the state of PHY24 set to "0" on the "RESET" operation.

# • PORTB(PB0 – PB2)

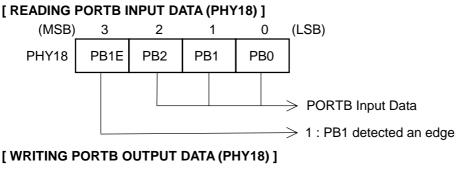

PORTB is a 3-bit input-output PORT. The input or the output is selected for each bit by the mask option. When the port is set as the output, the signal is output through the output terminal by writing data to the PORTB register (PHY18). When the port is set as the input, the external signal is gotten directly through the input terminal by reading data from PHY18.

When this PORTB is set as the input, these two ports perform the extra functions as follows:

# a. PB0 TERMINAL

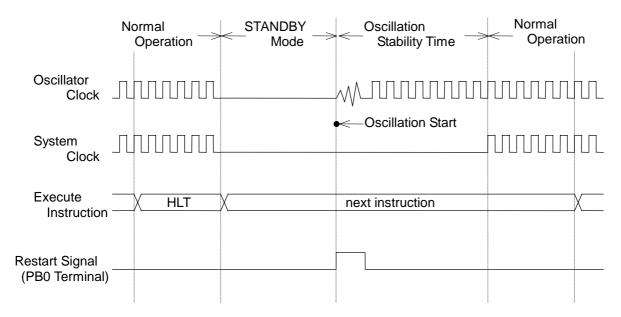

PB0 terminal performs the extra function as the restart signal input terminal to return from the "STANDBY" mode. When the rising edge of the signal from the external circuit is input into the PB0 terminal in mode of "STANDBY", the "STANDBY" mode is released and the CPU starts the execution again from the suspended address of the program. (refer **S**TANDBY FUNCTION)

# b. PB1 TERMINAL

PB1 terminal performs the extra function as the edge detector terminal. When the PB1 terminal detects the edge of the signal from the external circuit, the forth bit(b3) condition of PHY18 is set to "1". The "b3" of PHY18 is set to "1" even when the edge is input during the "STANDBY" mode. The condition of "b3" is kept until the writing operation to PHY18.

The polarity as low to high or high to low of the input signal edge can be selected by the mask option.

# • PORTC(PC0, PC1)

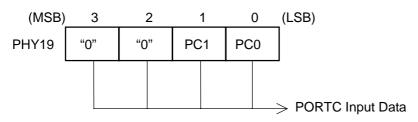

PORTC is a 2-bit input PORT. It operates also as  $V_{REF}$  and ADCK terminals of the internal A/D converter by the mask option. When the PORTC is set as the input PORT, the two external signals are gotten directly through the input terminals by reading data from PHY19.

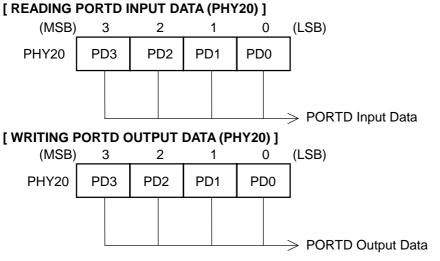

# [READING PORTD INPUT DATA (PHY20)]

# • PORTD(PD0 – PD3)

PORTD is a 4-bit input-output PORT. It operates also as the multiplexed 4-bit analog signal input terminals (AIN0 to AIN3) to the internal A/D converter by the mask option. The input or the output is selected for each bit by the mask option. When the PORT is set as the output, the 4-bit signals are output through the output terminals by writing data into the peripheral register assigned for PORTD (PHY20). PHY20 as the output register should be written the output data, because the conditions of the output terminals are unknown while the output data is not written in PHY20. When this PORT is set as the input, the 4-bit external signals are gotten directly through the input terminals by reading data from PHY20.

Though the output circuit is Nch open drain type, the C-MOS input buffer is connected to the same terminal. Therefore, the operating current of the chip by the short circuit current when the middle level voltage between  $V_{DD}$  and  $V_{SS}$  is input to this terminal.

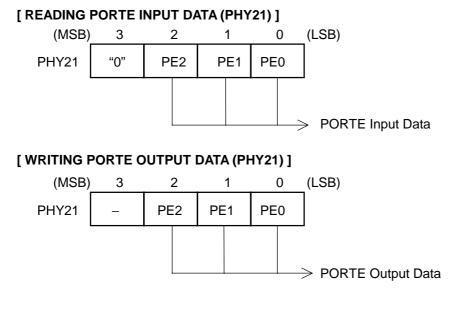

# PORTE(PE0 – PE2)

PORTE is a 3-bit input-output PORT. It operates also as the multiplexed 2-channel analog signal input terminals (AIN4 to AIN5) to the internal A/D converter by the mask option. The input or the output is selected for each bit by the mask option. When the PORT is set as the output, the 3-bit signals are output through the output terminals by writing data into the peripheral register assigned for PORTD (PHY21). PHY21 as the output register should be written the output data, because the conditions of the output terminals are unknown while the output data is not written in PHY21. When this PORT is set as the input, the 3-bit external signals are gotten directly through the input terminals by reading data from PHY21.

Though the output circuit is Nch open drain type, the C-MOS input buffer is connected to the same terminal. Therefore, the operating current of the chip by the short circuit current when the middle level voltage between  $V_{DD}$  and  $V_{SS}$  is input to this terminal.

New Japan Radio Co., Ltd.

- 16 -

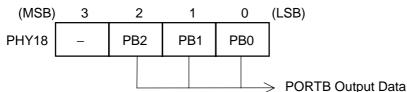

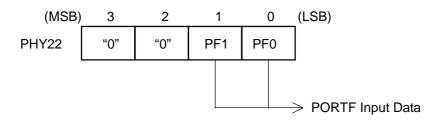

• PORTF(PF0 – PF1)

PORTF is a 2-bit input PORT. It operates also as EXTI input terminal for the external interrupt input and CNTI terminal for the event counter external clock input by the mask option. When the PORTF is set as the input PORT, the two external signals are gotten directly from the input terminals by reading data from PHY22.

# [ READING PORTF INPUT DATA (PHY22) ]

# • PORTG(PG0, PG1)

PORTG is a 2-bit input-output PORT. It operates also as SDO and SDI(O) terminals for the 8-bit serial interface by the mask option. When the PORTG is selected as the input-output PORT, PGO is fixed as the output and PG1 can be selected as the input or the output by the mask option. When the PORTG is selected as the output, the two signals are output through the output terminals to the external circuit by writing data to the PORTG register(PHY23). When PL1 is selected as the input, the external signal is gotten directly through the input terminal by reading data from PHY23.

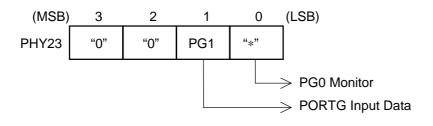

# [READING PORTG INPUT DATA (PHY23)]

When PG0 is output, its output condition can be monitored.

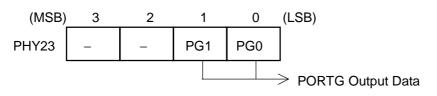

# [WRITING PORTG OUTPUT DATA (PHY23)]

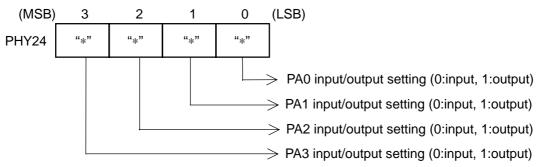

# • PROGRAMMABLE INPUT/OUTPUT PORT CONTROL REGISTER(PHY24)

Programmable Input / Output Port Control Register(PHY24) is a peripheral register to set the programmable input / output PORTA. The input or the output is selected for each bit by the mask option. It is set to "1" as the output, and is set to "0" as the input.

PORTA are set as the input in accordance with the state of PHY24 which is set to "0" on the "RESET" operation.

#### (MSB) 3 2 1 0 (LSB) "\*" "\*" "\*" PHY24 "\*" > PA0 input/output state(0:input, 1:output) $\rightarrow$ PA1 input/output state(0:input, 1:output) $\rightarrow$ PA2 input/output state(0:input, 1:output) $\rightarrow$ PA3 input/output state(0:input, 1:output)

# [WRITING Programmable Input / Output Port Control Register(PHY24)]

[READING Programmable Input / Output Port Control Register(PHY24)]

# (2) PROGRAMMABLE INPUT/OUTPUT PORT OPERATION

a. The output operation example

PA0 and PA1 of PORTA output "H", and PA2 and PA3 of PORTA output "L".

| SRPC<br>LDI<br>LDI<br>TAP | Y,0<br>A,%0001 | Peripheral table is set as the table1                                     |                   |

|---------------------------|----------------|---------------------------------------------------------------------------|-------------------|

| LDI                       | Y,1            | ;PHY17 is pointed                                                         |                   |

| LDI                       | A,%0011        | ;"0011" is stored into Accumulator                                        |                   |

| TAP                       |                | ;Data in Accumulator is transmitted to PHY17<br>; (PORTA output register) |                   |

| LDI                       | Y,8            | ;PHY24 is pointed                                                         |                   |

| LDI                       | A,%1111        | ;"1111" is stored into Accumulator                                        | set as the output |

| TAP                       |                | ;Data in Accumulator is transmitted to PHY24                              |                   |

|                           | :              |                                                                           |                   |

# b. The input operation example

Accumulator gets the input data from PORTA.

| SRPC<br>LDI<br>LDI<br>TAP       | Y,0<br>A,%0001        | Peripheral table is set as the table1                                                                                                                                            |                              |

|---------------------------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

| ldi<br>Ldi<br>Tap<br>Ldi<br>Tpa | Y,8<br>A,%0000<br>Y,1 | ;PHY24 is pointed<br>;"0000" is stored into Accumulator<br>;Data in Accumulator is transferred to PHY24<br>;PHY17 is pointed<br>;The input data from PHY17 is transferred to Acc | PORTA is<br>set as the input |

The signal from PA0 terminal is stored into the LSB of Accumulator, the signal from PA1 terminal is stored into the b1 of Accumulator, the signal from PA2 terminal is stored into the b2 of Accumulator, and the signal from PA3 terminal is stored into the b3 of Accumulator.

# ■ INPUT OUTPUT TERMINAL TYPE

Each terminal of PORTA, B, C, D, E, F, and G can select a terminal type from the follows by the mask option which is the same mask of the program coding into ROM and the others. But PORTC, and F select only the input terminal type. PG0 of PORTG select only the output terminal type.

|                                    | Types                                                             | With Pull-up | Without Pull-up | Terminals                                                                |  |  |

|------------------------------------|-------------------------------------------------------------------|--------------|-----------------|--------------------------------------------------------------------------|--|--|

| IINAL                              | C-MOS                                                             | Type ICP     | Type IC         | AIN0/PD0–<br>AIN3/PD3,<br>AIN4/PE0,<br>AIN5/PE1,<br>PE2,<br>SDI(O)/PG1   |  |  |

| INPUT TERMINAL                     | SCHMITT<br>TRIGGER                                                | Type ISP     | Type IS         | PB0–PB2,<br>ADCK/PC0,<br>V <sub>REF</sub> /PC1,<br>EXTI/PF0,<br>CNTI/PF1 |  |  |

| TERMINAL                           | C-MOS                                                             |              | Type OC         | PB0-PB2,<br>SDO/PG0,<br>SDI(O)/PG1                                       |  |  |

| Ουτρυτ Τ                           | N-channel<br>(Nch)<br>OPEN<br>DRAIN                               | Type ONP     | Type ON         | AIN0/PD0–<br>AIN3/PD3,<br>AIN4/PE0,<br>AIN5/PE2                          |  |  |

| PROGRAMMABLE INPUT OUTPUT TERMINAL | C-MOS<br>INPUT<br>/<br>N-channel<br>(Nch)<br>OPEN DRAIN<br>OUTPUT | Type IOP     | Type IO         | PA0-PA3                                                                  |  |  |

# TIMER

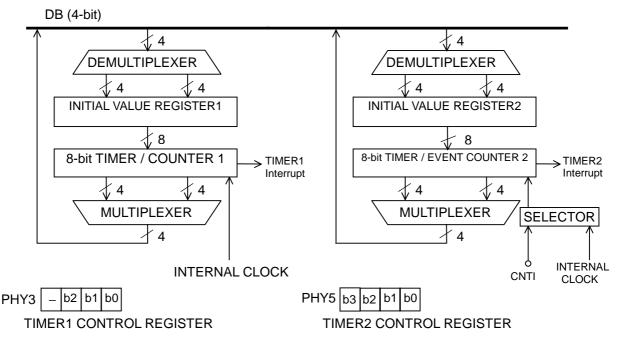

The **NJU3503** prepares a couple of Programmable Timer / Counter(Timer1,Timer2) consisted of the 8-bit binary counter.

# [Structure of Timer / Counter]

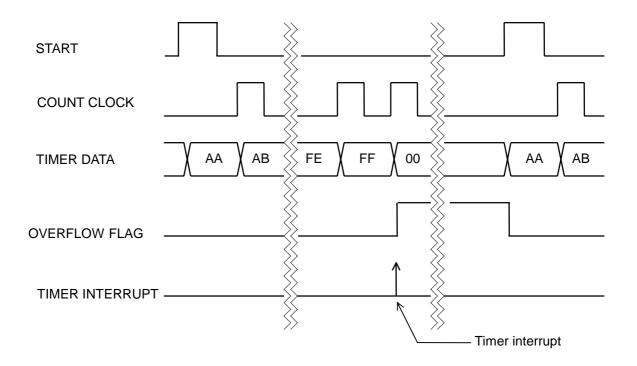

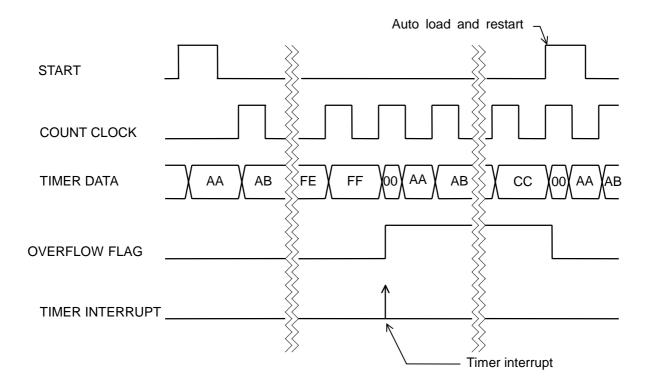

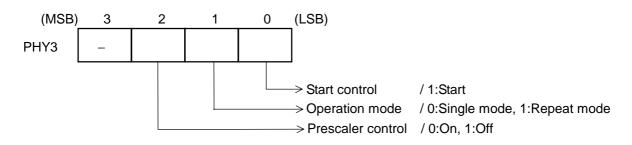

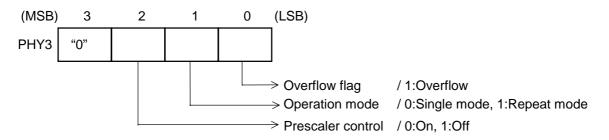

Timer1 counts only the internal clock and Timer2 counts either of the internal clock or the external clock in accordance with the condition of bit2(b2) of the Timer2 Control Register(PHY5). The initial value of the counter can be set the optional value by the program which instructs to write the data(a value of the time-interval or the event-count) into the Initial Value Register(Timer1 or Timer2 is set the each value independently). In enabling the timer interrupt, when the counter counts from "FF" to "00" (overflow), the timer interrupt request occurs and the internal interrupt process starts the own operation.

In the repeat mode of the Timer operation, when the counter overflows, the initial value is loaded into the counter automatically and the counter continues the count from the loaded initial value(Auto re-load function: See the repeat mode of the Timer operation timing chart). In the single mode of the Timer operation, when the counter overflows, the count is stopped(See the single mode of the Timer operation timing chart). For starting the count operation again, the start bit(LSB) of the Timer1 or Timer2 Control Register must be set to "1". The latest initial value is set into the counter and the counter starts the count.

In enabling the interrupt operation, when the counter overflows, the Timer / Counter overflow flag is set to "1" and the internal interrupt process starts to the own operation. In disabling the timer interrupt, the Timer / Counter overflow flag is not set. The Timer / Counter overflow flag is initialized by the Timer Start or the Reset signal.

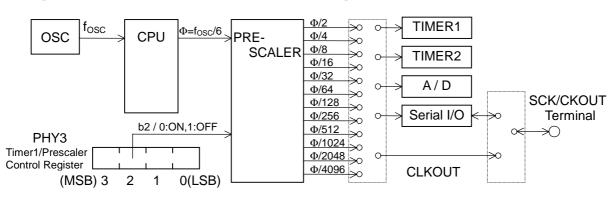

The internal clock into the counter is the divided clock from the internal prescaler. The frequency of the clock can be selected by the mask option from the following which are the dividing numbers based on the inverse of the 1-instruction executing  $period(1/f_{OSC} \times 6)$ .

# 1/2, 1/4, 1/8, 1/16, 1/32,1/64, 1/128, 1/256, 1/512, 1/1024, 1/2048,1/4096

When the bit2(b2) of the Timer1 / Prescaler Control Register is set to "1", the prescaler generating the internal count clock is stopped the operation. As the result, Timer / Counter stops the count operation.

In the external clock operation of Timer2, the external clock must be input to CNTI terminal. The Timer2 Control Register selects either the internal clock operation or the external clock operation.

New Japan Radio Co., Ltd.

[ THE SINGLE MODE OF THE TIMER OPERATION TIMING ] (The initial value is set to "AAh")

[THE REPEAT MODE OF THE TIMER OPERATION TIMING] (The initial value is set to "AAh")

# TIMER1 / PRESCALER CONTROL REGISTER { PHY3 ; (Y'=3, Peripheral register table 0) } [Writing to the Timer1 / Prescaler Control Register ]

EX.) An example of the start procedure in the single mode and the internal clock operation.

|      | :       |                                                  |       |                       |

|------|---------|--------------------------------------------------|-------|-----------------------|

| SRPC |         | ,                                                |       |                       |

| LDI  | Y,3     | ;PHY3(Timer1/Prescaler Control Register) is poir | nted. |                       |

| LDI  | A,%0000 | ;"0000"(BIN) is stored to accumulator            | ٦     | Single mode,          |

| TAP  |         | ;Data is transferred from accumulator to PHY3    | ļ     | Prescaler is enable   |

| LDI  | A,%0001 | ;"0001"(BIN) is stored to accumulator            | Ĩ     |                       |

| TAP  |         | ;Data is transferred from accumulator to PHY3    | J     | The count is started. |

|      | :       |                                                  | ,     |                       |

|      | :       |                                                  |       |                       |

Remarks) When the prescaler generating the internal count clock is stopped the operation, Timer is also stopped. But the data in the counter is kept. Therefore Timer can continue to count from the kept condition of the counter when the prescaler is started the operation again. However, the clocks from the prescaler are delivered to Serial I/O, CKOUT terminal and A/D converter controller, therefore the prescaler requires careful operation, especially stop or start.

When the prescaler is started the operation again after it was stopped, it is reset and start to count from "zero".

# [Reading from the Timer1 / Prescaler Control Register]

EX.) An example of the overflow in the single mode and the internal clock operation.(The data of the Timer1 / Prescaler Control Register is "0001"(BIN).)

| SRPC    | ;                                                    |

|---------|------------------------------------------------------|

| LDI Y,3 | ;PHY3(Timer1/Prescaler Control Register) is pointed. |

| TPA     | ;"0001"(BIN) of PHY3 is transferred to accumulator.  |

EX.) An example of the start procedure for the repeat mode, the external clock operation and releasing the count clock mask.

| SRPC |         | ;                                             |                       |

|------|---------|-----------------------------------------------|-----------------------|

| LDI  | Y,5     | ;PHY5(Timer2 Control Register) is pointed.    |                       |

| LDI  | A,%1110 | ;"1110"(BIN) is stored to accumulator         | Repeat mode, External |

| TAP  |         | ;Data is transferred from accumulator to PHY5 | clock operation.      |

| LDI  | A,%1111 | ;"1111"(BIN) is stored to accumulator         |                       |

| TAP  |         | ;Data is transferred from accumulator to PHY5 | The count is started. |

| :    |         |                                               |                       |

|      | :       |                                               |                       |

Remarks) In the Timer2 operation, when the count clock mask bit(b3) of the Timer2 Control Register is set to "0", the Timer2 is stopped to count and it holds the latest data of the 8-bit counter2. When the b3 is set to "1", the Timer2 starts to count from the hold data of the 8-bit counter2.

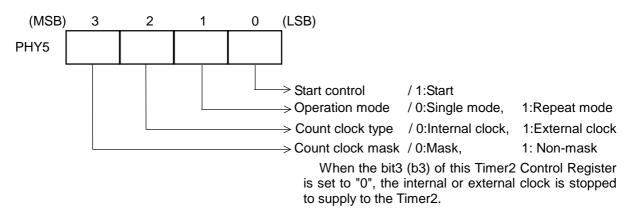

# [Reading from the Timer2 Control Register]

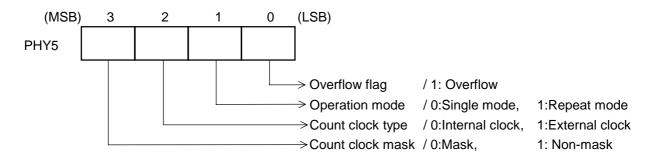

EX.)An example of the Timer2 starting information as the Single mode, the internal clock operation and the released clock mask. (The data of Timer2 Control Register is "1001"(BIN).)

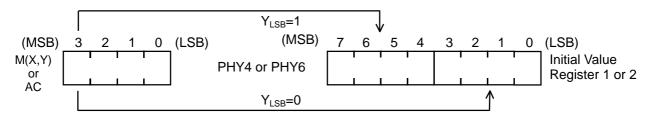

- INITIAL VALUE REGISTER1 / TIMER COUNTER1 {PHY4;(Y'=4, Peripheral register table 0)}

- INITIAL VALUE REGISTER2 / TIMER COUNTER2 {PHY6;(Y'=6, Peripheral register table 0)}

The Initial Value Register consisted of a 8-bit register sets the initial value to the counter, or gets the counted value from the counter.

# [Writing to the Initial Value Register1 or 2]

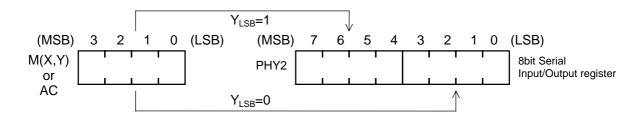

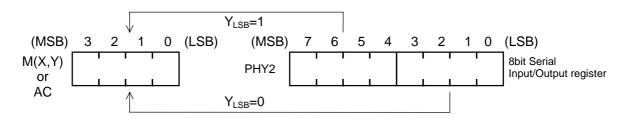

When a data in RAM or Accumulator is transferred to the Initial Value Register, the data is loaded into the higher 4-bit(b7 to b4) or lower4-bit(b3 to b0) of the Initial Value Register in accordance with the condition of LSB of Y-register.

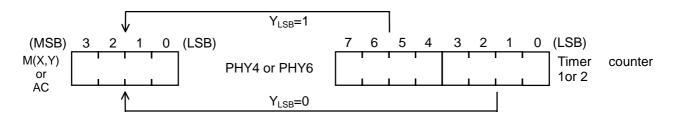

# [Reading from the Timer Counter1 or 2]

When a current data in the Timer Counter1 or Timer Counter2 is transferred into RAM or Accumulator, the data is gotten from higher 4-bit(b7 to b4) or lower 4-bit(b3 to b0) of the Timer Counter1 or Timer Counter2 in accordance with the condition of LSB of Y-register.

# [Reading data from 8-bit Timer Counter1 or 2 to RAM]

Though the data of the Timer and Counter can be read in the count operation, the read data is sometimes incorrect when the clock inputs to the counter during the reading operation.

When the 8-bit counter data is read in count operation as shown in the following timing chart(An example of data reading from the counter to RAM), Timer often counts up between the first 4-bit data reading and the second. In case of the following chart, though the timer data is "0Fh" when the lower 4-bit data is gotten, it is "10h" when the higher 4-bit data is gotten. Therefore the final data becomes to be "1Fh".

# [An example of data reading from the counter to RAM]

There are some other cases to read the incorrect data from the 8-bit counter during the count operation depending on the relation with the external clock speed and the system execution speed.

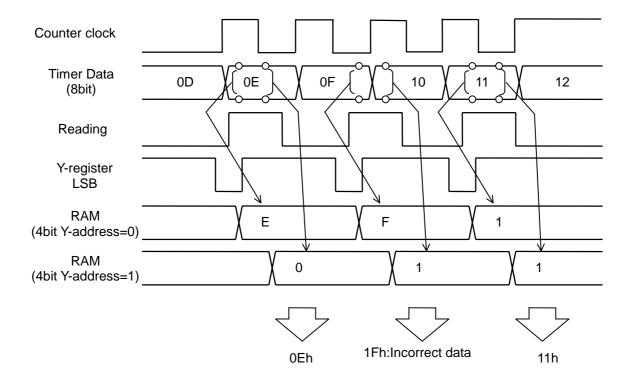

# ■ SERIAL INPUT OUTPUT

SERIAL INPUT OUTPUT consists of the sift registers to convert from 8-bit parallel data to serial data, the 3bit serial clock counter, and the 3-bit serial control register. It operates as the 8-bit serial input or output. The external or internal clock is selected as the shift clock in accordance with the Serial Input / Output control register.

# [Block diagram of the Serial Input Output]

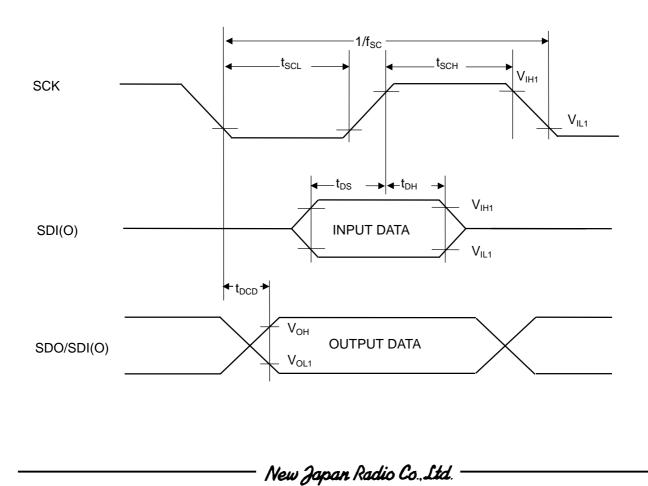

The serial input or output operation starts when the LSB of the Serial Input / Output control register(PHY1) is set to "1". In the external clock operation, the serial input or output operation waits to start until the external clock come in.

When the serial shift register (PHY2) is set the data in advance, the data is output(transmitted) through the SDO or the SDI(O) terminal. The SDI(O) terminal can be changed as a transmitter or a receiver in accordance with the bit3(b3) of PHY1. The data order, MSB or LSB first, is selected by the mask option.

Serial Input Output operates as the 3-wire method using SDI(O), SCK and SDO terminals, or the 2-wire using SDI(O) and SCK terminal.

#### <<The 3-wire method>>

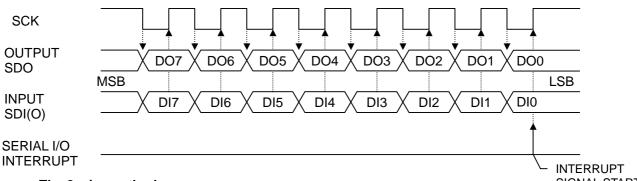

The data synchronized with the falling edge of the SCK clock is output(transmitted) through the SDO terminal. The data synchronized with the rising edge of the SCK clock is input(received) through the SDI(O) terminals.

# [The 3-wire transmission timing chart (MSB first)]

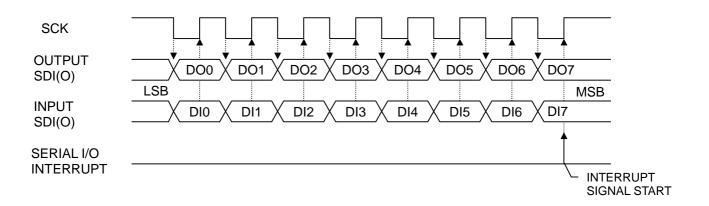

<<The 2-wire method>>

SIGNAL START

The data synchronized with the falling edge of the SCK clock is transmitted through the SDI(O) terminal. The data synchronized with the rising edge of the SCK clock is received through the SDI(O) terminal.

\* In case of the data transmission through the SDI(O) terminal, the SDI(O) terminal must be set as the output by the condition of the bit3(b3) of the Serial Input / Output control register(PHY1) set to "1". In case of the data reception through the SDI(O) terminal, the SDI(O) terminal must be set as the input by the condition of the b3 of PHY1 set to "0".

# [The 2-wire transmission timing chart (LSB first)]

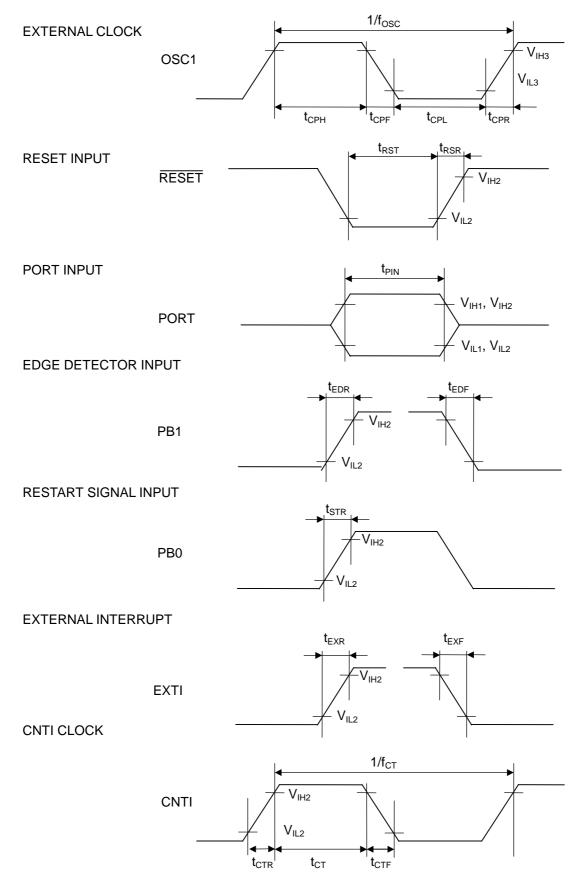

In case of the external clock operation, the external clock is input as the SCK clock to the SCK terminal as shown in the serial transmission timing chart. The signal condition into the SCK terminal must be kept as "HIGH" until the external clock come in. In the transmission, when the SCK with the noise or other redundant signals from the outside of the **NJU3503** input to the SCK terminal, Serial Input Output operates incorrectly. The maximum frequency of the SCK is 500kHz.

In case of the internal clock operation, the SCK outputs through the SCK terminal as shown in the serial transmission timing chart. The internal interrupt signal occurs when the 3-bit counter has counted the SCK clock up to 8 times that means 1-byte serial data transmission end. The internal clock as the SCK is the divided clock in the internal prescaler, and the frequency of the clock can be selected by the mask option from follows which are dividing numbers based on the inverse of the 1-instruction executing period( $1/f_{OSC} \times 6$ ).

#### 1/2, 1/4, 1/8, 1/16, 1/32,1/64, 1/128, 1/256, 1/512, 1/1024, 1/2048,1/4096

- Remarks 1) When the bit2(b2) of Timer1 / Prescaler control register(PHY3) is set to "1", the prescaler generating the internal serial clock is stopped and the internal serial clock is also stopped. Accordingly, Serial Input Output does not operate.

- Remarks 2) If the writing operation is operated to the Serial Input / Output shift register(PHY2) or the Serial Input / Output control register during the transmission or the reception operation, the 3-bit counter is reset and the serial data transmission or reception is stopped. Therefore the writing operation to the above registers must not be operated during the transmission or reception operation.

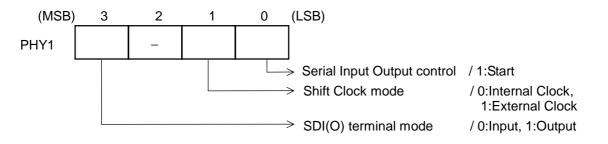

• SERIAL INPUT / OUTPUT CONTROL REGISTER { PHY1 ; (Y'=1) }

When the data of bit1(b1) and bit3(b3) of the Serial Input / Output control register are changed, the operation must be performed before starting the serial transmission. (See the following sample program) In changing the condition of b1 or b2 of PHY1 and setting the LSB of PHY1 to start the transmission are operated in the mean time, Serial Input Output operation does not operate correctly.

# [Writing to the Serial Input / Output Control Register]

EX.) An example of the start procedure in the 3-wire serial data transmission, the external clock operation and the SDI(O) terminal setting as the input.

| :    |         |                                                            |  |

|------|---------|------------------------------------------------------------|--|

| SRPC |         | ;                                                          |  |

| LDI  | Y,1     | ;PHY1(Serial Input / Output control register) is pointed   |  |

| LDI  | A,%0010 | ;"0010"(BIN) is stored to accumulator   External clock,    |  |

| TAP  |         | ;Data is transferred from accumulator to PHY1   Input mode |  |

| LDI  | A,%0011 | ;"0011"(BIN) is stored to accumulator 👘 Transmission       |  |

| TAP  |         | ;Data is transferred from accumulator to PHY1 Starts.      |  |

| :    |         | )<br>J                                                     |  |

| :    |         |                                                            |  |

Remarks 3) In case of the external clock operation at the both of the transmission and reception mode, inputting the external clock must wait while the 2-instruction execution period after that LSB of Serial Input / Output control register is set to "1"(START). (one instruction execution period = 1 / f<sub>OSC</sub> X 6)

If the external clock is input within the 2-instruction execution period, the Serial Input / Output shift register can not recognize the first SCK. The number of the shift operation is decreased a time, 8 times to 7.

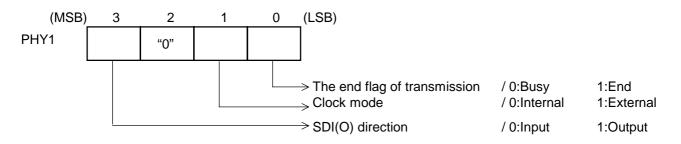

# [Reading from the Serial Input / Output Control Register]

- Remarks 4) The end flag of transmission is set to "1" when the serial data(8 bits) transmission operation is ended. It is cleared by setting the serial data transmission start signal in the Serial Input /Output control register.

- SERIAL INPUT/OUTPUT Shift REGISTER { PHY2 ; (Y'=2) }

The Serial Input / Output Shift register consisted of a 8-bit register operates to set the transmission data or to get the reception data.

# [Writing to the Serial Input / Output Shift Register]

The data in RAM or Accumulator is transferred to the Serial Input / Output Shift register, and it is loaded into lower 4-bit(b0 to b3) or higher(b4 to b7) in PHY2 in accordance with the condition of LSB of Y-register.

#### [Reading from the Serial Input / Output Shift Register]

The Serial Input data is transferred to RAM or Accumulator, it is loaded from lower 4-bit(b0 to b3) or higher(b4 to b7) of PHY2 in accordance with the condition of LSB of Y-register.

New Japan Radio Co., Ltd.

An example of the serial data reception program) In the internal clock operation, SDI(O) terminal is set as the input and the serial input data is transferred to RAM.

|                       | :                                  |                       |                                                                                                                                                                                                                                              |

|-----------------------|------------------------------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ; Interr              | :<br>upt proce                     | SS                    |                                                                                                                                                                                                                                              |

| SINT                  | ORG<br>SRPC                        | \$40                  | ;Interrupt vector address of FULL or EMPTY                                                                                                                                                                                                   |

| SINT                  | LDI<br>TPA                         | Y,1                   | ,<br>;The Serial Input / Output control register is set<br>;                                                                                                                                                                                 |

|                       | TBA<br>JMP<br>JMP                  | 0<br>SIO_OK<br>SINT_E | ;The end flag of transmission is tested<br>;<br>;                                                                                                                                                                                            |

| ,<br>SIO_OK           | LDI<br>RRPC<br>LDI<br>LDI<br>TPMIC |                       | ;The Serial Input / Output shift register is set<br>;RAM to store the serial input data is pointed<br>;RAM address, X=0<br>;RAM address, Y=0<br>;The serial input data is transferred to RAM(lower 4-bit)<br>; and Y-register is incremented |

|                       | TPMIC                              | Y                     | ;The serial input data is transferred to RAM(higher 4-bit)<br>; and Y-register is incremented                                                                                                                                                |

| ,<br>SINT_E           | RETI                               |                       | ; End of the interrupt process                                                                                                                                                                                                               |

| ,<br>; Seri<br>SIO_IN | al data in<br>SRPC                 | putting process       | ·                                                                                                                                                                                                                                            |

|                       | LDI<br>CLA<br>TAP                  | Y,0                   | ;The peripheral register table is set<br>;<br>;                                                                                                                                                                                              |

|                       | LDI<br>LDI                         | Y,1<br>A,%0000        | ;The Serial Input / Output control register is set<br>;The internal clock operation is set and the SDI(O)<br>; terminal is set as the input                                                                                                  |

|                       | TAP<br>LDI<br>TAP                  | A,%0001               | ;<br>;The serial data reception is started<br>;                                                                                                                                                                                              |

| ,                     | :                                  |                       |                                                                                                                                                                                                                                              |

| SIO_DAT               | WSEG<br>DS                         | 2                     | ;The RAM area is set<br>;The area to store the serial input data is secured                                                                                                                                                                  |

An example of the serial data transmitting program) In the internal clock operation, the SDI(O) terminal is set as the output and the data in RAM is transmitted.

|                        | :                                |                                   |                                                                                                                                                                                          |

|------------------------|----------------------------------|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ; Interro              | ORG                              | ss<br>\$40                        | ;Interrupt vector address of FULL or EMPTY                                                                                                                                               |

| SINT                   | SRPC<br>LDI                      | Y,1                               | ;<br>;The Serial Input / Output control register is set                                                                                                                                  |

|                        | TPA<br>TBA<br>JMP<br>JMP         | 0<br>SIO_OK<br>SINT_E             | ;<br>;The end flag of transmission is tested<br>;                                                                                                                                        |

| ,<br>SIO_OK            | RRPC<br>LDI<br>LDI<br>LDI<br>TAM | X,SIO_FLG.X<br>Y,SIO_FLG.Y<br>A,1 | ;The end flag of transmission is set<br>;<br>;                                                                                                                                           |

| ,<br>SINT_E            | RETI                             |                                   | ;End of the interrupt process                                                                                                                                                            |

| ;<br>; Seri<br>SIO_OUT |                                  | ansmitting process<br>Y,0         | ;<br>;The peripheral register table is set<br>;                                                                                                                                          |

| ,                      | LDI                              | Y,2                               | ;The Serial Input / Output shift register is set                                                                                                                                         |

| ,                      | RRPC<br>LDI<br>LDI<br>TMPIC`     | X,SIO_DAT.X<br>Y,SIO_DAT.Y<br>Y   | ;RAM to store the serial output data is set<br>;RAM address, X=0<br>;RAM address, Y=1<br>;The data in RAM is transferred to the Serial Input /<br>; Output shift register(lower 4-bit)   |

|                        | TMPIC                            | Y                                 | <ul> <li>and Y-register is incremented</li> <li>The data in RAM is transferred to the Serial Input /</li> <li>Output shift register(higher 4-bit)</li> <li>&amp; Increments Y</li> </ul> |

| 3                      | SRPC<br>LDI<br>LDI               | Y,1<br>A,%1000                    | ;<br>;The Serial Input / Output control register is set<br>;The internal clock operation and the transmission<br>; mode are set                                                          |

| ;                      | TAP<br>LDI<br>TAP                | A,%1001                           | ;<br>;The serial data transmitting operation is started<br>;                                                                                                                             |

| SIO_DAT<br>SIO_FLG     | :<br>WSEG<br>DS<br>DS            | 2<br>1                            | ;The RAM area<br>;The area to store the serial output data<br>;The end flag of transmission                                                                                              |

# INTERRUPT

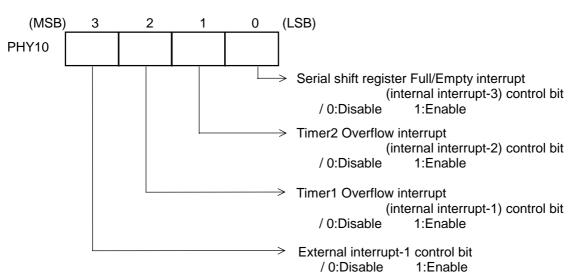

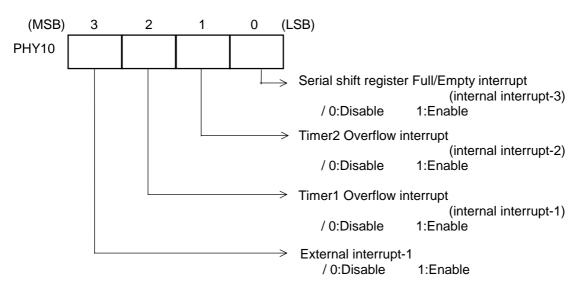

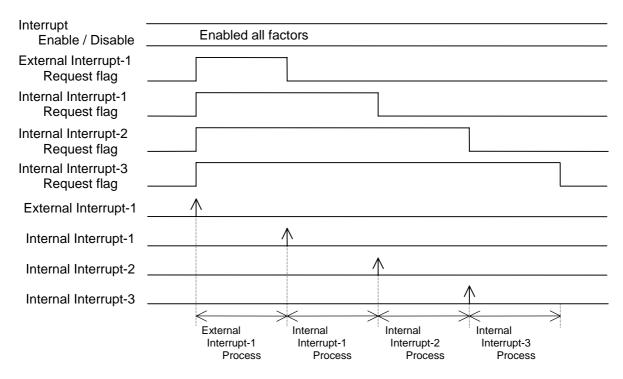

The **NJU3503** prepares four kinds of the interrupt. The interrupt "enable" or "disable" is controlled by the program. The interrupt operates as single process and no multiple. However, when new interrupt request occurs during the other interrupt process, the request is kept, and then the new interrupt process starts after the prior interrupt process. The priority order of the interrupt is that the first is (1)External interrupt-1, the second is (2)Internal interrupt-1, the third is (3)Internal interrupt-2, and the fourth is (4)Internal interrupt-3 as shown below.

When the interrupt request flag is set by the own factor, the interrupt enabled by the interrupt control register (PHY10) stores the data of Program Counter, Accumulator, X-reg, X'-reg, Y'-reg, RPC, and STATUS into the STACK register, and sets the interrupt vector address into Program Counter, and then the interrupt process is started. The return from the interrupt process by "RETI" instruction resets the corresponded interrupt request flag, and regains the held data from STACK, and then the operation before the interrupt process is started continuously. When the interrupt control register disables the interrupt process, the interrupt request flag is not set.

# [ THE PRIORITY ORDER OF FOUR INTERRUPTS ]

| Order | Interrupt                                             | Vector Address(H:HEX) |

|-------|-------------------------------------------------------|-----------------------|

| (1)   | External interrupt-1                                  | 10H                   |

| (2)   | Internal interrupt-1 Timer/Counter-1 Overflow         | 20H                   |

| (3)   | Internal interrupt-2 Timer/Counter-2 Overflow         | 30H                   |

| (4)   | Internal interrupt-3 Serial shift register Full/Empty | 40H                   |

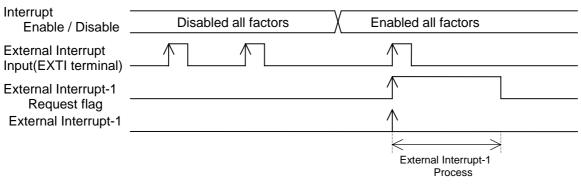

The External interrupt-1 enabled by PHY10 is started the interrupt process when the rising edge of signal pulse is input to the external interrupt signal input terminal(EXTI). The External interrupt-1 request flag is reset by 'RETI' instruction. When the external interrupt-1 occurs during the standby mode by the HALT instruction, the External interrupt-1 request signal is latched and its interrupt process is started after that the standby mode is released.

The Internal interrupt enabled by PHY10 is started the interrupt process when the internal interrupt request flag is set.

The Timer1 and the Timer2 interrupt request flags are independent of the overflow flag, and they are reset by "RETI" instruction, (TIMER)START signal of the Timer control register, or RESET signal from the external circuit. Serial Input Output interrupt request flag is set synchronizing with the transmission end flag when its interrupt is enabled by PHY10. And the flag is reset by the "RETI" instruction or the RESET signal from the external circuit.

INTERRUPT CONTROL REGISTER { PHY10 ; (Y'=10) }

# [Writing to the Interrupt Control Register]

# [Reading from the Interrupt Control Register]

# [Enabled all factors (b0 to b3 of PHY10 were set to "1")]

[From the all factors disabled to the enabled (b0 to b3 of PHY10 are changed from "0" to "1")]

\* The internal interrupt is also ignored while it is disabled.

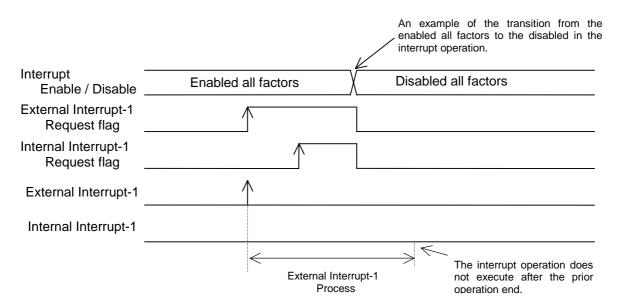

[From the all factors enabled to the disabled (b0 to b3 of PHY10 are changed from "1" to "0")]

\* When the interrupt is enabled, the latest interrupt request occurred during the prior other interrupt process starts its interrupt process after the prior interrupt operation. However, when the interrupt is disabled during the prior interrupt process as shown in above timing chart, the latest interrupt request does not start. But the prior interrupt process is completed.

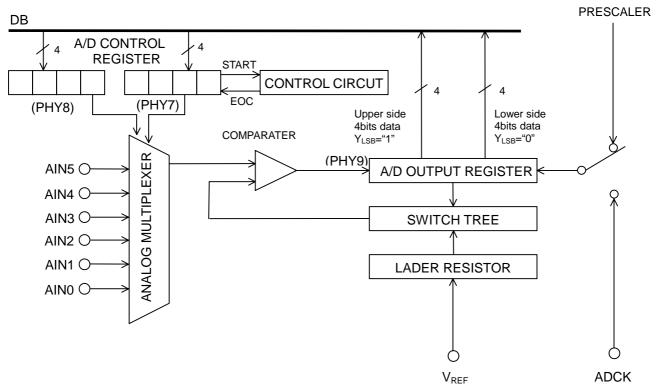

# **A/D CONVERTER**

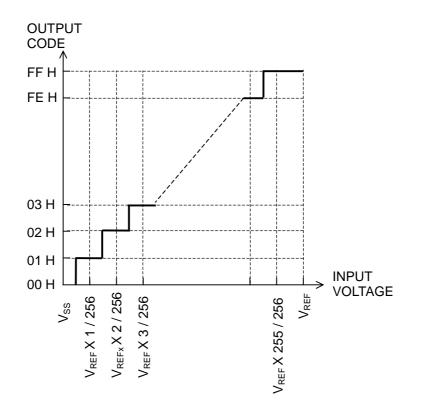

The A/D converter operates with the following specification.

- A/D Conversion : Successive Approximation method : 40µsec (V<sub>DD</sub>=5V, V<sub>REF</sub>=5V, f<sub>ADCK</sub>=225kHz)

- Minimum conversion Time

- Resolution

: 8 bit (256 step)

:  $\pm 2$  LSB (V<sub>DD</sub>=5V, V<sub>REF</sub>=5V)

- Absolute Accuracy

- Reference Voltage

- : 2.4V-AV<sub>DD</sub>

- Analog Input Voltage

- Channel