# MX•CDM, INC. MiXed Signal ICs

**DATA BULLETIN**

# **MX105A** Tone Detector

#### PRELIMINARY INFORMATION

- **FEATURES**

- **Operates in High Noise Conditions**

- ≥36 dB Signal Input Range

- High Sensitivity

- Low Power Operation 2.7 V to 5.5 V

- **Adjustable Bandwidth**

- **Adjustable Frequency**

- **APPLICATIONS**

- **Single and Multitone System Applications**

The MX105A is a monolithic CMOS tone detector for tone decoding in single and multitone signaling systems. Using phase locked loop (PLL) decoding techniques, the MX105A recognizes tones in the presence of high noise levels and strong adjacent channel tones. Detection frequency and bandwidth can each be independently adjusted. The design is immune to high levels of harmonic and sub-harmonic noise. It also maintains excellent noise immunity and constant bandwidth over a wide range of input signal levels.

The MX105A requires a voltage supply of 2.7V to 5.5V and is available in the following package styles: 16-pin SOIC (MX105ADW), 16-pin PDIP (MX105AP), and 24-pin PLCC (MX105ALH).

# **CONTENTS**

| Section                                              | Page |

|------------------------------------------------------|------|

| 1. Block Diagram                                     | 3    |

| 2. Signal List                                       | 4    |

| 3. External Components                               | 5    |

| 4. General Description                               | 6    |

| 5. Application                                       | 7    |

| 5.1 Method for Calculating External Component Values | 7    |

| 5.2 Define fo                                        | 7    |

| 5.3 Calculate Minimum Usable Bandwidth               | 7    |

| 5.4 Calculate The Recommended Operating Bandwidth    | 7    |

| 5.5 Select R4 for Operating BW                       | 8    |

| 5.6 Calculate R2×C2д                                 | 8    |

| 5.7 Define Maximum Allowed Response Time             | 8    |

| 5.8 Calculate R3×C3д                                 | 8    |

| 5.9 Calculate Maximum De-response Time               |      |

| 5.10 Calculate Signal to Noise Performance           | 10   |

| 5.11 Calculate C4 for 30° Phase Shift                | 10   |

| 6. Performance Specification                         | 11   |

| 6.1 Electrical Performance                           | 11   |

| 6.1.1 Absolute Maximum Ratings                       |      |

| 6.1.2 Operating Limits                               | 11   |

| 6.1.3 Operating Characteristics                      |      |

| 6.2 Packaging                                        | 13   |

MX•COM, Inc. reserves the right to change specifications at any time and without notice.

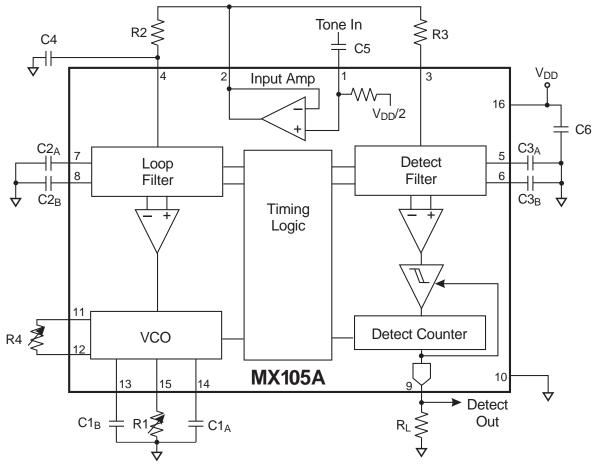

# 1. Block Diagram

Figure 1: Block Diagram

# 2. Signal List

| Pin No. | Pin No. | Name            | Туре   | Description                                                                                                                           |  |  |

|---------|---------|-----------------|--------|---------------------------------------------------------------------------------------------------------------------------------------|--|--|

| DW/P    | LH      |                 |        |                                                                                                                                       |  |  |

| 1       | 1       | INPUT AMP IN    | input  | AC couple to this input. Nominal input impedance is 200 k $\Omega$ .                                                                  |  |  |

| 2       | 3       | INPUT AMP OUT   | output | Nominal output impedance is 1 k $\Omega$ .                                                                                            |  |  |

| 3       | 5       | R3              | input  | Detect filter resistor pin.                                                                                                           |  |  |

| 4       | 6       | R2              | input  | PLL loop filter resistor pin. For improved performance C4 may be chosen to provide 30° of phase shift at the loop filter input.       |  |  |

| 5       | 7       | C3 <sub>A</sub> | output | Detect filter capacitor pin A                                                                                                         |  |  |

| 6       | 8       | C3 <sub>B</sub> | output | Detect filter capacitor pin B                                                                                                         |  |  |

| 7       | 10      | C2 <sub>A</sub> | output | Loop filter capacitor pin A                                                                                                           |  |  |

| 8       | 11      | C2 <sub>B</sub> | output | Loop filter capacitor pin B                                                                                                           |  |  |

| 9       | 13      | DETECT OUT      | output | PMOS open drain output - active on detect.                                                                                            |  |  |

| 10      | 14      | $V_{SS}$        | power  | Ground.                                                                                                                               |  |  |

| 11      | 16      | R4 <sub>A</sub> | input  | Bandwidth control resistor pin A                                                                                                      |  |  |

| 12      | 17      | R4 <sub>B</sub> | input  | Bandwidth control resistor pin B                                                                                                      |  |  |

| 13      | 19      | C1 <sub>B</sub> | output | VCO capacitor B                                                                                                                       |  |  |

| 14      | 20      | C1 <sub>A</sub> | output | VCO capacitor A                                                                                                                       |  |  |

| 15      | 22      | R1              | input  | VCO discharge resistor. When potentiometer tuning is required, a series resistor is recommend to prevent possible shorting to ground. |  |  |

| 16      | 24      | $V_{DD}$        | power  | Power supply.                                                                                                                         |  |  |

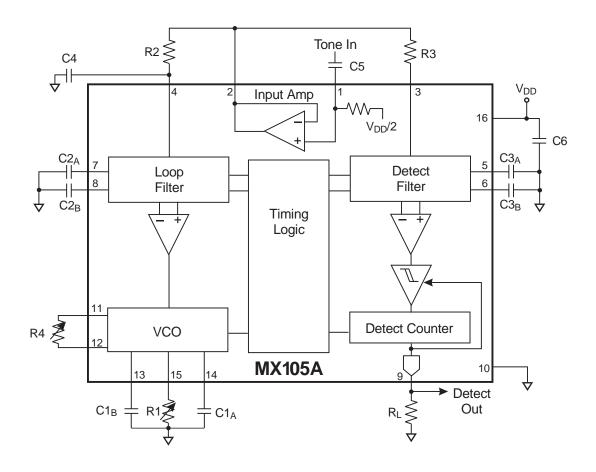

# 3. External Components

Figure 2: Recommended External Components

| R1 <sub>F</sub> | See Section 5.2           | 300kΩ |      |

|-----------------|---------------------------|-------|------|

| R1 <sub>V</sub> | See Section 5.2           | 100kΩ |      |

| R2              | See Section 5.6           |       |      |

| R3              | See Section 5.8           |       |      |

| R4              | See Section 5.5           |       |      |

| R <sub>L</sub>  | Note 4                    | 20kΩ  | ±20% |

| C1 <sub>A</sub> | See Section 5.2<br>Note 2 |       |      |

| C1 <sub>B</sub> | See Section 5.2<br>Note 2 |       |      |

| C2 <sub>A</sub> | See section 5.6  |               |      |

|-----------------|------------------|---------------|------|

|                 | Note 2           |               |      |

| C2 <sub>B</sub> | See Section 5.6  |               |      |

|                 | Note 2           |               |      |

| C3 <sub>A</sub> | See Section 5.8  |               |      |

|                 | Note 2           |               |      |

| C3 <sub>B</sub> | See Section 5.8  |               |      |

|                 | Note 2           |               |      |

| C4              | See Section 5.11 |               |      |

|                 | Note 1, 2        |               |      |

| C5              |                  | 0.27µF        | ±20% |

| C6              |                  | 0.1µF         | ±20% |

|                 |                  |               |      |

| D1              | See Section 5.9  | small signal  |      |

|                 | Note 3           | diode (1N914) |      |

# **External Components Notes:**

- 1. For improved performance, C4 may be chosen to provide 30° phase shift at the VCO loop filter input.

- 2. For compatibility with the MX105; capacitors (C1 C4) may be connected to V<sub>DD</sub> instead of V<sub>SS</sub>.

- 3. For improved de-response time, a diode (D1) may be added.

- 4. Any value load resistance (R<sub>L</sub>) may be used, providing the maximum load current does not exceed the value given in 'Maximum Ratings Specifications'.

# 4. General Description

The MX105A implements a frequency detector with a phase locked loop (PLL) and a lock detector. The voltage controlled oscillator (VCO) center frequency, detection bandwidth, loop filter, and detect filter are all independently controlled by external components.

The MX105A provides a pair of pseudo-sinewave multipliers for splitting the input signal into approximately orthogonal components. These multipliers are implemented with commutating filters (cyclically sampling filters) which translate an in band AC input signal to DC. The commutating loop filter is used as the phase detector of the PLL while the commutating detect filter provides for lock detection. Each pseudo-sinewave has a cyclic form (1 1 0 -1 -1 0) to eliminate low order harmonic responses. The loop filter produces an error signal, which when applied to the VCO input allows frequency locking. A limiter between the loop filter output and the VCO input provides tunable control of the detection bandwidth (BW). Once lock is achieved the detect filter produces a DC value proportional to the input tone amplitude. An internally generated reference is compared to the detect filter output to determine whether the PLL is locked to an input tone. Once lock is determined the internal reference is reduced by 50% to minimize output chatter with marginal input signals.

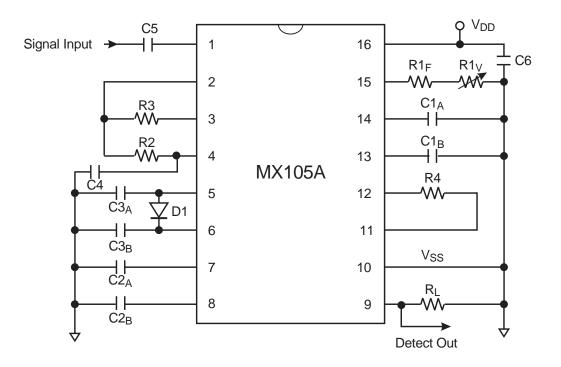

The sampling clocks of the detect filter lag those of the loop filter by 60°. To improve performance, a capacitor (C4) can be used to phase shift the input to the loop filter by 30°. This shifts all sampling clocks an additional 30° relative to the input tone to phase align the detect filter sampling clocks with the amplitude peaks of the input tone.

Figure 3 shows the sampling clocks relative to an in band input tone; this figure represents the steady state 'locked' condition without C4.

Figure 3: Sampling Clocks of Commutating Filters

# 5. Application

The external components shown in Figure 2 are used to adjust the various performance parameters of the MX105A. The signal-to-noise performance, response time and signal bandwidth are all interrelated factors which should be optimized to meet the requirements of the application.

By selecting component values in accordance with the following formulas, optimum circuit performance is obtained for any given application.

First define the following application parameters:

- A. The center frequency to be detected  $(f_0)$ .

- B. The MX105A Minimum Usable Bandwidth (MUBW). This is obtained by taking into account the worst case tolerances on the input tone frequency and variations in the MX105A f<sub>0</sub> due to supply voltage and any temperature effect of the MX105A and its supporting components.

- C. The maximum permissible MX105A response time.

- D. The minimum input signal amplitude.

**Note:** Using this information the appropriate component values can be calculated, and the signal-to-noise performance can be read from a chart. Do not add large safety margins for response time and minimum signal amplitude; reasonable margins are already included in the formulas. Excessive margins may result in reduced noise immunity.

# 5.1 Method for Calculating External Component Values

The examples on the following pages demonstrate the calculation of component values for any given application. For the purpose of the examples, the values below are used:

- A.  $f_0 = 2800 \text{ Hz}$

- B.  $\Delta TEMP = 100 \,^{\circ}C$ ,  $\Delta V_{DD} = 1V$ ,  $\Delta f_{IN} = 0.5\%$

- C. Maximum allowed response time = 50ms

- D. Minimum input signal amplitude = 200 mV<sub>RMS</sub>.

# 5.2 Define fo

The components R1, C1<sub>A</sub> and C1<sub>B</sub> set the free running frequency of the VCO and therefore the  $f_0$  of the MX105A. As shown below, the frequency of 2800 Hz corresponds to a capacitor value of 220pF and a resistor value of 385 k $\Omega$ . This resistance can be achieved with a 300 k $\Omega$  fixed resistor for R1<sub>F</sub> and for R1<sub>V</sub> a 100 k $\Omega$  potentiometer. The capacitance of C1<sub>A</sub> and C1<sub>B</sub> should include 10-20pF parasitic capacitance due to the device and its package plus any board parasitic capacitance.

$$f_0 = \frac{1}{K \cdot R1(C1_A + C1_B)} \Rightarrow R1 \times C1_A = \frac{1}{2Kf_0}$$

where:

$$K = 2.1 \pm 5\%$$

$R1 = (R1_F + R1_V)$

#### 5.3 Calculate Minimum Usable Bandwidth

Minimum Usable Bandwidth (MUBW) is the TOTAL bandwidth required for the following:

- A. Input signal frequency tolerance

- B. MX105A  $f_0$  temperature coefficient ( $T_C = 100 \text{ ppm/}^{\circ}\text{C}$ )

- C. MX105A  $f_0$  supply voltage coefficient ( $V_C = 5000 \text{ ppm/V}$ )

Note: Add A, B and C and express as TOTAL bandwidth, not as a ± percentage (%) value.

MUBW =

$$\Delta f_0 + T_C \Delta TEMP + V_C \Delta V$$

MUBW = 0.5 + 0.01 × 100 + 0.5 × 1 = 2%

# 5.4 Calculate The Recommended Operating Bandwidth

$$BW = \frac{10 + MUBW}{2} = \frac{10 + 2}{2} = 6\%$$

## 5.5 Select R4 for Operating BW

$$R4 = \frac{4.8 \times BW}{10.35 - BW} = \frac{4.8 \times 6}{10.35 - 6} \approx 6.8 \text{k}\Omega$$

The exact bandwidth given by any value of R4 will vary slightly. In applications where an exact bandwidth is required, R4 should be a variable resistor to permit adjustment.

# 5.6 Calculate R2×C2A

$$R2 \times C2_A \approx \frac{100}{3 \times f_0 \times BW}$$

For a frequency of 2800 Hz, a bandwidth of 6%, and a choice of  $C2_A = 0.01 \mu F \Rightarrow R_V = 200 k\Omega$ .

Note: Use nearest preferred values.

# 5.7 Define Maximum Allowed Response Time

The maximum response time  $(T_{ON})$  is the sum of the VCO lock time  $(T_{LOCK})$  and the DETECT integration time  $(T_{DETECT})$ . The MX105A's  $T_{ON}$  must not exceed the maximum time allowed for the application, but a value lying near the maximum gives the best S/N performance.

A. Calculate T<sub>LOCK</sub>

$$T_{LOCK} = \frac{150}{f_0 \times BW}$$

Using the formula above, for a frequency of 2800 Hz and a bandwidth of 6% the approximate Lock time ( $T_{LOCK}$ ) will be 9 ms. Since the maximum response time is 50 ms, a DETECT time of 41 ms is allowed.

Note: T<sub>LOCK</sub> may vary from near zero to the value given, causing corresponding variations in actual T<sub>ON</sub>.

B. Calculate Maximum Allowable T<sub>DETECT</sub>

$$T_{DETECT} = T_{ON_{MAX}} - T_{LOCK}$$

C. Define Minimum Expected Signal Amplitude  $\left(V_{\text{IN}_{\text{MIN}}}\right)$

This is used in calculating T<sub>DETECT</sub> components.

#### 5.8 Calculate R3×C3<sub>A</sub>

$$R3 \times C3_{A} \approx \frac{T_{DETECT}}{-3 \times In \left(1 - \frac{V_{TH}}{V_{IN_{MIN}}}\right)}$$

where: V<sub>TH</sub> is the detect filter sensitivity.

#### Note:

- 1. For a signal amplitude of 200 mV<sub>RMS</sub>, a resistor value R3 of 510 k $\Omega$  with a 0.1 $\mu$ F capacitor for C3<sub>A</sub> and C3<sub>B</sub> will yield a T<sub>DETECT</sub> time of 20ms. This in turn yields a response time of 9ms + 20 ms = 29ms.

- Use nearest preferred values.

# 5.9 Calculate Maximum De-response Time

$$T_{OFF} \approx -3 \times In \left( \frac{V_{TH}}{V_{IN_{MAX}}} \right) R3 \times C3_A$$

where: V<sub>TH</sub> is the detect filter sensitivity.

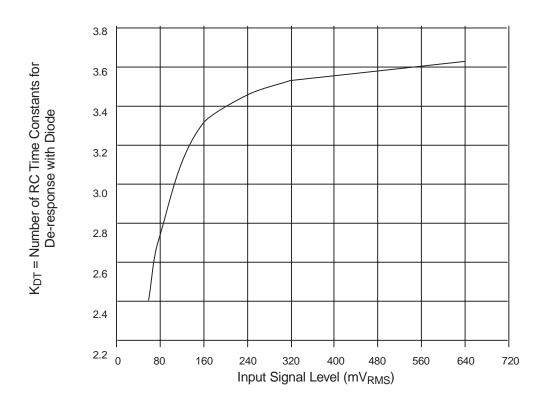

For improved de-response time, a diode (1N914 or similar) can be placed between pins 5 and 6, as shown in Figure 3. The formula and figure below show the approximate time the MX105A will take to turn off after an in-band signal has been removed. The effect of this diode is to greatly reduce the turn-off time with signal input amplitudes greater than 300 mV<sub>RMS</sub>. This graph is for  $V_{DD} = 5V$ ; for lower  $V_{DD}$  KDT increases.

$$T_{OFF} \approx K_{DT} \times R3 \times C3_A$$

Figure 4: K<sub>DT</sub> Factor for T<sub>OFF</sub> vs. Signal Input Amplitude

# 5.10 Calculate Signal to Noise Performance

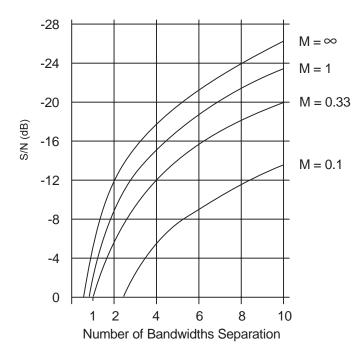

Worst-case S/N calculations depend on calculation of a value "M" using the formula shown below:

$$M = \frac{R3 \times C3_A}{3 \times R2 \times C2_A}$$

substituting example values,

$$M = \frac{510 \times 0.1}{3 \times 200 \times 0.01} = 8.5$$

By substituting this value for M in Figure 5, the minimum required S/N of an in band tone with respect to an adjacent interfering tone can be found. This then has to be increased depending on the input tone amplitude.

Figure 5: S/N vs. BW Separation

The following formula expresses the reduction in noise immunity as the input signal approaches the detect filter sensitivity  $V_{TH}$ .

required

$$\frac{S}{N} = 20 \log \left( \frac{V_{IN}}{V_{IN} - V_{TH}} \right) + \frac{S}{N_{Figure 5}}$$

If this S/N is better than required for the application, R3×C3<sub>A</sub> can be reduced, or the operating bandwidth can be increased to obtain a faster tone detection time.

If the S/N performance is not adequate, the operating bandwidth can be reduced toward the MUBW, or R3C3<sub>A</sub> can be increased to improve S/N performance at the expense of slower response time.

#### 5.11 Calculate C4 for 30° Phase Shift

Capacitor C4 is used to phase shift the input to the VCO commutating filter by 30°, thereby shifting the sampling clocks by the same amount. This enables the Detect sampling filter to sample and integrate at the maximum and minimum of the input tone.

$$C4 = \frac{tan(30^\circ)}{2\pi \times f_0 \times R_V} \approx \frac{0.092}{f_0 \times R_V} \approx 164 pF$$

# 6. Performance Specification

# **6.1 Electrical Performance**

### 6.1.1 Absolute Maximum Ratings

Exceeding these maximum ratings can result in damage to the device.

| General                                       | Min. | Max.           | Units            |  |

|-----------------------------------------------|------|----------------|------------------|--|

| Supply (V <sub>DD</sub> - V <sub>SS</sub> )   | -0.3 | 7.0            | V                |  |

| Voltage on any pin (wrt V <sub>SS</sub> )     | -0.3 | $V_{DD} + 0.3$ | V                |  |

| Current                                       |      |                |                  |  |

| $V_{DD}$                                      | -30  | 30             | mA               |  |

| $V_{SS}$                                      | -30  | 30             | mA               |  |

| Any other pins                                | -20  | 20             | mA               |  |

| Max. Output Switch Load Current               |      | 10             | mA               |  |

| P/LH/DW Package                               |      |                |                  |  |

| Device Dissipation at T <sub>AMB</sub> = 25°C |      | 800            | mW               |  |

| Derating above 25°C                           |      | 13             | mW/°C above 25°C |  |

| Storage Temperature                           | -40  | 85             | °C               |  |

| Operating Temperature                         | -30  | 85             | °C               |  |

# 6.1.2 Operating Limits

Correct operation of the device outside these limits is not implied.

|                                             | Notes | Min. | Тур.    | Max. | Units |

|---------------------------------------------|-------|------|---------|------|-------|

| Supply (V <sub>DD</sub> - V <sub>SS</sub> ) |       | 2.7  | 3.3/5.0 | 5.5  | V     |

| Operating Temperature                       |       | -30  |         | 85   | °C    |

### 6.1.3 Operating Characteristics

For the following conditions unless otherwise specified:

$V_{DD} = 5.0 \text{ V } @ T_{AMB} = 25 ^{\circ}\text{C}$

Load resistance on decoder output =  $20k\Omega$ .

|                                            | Notes | Min. | Тур. | Max.    | Units                |

|--------------------------------------------|-------|------|------|---------|----------------------|

| Static Parameters                          |       |      |      |         |                      |

| I <sub>DD</sub>                            |       |      | 1.0  |         | mA                   |

| Amplifier Input Impedance                  |       | 160  | 200  |         | kΩ                   |

| Digital Output Impedance                   |       |      | 500  | 1000    | Ω                    |

| Analog Output Impedance                    |       |      | 1000 | 1200    | Ω                    |

| Dynamic Parameters                         |       |      |      |         |                      |

| Input Signal                               |       |      |      |         |                      |

| Frequency                                  |       | 40   |      | 20,000  | Hz                   |

| Lowest Must Detect Level                   | 1     |      | 30   |         | ${\rm mV}_{\rm RMS}$ |

| Highest Will Not Detect Level              | 1     |      | 20   |         | $mV_{RMS}$           |

| Highest Will Not Detect f <sub>0</sub> /2  | 1, 2  |      | 30   |         | dB                   |

|                                            |       |      | 790  |         | $mV_{RMS}$           |

| Highest Will Not Detect 5(f <sub>0</sub> ) | 1, 2  |      | 20   |         | dB                   |

|                                            |       |      | 250  |         | $mV_{RMS}$           |

| VCO                                        |       |      |      |         |                      |

| Frequency                                  | 3     | 120  |      | 120,000 | Hz                   |

| Frequency Stability                        |       |      | 100  |         | ppm/°C               |

|                                            |       |      | 5000 |         | ppm/V                |

| BW Limiter                                 |       |      |      |         |                      |

| BW Range                                   |       | 2    |      | 10      | %f <sub>0</sub>      |

| Amplifier                                  |       |      |      |         |                      |

| Open Loop Gain                             |       |      | 60   |         | dB                   |

| GBWP                                       |       |      | 1.0  |         | MHz                  |

| Closed Loop Gain                           |       |      | 0    |         | dB                   |

| Detect Commutating Filter                  |       |      |      |         |                      |

| Sensitivity (V <sub>TH</sub> )             | 1     |      | 25   |         | $mV_{RMS}$           |

#### **Operating Characteristics Notes:**

- 1. Multiply by V<sub>DD</sub> /5V for other supply values.

- 2. The reference level is V<sub>TH</sub>. The following formula converts dB to mV<sub>RMS</sub>.

$$mV_{RMS} = {}_{10}{}^{(dB/20)} \times V_{TH}$$

3. Observing pins 13, 14, or 15 (DW/J package) will cause a frequency shift due to additional loading. If tuning center frequency by observing oscillator, design in a buffer amplifier between pin 15 and probe/calibration point and tune with no input signal. Otherwise, tune by observing detect output band edges while sweeping input signal. VCO center frequency is 6(f<sub>0</sub>) at pin 15 while it is 3(f<sub>0</sub>) at pins 13 and 14.

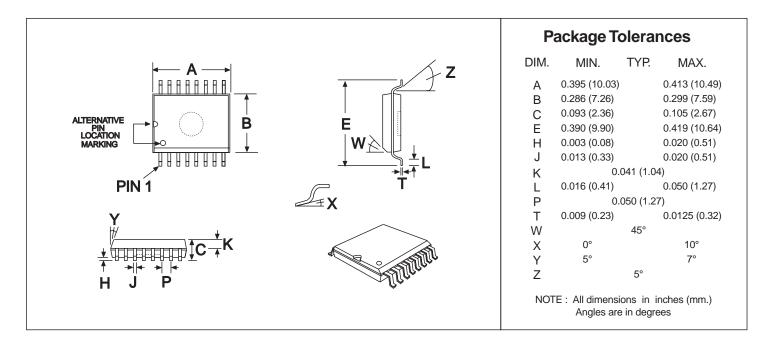

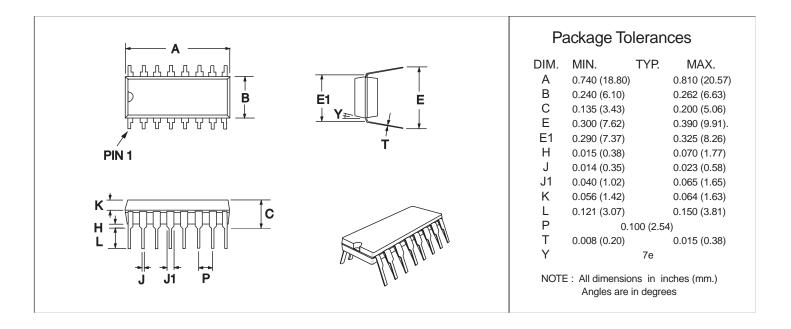

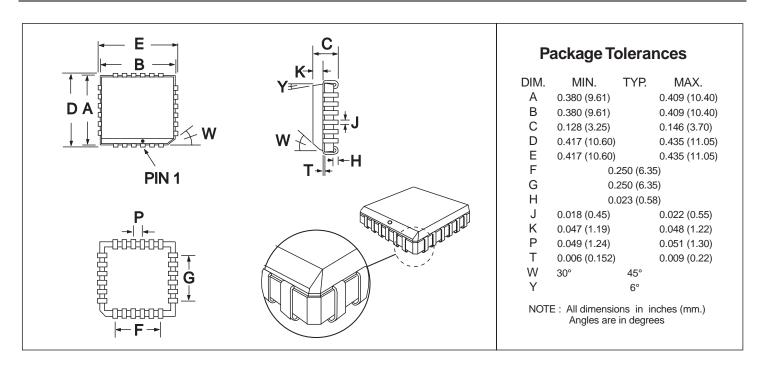

# 6.2 Packaging

Figure 6: 16-pin SOIC Mechanical Outline: Order as part no. MX105ADW

Figure 7: 16-pin PDIP Mechanical Outline: Order as part no. MX105AP

Figure 8: 24-pin PLCC Mechanical Outline: Order as part no. MX105ALH

#### **CML Product Data**

In the process of creating a more global image, the three standard product semiconductor companies of CML Microsystems Plc (Consumer Microcircuits Limited (UK), MX-COM, Inc (USA) and CML Microcircuits (Singapore) Pte Ltd) have undergone name changes and, whilst maintaining their separate new names (CML Microcircuits (UK) Ltd, CML Microcircuits (USA) Inc and CML Microcircuits (Singapore) Pte Ltd), now operate under the single title CML Microcircuits.

These companies are all 100% owned operating companies of the CML Microsystems Plc Group and these changes are purely changes of name and do not change any underlying legal entities and hence will have no effect on any agreements or contacts currently in force.

### **CML Microcircuits Product Prefix Codes**

Until the latter part of 1996, the differentiator between products manufactured and sold from MXCOM, Inc. and Consumer Microcircuits Limited were denoted by the prefixes MX and FX respectively. These products use the same silicon etc. and today still carry the same prefixes. In the latter part of 1996, both companies adopted the common prefix: CMX.

This notification is relevant product information to which it is attached.

### CML Microcircuits (USA) [formerly MX-COM, Inc.] Product Textual Marking

On CML Microcircuits (USA) products, the 'MX-COM' textual logo is being replaced by a 'CML' textual logo.

Company contact information is as below:

COMMUNICATION SEMICONDUCTORS

Oval Park, Langford, Maldon, Essex, CM9 6WG, England Tel: +44 (0)1621 875500 Fax: +44 (0)1621 875600 uk.sales@cmlmicro.com www.cmlmicro.com

COMMUNICATION SEMICONDUCTORS

4800 Bethania Station Road, Winston-Salem, NC 27105, USA Tel: +1 336 744 5050,

0800 638 5577

Fax: +1 336 744 5054

us.sales@cmlmicro.com

www.cmlmicro.com

No 2 Kallang Pudding Road, 09-05/ 06 Mactech Industrial Building, Singapore 349307

Tel: +65 7450426 Fax: +65 7452917 sg.sales@cmlmicro.com www.cmlmicro.com