# **OKI** Semiconductor

## MSM54V16258B/BSL

#### 262,144-Word x 16-Bit DYNAMIC RAM: FAST PAGE MODE TYPE WITH EDO

#### DESCRIPTION

The MSM54V16258B/BSL is a 262,144-word x 16-bit dynamic RAM fabricated in OKI's CMOS silicon gate technology. The MSM54V16258B/BSL achieves high integration, high-speed operation, and low-power consumption due to quadruple polysilicon double metal CMOS. The MSM54V16258B/BSL is available in a 40-pin plastic SOJ or 44/40-pin plastic TSOP.

#### **FEATURES**

- · Single3.3V power supply, ±0.3V tolerance

- · Input :TTL compatible

- · Output :TTL compatible, 3-state

- Refresh: 512 cycles/64ms

- · Fast page mode with EDO, read modify write capability

- Byte wide control: 2 CAS control

- · CAS before RAS refresh, Hidden refresh, RAS only refresh capability

- · CAS before RAS self-refresh capability (SL Version.)

- Pachage: 40-Pin 400 mil plastic SOJ (SOJ40-P-400) (Product: MSM54V16258B/BSL-xxJS)

44/40-Pin 400 mil plastic TSOP (TSOP44/40-P-400/0.8-K) (Product : MSM54V16258B-xxTS-K)

(Product: MSM54V16258BSL-xxTSK) xx: indicates speed rank.

#### PRODUCT FAMILY

| Family              | A    | ccess Tin | ne (Max.)    |              | Cycle Tim | e (Min.) |                   |  |

|---------------------|------|-----------|--------------|--------------|-----------|----------|-------------------|--|

|                     | trac | taa       | <b>t</b> CAC | <b>t</b> oea | trc       | thpc     | Power Dissipation |  |

| MSM54V16258B/BSL-40 | 40ns | 22ns      | 10ns         | 10ns         | 80ns      | 15ns     | 432mW             |  |

| MSM54V16258B/BSL-45 | 45ns | 24ns      | 12ns         | 12ns         | 90ns      | 17ns     | 396mW             |  |

| MSM54V16258B/BSL-50 | 50ns | 26ns      | 12ns         | 14ns         | 100ns     | 20ns     | 360mW             |  |

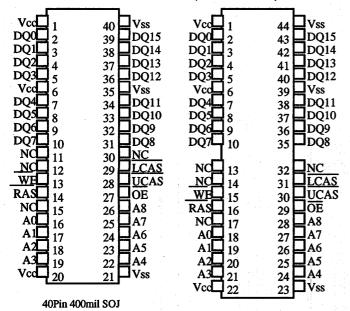

#### PIN CONFIGURATION (TOP VIEW)

| 44/40Pin | 400mil | TSOP |

|----------|--------|------|

|          |        |      |

| Pin Names | Function                |

|-----------|-------------------------|

| A0-A8     | Address Input           |

| RAS       | Row Address Strobe      |

| LCAS,UCAS | Column Address Strobe   |

| DQ0-15    | Data-Input/ Data-Output |

| WE        | Write Enable            |

| <u>OE</u> | Output Enable           |

| Vcc       | Power Supply (3.3V)     |

| Vss       | Ground (0V)             |

| NC        | No Connection           |

#### Note1:

The same power supply voltage must be provided to every Vcc pin, and the same GND voltage level must be provided to every Vss pin.

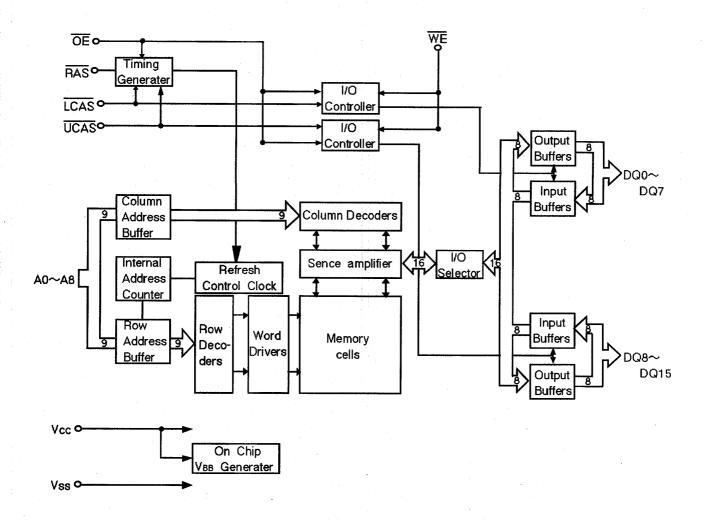

### **BLOCK DIAGRAM**

### **FUNCTION TABLE**

|     |           |      |    |    |            | <u> </u>   | -                |  |  |

|-----|-----------|------|----|----|------------|------------|------------------|--|--|

|     | Input Pin |      |    |    | DO         | )Pin       | Functional Made  |  |  |

| RAS | LCAS      | UCAS | WE | ŌĒ | DQ0~DQ7    | DQ8~DQ15   | Functinal Mode   |  |  |

| Н   | *         | *    | *  | *  | High-Z     | High-Z     | Standby          |  |  |

| L   | H         | Н    | *  | *  | High-Z     | High-Z     | Refresh          |  |  |

| L   | L         | Н    | Н  | L  | Dout       | High-Z     | Lower Byte Read  |  |  |

| L   | Н         | L    | Н  | L  | High-Z     | Douт       | Upper Byte Read  |  |  |

| L   | L         | L    | Н  | ٦  | Dout       | Dout       | Word Read        |  |  |

| L   | L         | Н    | L  | Н  | DIN        | Don't Care | Lower Byte Write |  |  |

| L   | Н         | L    | L  | Н  | Don't Care | Din        | Upper Byte Write |  |  |

| L   | L         | L    | L  | Н  | Din        | Din        | Word Write       |  |  |

| L   | L         | L    | Н  | Н  | High-Z     | High-Z     | <del></del>      |  |  |

### **ELECTRICAL CHARACTERISTICS**

## Absolute Maximum Ratings

| Rating                             | Symbol | Conditions | Value     | Unit |

|------------------------------------|--------|------------|-----------|------|

| Voltage on any pin relative to Vss | Vt.    | Ta=25°C    | -0.5~+4.6 | ٧    |

| Short circuit output current       | los    | Ta=25°C    | 50        | mΑ   |

| Power dissipation                  | Po     | Ta=25°C    | 1         | W    |

| Operrating temperrature            | Topr   | _          | 0~+70     | ů    |

| Storage temperature                | Tstg   | -          | -55~+150  | °C   |

## Recommended Operating Conditions

(Ta=0°C to 70°C)

| Parameter          | Symbol | Conditions | Min. | Тур. | Max.    | Unit |

|--------------------|--------|------------|------|------|---------|------|

| Supply voltage     | Vcc    | _          | 3.0  | 3.3  | 3.6     | V    |

|                    | Vss    | _          | 0    | 0    | 0       | V    |

| Input high voltage | Vih    |            | 2.4  | _    | Vcc+0.3 | ٧    |

| Input low voltage  | Vil    | _          | -0.3 | _    | 0.8     | ٧    |

## Capacitance

(Vcc=3.3V±0.3V,Ta=25°C,f=1MHz)

| Parameter                                   | Symbol | Conditions | Тур. | Max. | Unit |

|---------------------------------------------|--------|------------|------|------|------|

| Input capacitance (A0~A8)                   | Cint   | . –        | _    | 8    | pf   |

| Input capacitance (RAS, LCAS, UCAS, WE, OE) | Cin2   | _          | _    | 8    | pf   |

| Input / output capacitance (DQ0~DQ15)       | C1/0   | _          | _    | 9    | pf   |

### DC CHARACTERISTICS

(Vcc=3.3V±0.3V , Ta=0 to 70℃)

| D                                                          |                  |                                          | MSM54V16258<br>B/BSL-40<br>Min. Max. |     | MSM54        |      |            | V16258<br>SL-50 |            |         |

|------------------------------------------------------------|------------------|------------------------------------------|--------------------------------------|-----|--------------|------|------------|-----------------|------------|---------|

| Parameter                                                  | Symbol           | Condition                                |                                      |     | Min.         | Max. | Min.       | Max.            | Unit       | Note    |

| Output High Voltage                                        | Vон              | lон= - 1.0mA                             | 2.4                                  | Vcc | 2.4          | Vcc  | 2.4        | Vcc             | ٧          |         |

| Output Low Voltage                                         | Vol              | loL= 2.0mA                               | 0                                    | 0.4 | 0            | 0.4  | 0          | 0.4             | ٧          |         |

| Input Leakage Current                                      | lu               | 0V≦Vin≦Vcc                               | -10                                  | 10  | -10          | 10   | -10        | 10              | μΑ         |         |

| Output Leakage Current                                     | Iro              | DQi Disable<br>0V≦V₀≦5.5V                | -10                                  | 10  | -10          | 10   | -10        | 10              | μΑ         |         |

| Average Power<br>Supply Current<br>(Operating)             | lcc <sub>1</sub> | RAS,CAS Cycling<br>tnc=Min.              |                                      | 120 |              | 110  | _          | 100             | mA         | 1,2     |

| Power Supply<br>Current (Standby)                          | lcc2             | RAS,CAS = VIH                            |                                      | 2   | _            | 2    | _          | 2               | mA         | 1       |

| Average Power<br>Supply Current<br>(RAS only Refresh)      | lccs             | RAS=Cycling CAS=ViH trc=Min.             | _                                    | 110 | -<br>-       | 100  | _          | 90              | mA         | 1,2     |

| Average Power<br>Supply Current<br>(Fast Page Mode)        | lcc4             | RAS=VIL<br>CAS Cycling<br>thec=Min.      | <del>_</del>                         | 70  | _            | 65   | _          | 60              | mA         | 1,3     |

| Average Power Supply Current (CAS Before RAS Refresh)      | lcc5             | RAS=Cycling<br>CAS Befor RAS             |                                      | 100 | _            | 90   |            | 80              | m <b>A</b> | 1,2     |

| Average Power<br>Supply Current<br>(Battery Backup)        | Icce             | tRC=125 μs<br>CAS Befor RAS<br>tRAS≦1 μs | <del>-</del> .                       | 300 | -            | 300  | _          | 300             | μΑ         | 1,2,4,5 |

| Average Power Supply Current (CAS Before RAS Self-Refresh) | lccs             | RAS=VIL<br>CAS=VIL                       | -<br>-                               | 300 | <del>-</del> | 300  | - <u>-</u> | 300             | μΑ         | 1,2,4,5 |

Notes: 1. Icc Max. is specified as Icc for the output open cindition

<sup>2.</sup> Address can be changed once or less while RAS=VIL.

<sup>3.</sup> Address can be changed once or less while CAS=VIH.

<sup>4.</sup> Vcc-0.2V $\leq$ VIH $\leq$ 6.5V, -1.0V $\leq$ VIL $\leq$ 0.2V.

<sup>5.</sup> SL version.

## AC CHARACTERISTICS (1/2)

$(Vcc = 3.3V \pm 0.3V, Ta = 0\sim70^{\circ}C)$

|                                            |              | MSM54V16258   MSM54V16258 |         |      |          | $(\text{Vcc} = 3.3\text{V} \pm 0.3\text{V},$<br>MSM54V16258 |            |      | 0~70 C) |

|--------------------------------------------|--------------|---------------------------|---------|------|----------|-------------------------------------------------------------|------------|------|---------|

| Parameter                                  | Symbol       | B/BS                      |         | B/BS |          | B/BS                                                        |            | Unit | Note    |

|                                            |              | MIN                       | MAX     | MIN  | MAX      | MIN                                                         | MAX        |      | 11010   |

| Random read or write cycle time            | tric         | 80                        |         | 90   | _        | 100                                                         | _          | ns   |         |

| Read/Write cycle time                      | trmw         | 115                       | _       | 130  | _        | 145                                                         | _          | ns   |         |

| Fast page mode cycle time                  | tнрс         | 15                        | _       | 17   | _        | 20                                                          | _          | ns   |         |

| Fast page mode read/write cycle time       | tprmw        | 55                        |         | 60   |          | 65                                                          | _          | ns   |         |

| Access time from RAS                       | trac         | _                         | 40      | -    | 45       | _                                                           | 50         | ns   | 7,12,13 |

| Access time from CAS                       | tcac         | _                         | 10      | -    | 12       |                                                             | 14         | ns   | 7,12    |

| Access time from column address            | taa          |                           | 22      | _    | 24       |                                                             | 26         | ns   | 7,13    |

| Access time from OE                        | <b>t</b> OEA | _                         | 10      | _    | 12       |                                                             | 14         | ns   |         |

| Access time from CAS precharge             | tcpa .       | -                         | 24      | . —  | 26       |                                                             | 28         | ns   | 7,12    |

| Output low impedance time from CAS         | tcLz         | 0                         | _       | 0    | -        | 0                                                           | _          | ทธ   |         |

| Data hold after CAS low                    | tсон         | 3                         | _       | 3    | _        | 3                                                           | _          | ns   | 17      |

| Output buffer turn-off delay time          | toff         | 3                         | 8       | 3    | 8        | 3                                                           | 8          | ns   | 8       |

| Output buffer turn-off delay time from OE  | toez         | 3                         | 8       | 3    | 8        | 3                                                           | 8          | ns   | 8       |

| Output buffer turn-off delay time from RAS | trez         | 3                         | 8       | 3    | 8        | 3                                                           | 8          | ns   | 8       |

| Output buffer turn-off delay time from WE  | twez         | 3                         | 8       | 3    | 8        | 3                                                           | 8          | ns   | 8       |

| Transition time                            | tr           | 2                         | 35      | 2    | 35       | 2                                                           | 35         | ns   |         |

| Refresh preiod                             | tref         | _                         | 64      |      | 64       | _                                                           | 64         | ms   |         |

| RAS precharge time                         | tap          | 30                        | _       | 35   | _        | 40                                                          | _          | ns   |         |

| RAS pulse width                            | TRAS         | 40                        | 10,000  | 45   | 10,000   | 50                                                          | 10,000     | ns   |         |

| RAS pulse width (Fast page mode)           | trasp        | . 40                      | 100,000 | 45   | 100,000  | 50                                                          | 100,000    | ns   |         |

| RAS hold time                              | tasa         | 8                         | _       | 10   |          | 10                                                          | _          | ns   |         |

| RAS hold time reference to OE              | tвон         | 8                         | _       | - 8  | _        | 10                                                          | _          | ns   |         |

| CAS precharge time                         | <b>t</b> CP  | 5                         | _       | 6    | _        | 7                                                           | _          | ns   |         |

| CAS pulse width                            | tcas         | 6                         | 10,000  | 7    | 10,000   | 8                                                           | 10,000     | ns   |         |

| CAS hold time                              | tсsн         | 40                        | _       | 45   |          | 50                                                          | _          | ns   |         |

| CAS to RAS precharge time                  | tcrp         | 5                         | _       | 5    | •••      | 5                                                           | . <b>–</b> | ns   |         |

| RAS to CAS delay time                      | trco         | 18                        | 30      | 18   | 33       | 20                                                          | 38         | ns   | 12      |

| RAS to column address delay time           | trad         | 13                        | 18      | 13   | 21       | 15                                                          | 24         | ns   |         |

| Row address set-up time                    | tasa         | 0                         | _       | 0    | _        | 0                                                           |            | ns   | 13      |

| Row address hold time                      | trah         | 8                         |         | 8    | _        | 10                                                          |            | ns   |         |

| Column address set-up time                 | tasc         | 0                         | _       | 0    | -        | 0                                                           |            | ns   |         |

| Column address hold time                   | tcah         | 5                         | _       | 6    | _        | 8                                                           | _          | ns   |         |

| Column address hold time from RAS          | <b>t</b> ar  | 30                        | _       | 30   | -        | 35                                                          |            | ns   |         |

| Column address to RAS lead time            | TRAL         | 22                        | _       | 24   |          | 26                                                          | _          | ns   |         |

| Read command set-up time                   | trics        | 0                         |         | 0    | _        | 0                                                           | _          | ns   |         |

| Read command hold time                     | tach         | 0                         | - 1     | 0    | -        | 0                                                           |            | ns   | 9       |

| Read command hold time reference to RAS    | trrh         | 0                         | -       | 0    | <u>-</u> | 0                                                           | _          | ns   | 9       |

| WE pulse width                             | twep         | 10                        |         | 10   |          | 10                                                          | _          | ns   |         |

## AC CHARACTERISTICS (2/2)

$(Vcc = 3.3V \pm 0.3V, Ta = 0 \sim 70^{\circ}C)$

| Parameter                                           | Symbol   | MSM54V16<br>Symbol B/BSL-40 |          | MSM54<br>B/BS | V16258<br>L-45 |     | 4V16258<br>SL-50 | Unit | Note  |

|-----------------------------------------------------|----------|-----------------------------|----------|---------------|----------------|-----|------------------|------|-------|

|                                                     | Joynnbor | MIN                         | MAX      | MIN           | MAX            | MIN | MAX              | 1    | 11010 |

| Write command set-up time                           | twcs     | 0                           |          | 0             | _              | 0   | _                | ns   |       |

| Write command hold time                             | twch     | 7                           | _        | 8             | _              | 9   | _                | ns   |       |

| Write command pulse width                           | twp      | 7                           | _        | 8             | _              | 9   | -                | ns   |       |

| Write command hold time from RAS                    | twcn     | 30                          | _        | 30            | _              | 35  |                  | ns   |       |

| OE command hold time                                | toeh     | 7                           |          | - 8           |                | 9   |                  | ns   |       |

| Write command to CAS lead time                      | tcwL     | 7                           | _        | 8             |                | 9   | _                | ns   |       |

| Write command to RAS lead time                      | trwL     | 8                           | -        | 12            | _              | 14  | _                | ns   |       |

| Data to CAS delay time                              | tozc     | 0                           | _        | 0             | _              | 0   | _                | ns   |       |

| Data to BE/OE delay time                            | tozo     | 0                           | _        | 0             | _              | 0   | _                | ns   |       |

| Data-in set-up time                                 | tos      | 0                           |          | 0             |                | 0   |                  | ns   | 10    |

| Data-in hold time                                   | tрн      | 6                           | _        | 7             | -              | 8   |                  | ns   | 10    |

| Data-in hold time referenced to RAS                 | tohr     | 30                          | _        | 30            |                | 35  |                  | ns   |       |

| OE to Data delay time                               | toed     | 8                           |          | 8             | _              | 8   |                  | กร   |       |

| OE "L" to CAS "H" lead time                         | tосн     | 10                          | _        | 10            | -              | 10  | _                | ns   |       |

| CAS "H" to OE "L" lead time                         | tсно     | 10                          | _        | 10            | _              | 10  | _                | ns   |       |

| Hi-Z command pulse width                            | toep     | 10                          | _        | 10            | _              | 10  | _                | ns   |       |

| CAS to WE delay time                                | tcwn     | 28                          | <b>_</b> | 30            | _              | 32  | _                | ns   | 11    |

| Column address to WE delay time                     | tawd     | 38                          | _        | 40            | _              | 44  | _                | ns   | 11    |

| RAS to WE delay time                                | trwd     | <b>5</b> 5                  |          | 60            | _              | 65  | -                | ns   | 11    |

| CAS active delay time from RAS precharge            | tnpc     | 0                           | . –      | 0             | _              | 0   | _                | ns   |       |

| RAS to CAS set-up time (CAS before RAS)             | tcsR     | 10                          | _        | 10            | _              | 10  | _                | ns   |       |

| RAS to CAS hold time<br>(CAS before RAS)            | tсня     | 10                          | -:.      | . 10          |                | 10  |                  | ns   |       |

| RAS pulse width<br>(CAS before RAS self-refresh)    | trass    | 100                         | _        | 100           |                | 100 |                  | us   | 19    |

| RAS precharge time<br>(CAS before RAS self-refresh) | taps     | 100                         | -        | 100           |                | 100 | _                | ns   | 19    |

| CAS hold time<br>(CAS before RAS self-refresh)      | tcus     | -40                         | _        | -40           | _              | -40 |                  | ns   | 19    |

#### Notes:

- 1. All voltages are referenced to Vss.

- 2. This parameter is dependent upon the cycle rate.

- 3. This parameter is dependent upon the output loading. Specified values are obtained with the output open.

- 4. An initial pause of 200 μs is required after power-up, followed by any 8RAS cycles. (Example: RAS-only-refresh) before proper device operation is achieved. In case of using internal refresh counter, a minimum of 8CAS before RAS cycles instead of 8RAS cycles are required.

- 5. The AC characteristics assume tr=5ns.

- 6. Vih (Min.) and Vil. (Max.) are reference levels for measuring timing of input signals. Also, transition times are measured between V iii and Vii.

- Data outputs are measured with a load of 30 pF.

DOUT reference levels: VoH/VoL=1.8V/1.4V.

- 8. trez (Max.), toff (Max.), twez (Max.) and toez (Max.) define the time at which the outputs achieve the open circuit condition and are not referebced to output voltage levels.

This parameter is sampled and not 100 % tested.

- 9. Either tren or trrn must be satisfied for a read cycle.

- 10. These parameters are referenced to CAS leading edge of early write cycles and to WE leading edge in OE-controlled write cycles and read-modify-write cycles.

- 11. twos, txwb, tcwb and tawb are not restrictive operating parameters. They are included in the data sheet as electrical characteristics only. If twos≥twos (Min.), the cycle is an early write cycle and the data out pins will remain open circuit throughout the entire cycle.

If txwb≥txwb (Min.), tcwb≥tcwb (Min.) and tawb≥tawb (Min.), the cycle is a read-modify-write cycle and the data out will contain data read from the selected cell. If neither or the above sets of conditions is satisfied, the condition of the data out is indetermunate.

- 12. Operation within the trop (Max.) limit insures that trac (Max.) can be met. trop (Max.) is specified as a reference point only. If trop is greater than the specified trop (Max.) limit, then access time is controlled by topo.

- 13. Operation within the trad (Max.) limit ensures that trac (Max.) can be met. trad (Max.) is specified as a reference point only: If trad is greater than the specified trad (Max.) limit, then access time is controlled by trad.

- 14. Input levels at the AC testing are 3.0V/0V.

- 15. Addresses (A0 A8) may be changed two times or less while RAS = V II.

- 16. Addresses (A0 A8) may be changed once or less while  $\overline{CAS} = V$  III and  $\overline{RAS} = VIII.$

- 17. This is guaranteed by design. ( toon=toac output transition time). This parameter is not 100 % tested.

- 18. This parameter is dependent upon the number of address transitions. Specified values are measured with a maximum of two transitions per address cycle in Fast Page Mode.

- 19. SL version.

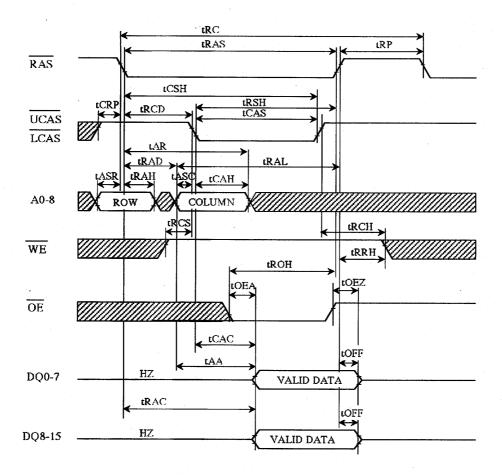

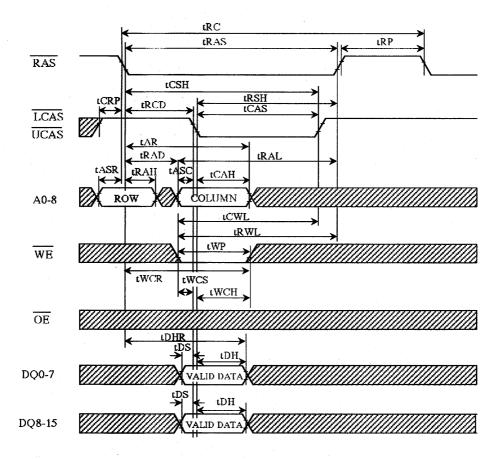

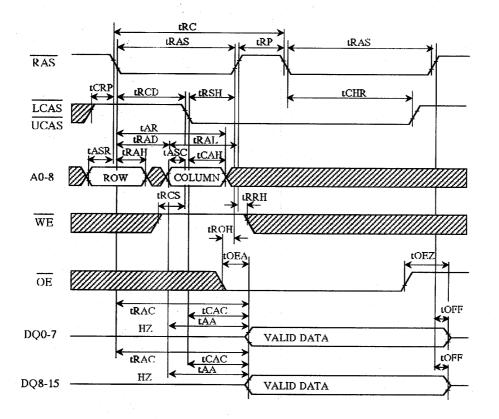

## READ CYCLE (RAS output control)

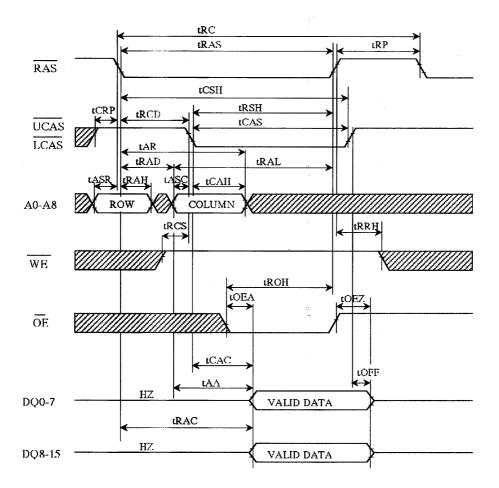

## READ CYCLE (CAS output control)

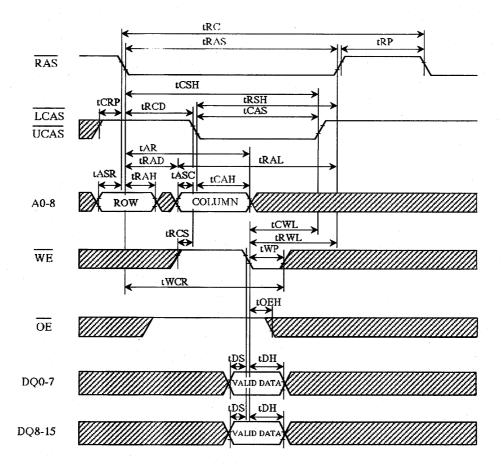

## EARLY WRITE CYCLE (LCAS and UCAS active)

## LATE WRITE CYCLE (LCAS and UCAS active)

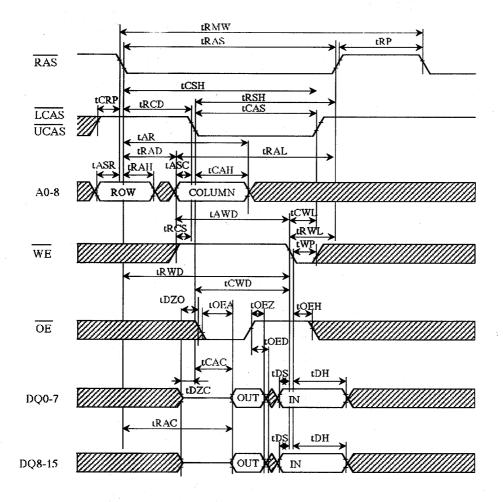

## READ MODIFY WRITE CYCLE (LCAS and UCAS active)

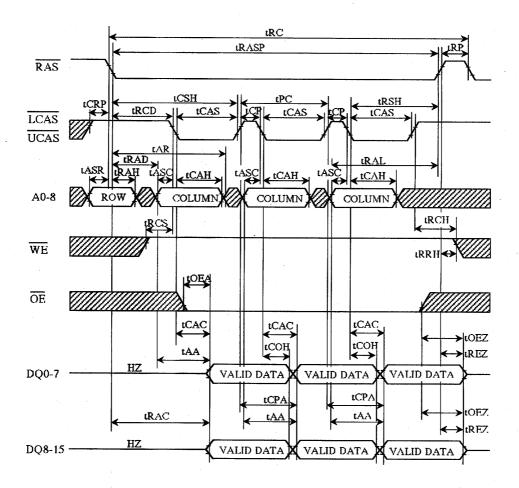

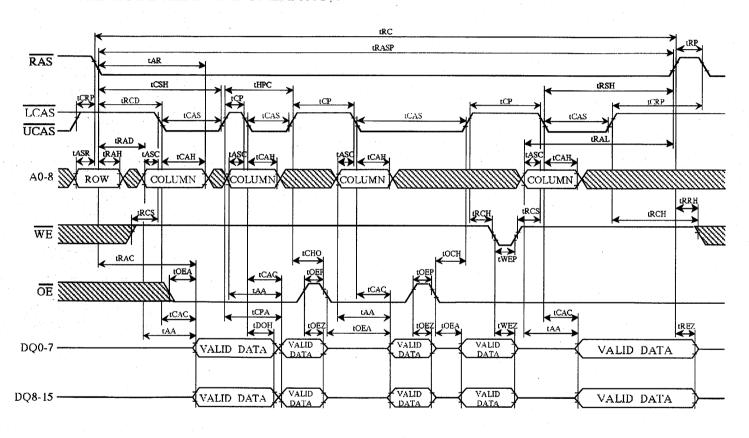

### **FAST PAGE MODE READ CYCLE with Extended Data Out**

### **FAST PAGE MODE READ HI-Z OPERATION**

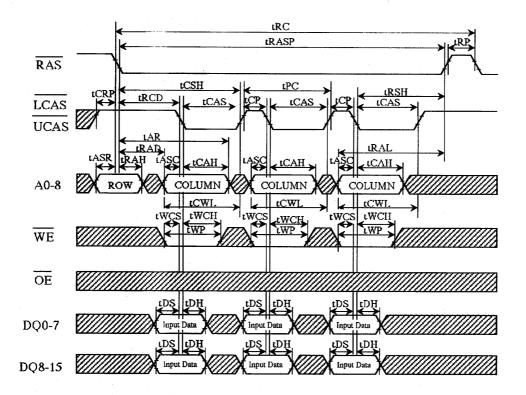

### **FAST PAGE MODE EARLY WRITE CYCLE**

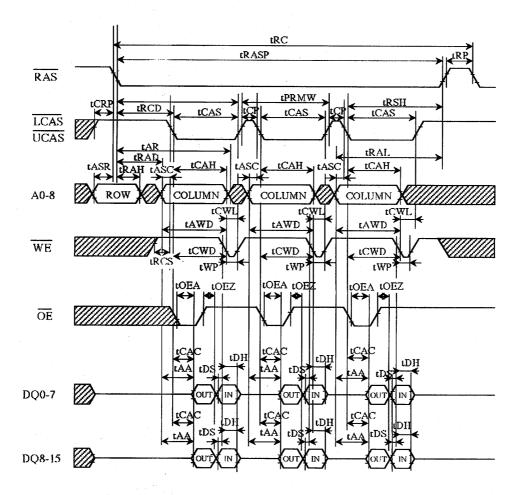

### **FAST PAGE MODE READ MODIFY WRITE CYCLE**

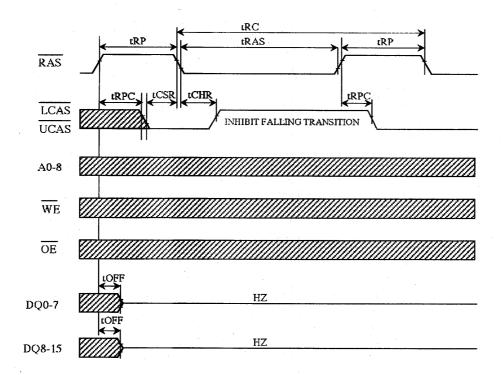

### CAS BEFORE RAS REFRESH CYCLE

### HIDDEN REFRESH CYCLE

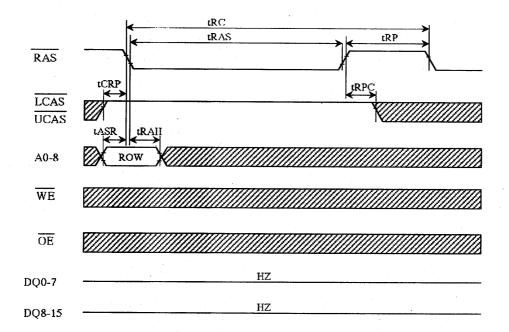

### **RAS ONLY REFRESH CYCLE**

$\qquad \qquad : \ ^{"}\!H" \ \text{or} \ ^{"}\!L" \\$

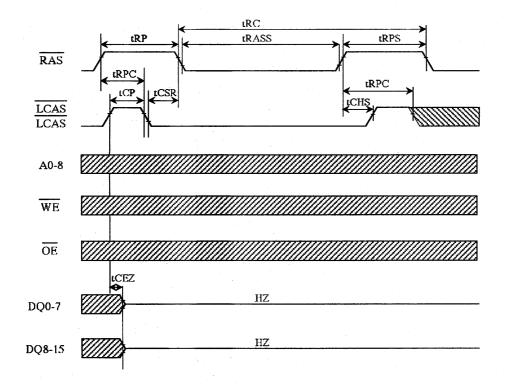

## CAS BEFORE RAS SELFREFRESH CYCLE

: "H" or "L"

NOTE: SL version.