# LAPIS Semiconductor ML9212

#### 32-Bit Duplex/Triplex (1/2 duty / 1/3 duty) VF Controller/Driver with Digital Dimming

# **GENERAL DESCRIPTION**

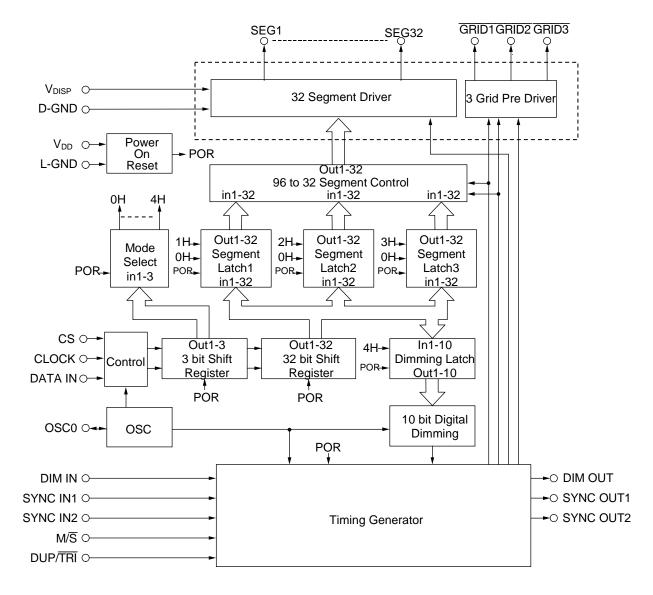

The ML9212 is a full CMOS controller/driver for Duplex or Triplex (1/2 duty or 1/3 duty) vacuum fluorescent display tube. It consists of a 32-segment driver multiplexed to drive up to 96 segments, and 10-bit digital dimming circuit.

ML9212 features a selection of a master mode and a slave mode, and therefore it can be used to expand segments for the VFD driver with keyscan and A/D converter function.

ML9212 provides an interface with a microcontroller only by three signal lines: DATA IN, CLOCK and CS.

# FEATURES

- Logic supply voltage (V<sub>DD</sub>) : 4.5 to 5.5 V • Driver supply voltage ( $V_{DISP}$ ) : 8 to 18 V • Duplex/Triplex (1/2 duty / 1/3 duty) selectable  $DUP/\overline{TRI} = 1/2$  duty selectable at "H" level  $DUP/\overline{TRI} = 1/3$  duty selectable at "L" level • Number of display segments Max. 64-segment display (during 1/2 duty mode) Max. 96-segment display (during 1/3 duty mode) • Master/Slave selectable  $M/\overline{S}$  = Master mode selectable at "H" level  $M/\overline{S}$  = Slave mode selectable at "L" level • Interface with a microcontroller Three lines: CS, CLOCK, and DATA IN • 32-segment driver outputs :  $I_{OH} = -5$  mA at  $V_{OH} = V_{DISP}$ -0.8 V (SEG1 to 22) (can be directly connected to VFD tube :  $I_{OH} = -10$  mA at  $V_{OH} = V_{DISP} - 0.8V$  (SEG23 to 32) :  $I_{OL} = 500 \ \mu A$  at  $V_{OL} = 2 \ V$  (SEG1 to 32) and require no external resisters) • 3-grid pre-driver outputs :  $I_{OH} = -5.0$  mA at  $V_{OH} = V_{DISP} - 0.8$  V (require external drivers)  $I_{OL} = 10 \text{ mA}$  at  $V_{OL} = 2 \text{ V}$ • Logic outputs :  $I_{OH}$  = –200  $\mu A$  at  $V_{OH}$  =  $V_{DD}$ –0.8 V  $I_{OL} = 200 \ \mu A$  at  $V_{OL} = 0.8 \ V$ • Built-in digital dimming circuit (10-bit resolution)

- Built-in oscillation circuit (external R and C)

Built-in Power-On-Reset circuit

- Package options:

- 56-pin plastic QFP (QFP56-P-910-0.65-2K)(ML9212GA)

# **BLOCK DIAGRAM**

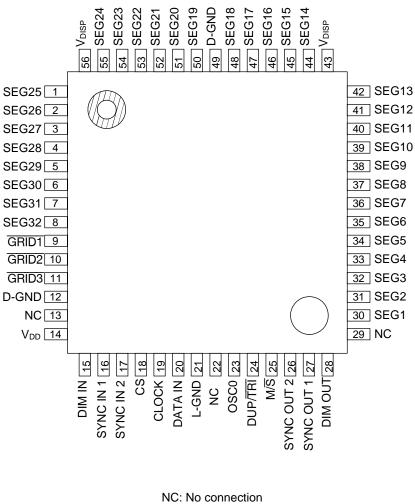

# PIN CONFIGURATION (TOP VIEW)

# **PIN DESCRIPTIONS**

| Symbol            | Pin                                | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------------------|------------------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>DISP</sub> | 43, 56                             | _    | Power supply pins for VFD driver circuit.<br>43 pin and 56 pin should be connected externally.                                                                                                                                                                                                                                                                                                                                                                                            |

| V <sub>DD</sub>   | 14                                 | _    | Power supply pin for logic drive.                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| D-GND             | 12, 49                             | _    | D-GND is ground pin for the VFD driver circuit. L-GND is ground pin                                                                                                                                                                                                                                                                                                                                                                                                                       |

| L-GND             | 21                                 | _    | for the logic circuit. 12 pin, 21 pin and 49 pin should be connected externally.                                                                                                                                                                                                                                                                                                                                                                                                          |

| SEG1 to 22        | 30 to 42,<br>44 to 48,<br>50 to 53 | 0    | Segment (anode) signal output pins for a VFD tube.<br>These pins can be directly connected to the VFD tube.<br>External circuit is not required.<br>$I_{OHL} \le -5$ mA                                                                                                                                                                                                                                                                                                                   |

| SEG23 to 32       | 1 to 8,<br>54, 55                  | 0    | Segment (anode) signal output pins for a VFD tube.<br>These pins can be directly connected to the VFD tube.<br>External circuit is not required.<br>$I_{OHL} \le -10$ mA                                                                                                                                                                                                                                                                                                                  |

| GRID1 to 3        | 9, 10, 11                          | ο    | Inverted Grid signal output pins. For pre-driver, the external circuit is required.<br>$I_{OL} \le 10 \text{ mA}$                                                                                                                                                                                                                                                                                                                                                                         |

| CS                | 18                                 | I    | Chip select input pin.<br>Data is not transferred when CS is set to a Low level.                                                                                                                                                                                                                                                                                                                                                                                                          |

| CLOCK             | 19                                 | I    | Shift clock input pin.<br>Serial data shifts at the rising edge of the CLOCK.                                                                                                                                                                                                                                                                                                                                                                                                             |

| DATA IN           | 20                                 | I    | Serial data input pin (positive logic).<br>Data is input to the shift register at the rising edge of the CLOCK<br>signal.                                                                                                                                                                                                                                                                                                                                                                 |

| DUP/TRI           | 24                                 | I    | Duplex/Triplex operation select input pin.<br>Duplex (1/2 duty) operation is selected when this pin is set to $V_{DD}$ .<br>Triplex (1/3 duty) operation is selected when this pin is set to L-GND.                                                                                                                                                                                                                                                                                       |

| M/S               | 25                                 | I    | Master/Slave mode select input pin.<br>Master mode is selected when this pin is set to V <sub>DD</sub> .<br>Slave mode is selected when this pin is set to L-GND.                                                                                                                                                                                                                                                                                                                         |

| DIM IN            | 15                                 | I    | Dimming pulse input.<br>When the slave mode is selected, the pulse width of the all segment<br>output are controlled by a input pulse width of DIM IN.<br>Connect this pin to the master side DIM OUT pin at the slave mode.<br>When the master mode is selected, the input level of this pin is<br>ignored and the pulse width of the all grids and segment outputs are<br>controlled by a built-in 10-bit dimming circuit.<br>Connect this pin to $V_{DD}$ or L-GND at the master mode. |

| Symbol           | Pin      | Туре | Description                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |  |

|------------------|----------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| SYNC IN 1, 2     | 16, 17   | 1    | Synchronous signal input.<br>When the slave mode is selected, connect these pins to the master side SYNC OUT 1, and 2 pins.<br>When the master mode is selected, the input level of these pins are ignored. Connect these pins to $V_{DD}$ or L-GND at the master mode. |  |  |  |  |  |  |  |  |

| DIM OUT          | 28       | 0    | Dimming pulse output.<br>Connect this pin to the slave side DIM IN pin.                                                                                                                                                                                                 |  |  |  |  |  |  |  |  |

| SYNC OUT<br>1, 2 | 26, 27   | 0    | Synchronous signal output.<br>Connect these pins to the slave side SYNC IN 1, and 2 pins.                                                                                                                                                                               |  |  |  |  |  |  |  |  |

| OSC0             | 23       | I/O  | RC oscillator connecting pins.<br>Oscillation frequency depends<br>on display tubes to be used.<br>For details refer to ELECTRICAL CHARACTERISTICS.                                                                                                                     |  |  |  |  |  |  |  |  |

| NC               | 13,22,29 | -    | OPEN pins.                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |  |

# ABSOLUTE MAXIMUM RATING

| Parameter             | Symbol            | Condition                        | Ratings                      | Unit |

|-----------------------|-------------------|----------------------------------|------------------------------|------|

| Driver Supply Voltage | V <sub>DISP</sub> | —                                | -0.3 to +20                  | V    |

| Logic Supply Voltage  | V <sub>DD</sub>   | —                                | -0.3 to +6.5                 | V    |

| Input Voltage         | V <sub>IN</sub>   | —                                | –0.3 to V <sub>DD</sub> +0.3 | V    |

| Power Dissipation     | PD                | Ta ≥ 105°C                       | 233                          | mW   |

| Storage Temperature   | T <sub>STG</sub>  | —                                | -55 to +150                  | °C   |

|                       | I <sub>o1</sub>   | SEG1 to 22                       | -10.0 to +2.0                | mA   |

|                       | I <sub>o2</sub>   | SEG23 to 32                      | -20.0 to +2.0                | mA   |

| Output Current        | I <sub>o3</sub>   | GRID1 to 3                       | -10.0 to +20.0               | mA   |

|                       | I <sub>04</sub>   | DIM OUT, SYNC OUT1,<br>SYNC OUT2 | -2.0 to +2.0                 | mA   |

# **RECOMMENDED OPERATING CONDITIONS**

| Parameter                | Symbol            | Condition              | Min.        | Тур. | Max.        | Unit |

|--------------------------|-------------------|------------------------|-------------|------|-------------|------|

| Driver Supply Voltage    | V <sub>DISP</sub> | —                      | 8.0         | 13.0 | 18.0        | V    |

| Logic Supply Voltage     | V <sub>DD</sub>   | —                      | 4.5         | 5.0  | 5.5         | V    |

| High Level Input Voltage | V <sub>IH</sub>   | All inputs except OSC0 | $0.8V_{DD}$ | —    | —           | V    |

| Low Level Input Voltage  | VIL               | All inputs except OSC0 | —           | —    | $0.2V_{DD}$ | V    |

| Clock Frequency          | f <sub>C</sub>    | —                      | —           | —    | 2.0         | MHz  |

# LAPIS Semiconductor

## ML9212

| Parameter             | Symbol           | Conditi                | on       | Min | Тур. | Max. | Unit |  |

|-----------------------|------------------|------------------------|----------|-----|------|------|------|--|

| Oscillation Frequency | f <sub>osc</sub> | R = 10 kΩ<br>C = 27 pF | ,        | 2.2 | 3.3  | 4.4  | MHz  |  |

|                       | ¢                | R = 10 kΩ±5%,          | 1/3 duty | 179 | 269  | 358  |      |  |

| Frame Frequency       | t <sub>FR</sub>  | C = 27 pF±5%           | 1/2 duty | 268 | Hz   |      |      |  |

| Operating Temperature | T <sub>OP</sub>  | _                      |          | -40 | _    | +105 | °C   |  |

# **ELECTRICAL CHARACTERISTICS**

## **DC** Characteristics

| $Ia = -40 \text{ to } +105^{\circ}\text{C}, V_{\text{DISP}} = 8.0 \text{ to } 18.0 \text{ V}, V_{\text{DD}} = 4.5 \text{ to } 5.5 \text{ V}$ |                   |                   |                          |                            |                         |             |      |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-------------------|--------------------------|----------------------------|-------------------------|-------------|------|--|--|--|--|

| Parameter                                                                                                                                    | Symbol            | Applied pin       | Co                       | ondition                   | Min.                    | Max.        | Unit |  |  |  |  |

| High Level Input Voltage                                                                                                                     | VIH               | *1)               |                          | —                          | $0.8V_{DD}$             | —           | V    |  |  |  |  |

| Low Level Input Voltage                                                                                                                      | VIL               | *1)               |                          | _                          | —                       | $0.2V_{DD}$ | V    |  |  |  |  |

| High Level Input Current                                                                                                                     | Iн                | *1)               | V⊮                       | H = V <sub>DD</sub>        | -1.0                    | +1.0        | μA   |  |  |  |  |

| Low Level Input Current                                                                                                                      | I <sub>IL</sub>   | *1)               | VIL                      | = GND                      | -1.0                    | +1.0        | μA   |  |  |  |  |

|                                                                                                                                              | V <sub>OH1</sub>  | SEG1-22           |                          | I <sub>OH1</sub> = -5 mA   | $V_{\text{DISP}} - 0.8$ | —           | V    |  |  |  |  |

| High Level Output                                                                                                                            | V <sub>OH2</sub>  | SEG23-32          | V <sub>DISP</sub> = 9.5V | $I_{OH2} = -10 \text{ mA}$ | $V_{\text{DISP}} - 0.8$ | —           | V    |  |  |  |  |

| Voltage                                                                                                                                      | V <sub>OH3</sub>  | GRID1-3           |                          | I <sub>OH3</sub> = -5 mA   | $V_{\text{DISP}} - 0.8$ | —           | V    |  |  |  |  |

|                                                                                                                                              | V <sub>OH4</sub>  | *2)               | $V_{DD} = 4.5 V$         | I <sub>OH4</sub> = -200 μA | $V_{DD} - 0.8$          | —           | V    |  |  |  |  |

|                                                                                                                                              | V <sub>OL1</sub>  | SEG1-22           |                          | l <sub>OL1</sub> = 500 μA  | _                       | 2.0         | V    |  |  |  |  |

| Low Level Output                                                                                                                             | V <sub>OL2</sub>  | SEG23-32          | VDISP = 9.5V             | I <sub>OL2</sub> = 500 μA  | _                       | 2.0         | V    |  |  |  |  |

| Voltage                                                                                                                                      | V <sub>OL3</sub>  | GRID1-3           |                          | I <sub>OL3</sub> = 10 mA   | _                       | 2.0         | V    |  |  |  |  |

|                                                                                                                                              | V <sub>OL4</sub>  | *2)               | $V_{DD} = 4.5 V$         | I <sub>OL4</sub> = 200 μA  | —                       | 0.8         | V    |  |  |  |  |

|                                                                                                                                              | I <sub>DISP</sub> | V <sub>DISP</sub> | R = 1                    | 0 kΩ±5%,                   |                         | 100         | uA   |  |  |  |  |

| Supply Current                                                                                                                               | I <sub>DD</sub>   | V <sub>DD</sub>   |                          | 27 pF±5%<br>p load         | _                       | 5.0         | mA   |  |  |  |  |

# Ta = -40 to +105°C, V<sub>DISP</sub> = 8.0 to 18.0 V, V<sub>DD</sub> = 4.5 to 5.5 V

\*1) CS, CLOCK, DATA IN, DIM IN, SYNC IN 1, SYNC IN 2, M/S, DUP/TRI \*2) DIM OUT, SYNC OUT 1, SYNC OUT 2

## LAPIS Semiconductor

# ML9212

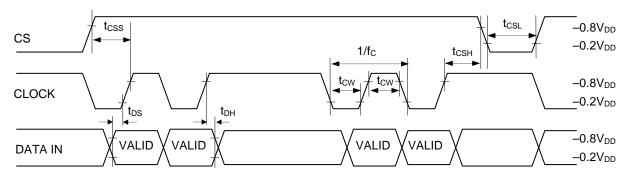

## **AC Characteristics**

| $Ta = -40.00 + 103.00$ , $V_{DISP} = 8.0.00 + 103.00$ , $V_{DD} = 4.3.00 + 3.00$ |                    |                          |                                   |      |      |      |  |  |  |

|----------------------------------------------------------------------------------|--------------------|--------------------------|-----------------------------------|------|------|------|--|--|--|

| Parameter                                                                        | Symbol             |                          | Condition                         | Min. | Max. | Unit |  |  |  |

| Clock Frequency                                                                  | f <sub>C</sub>     |                          | —                                 | —    | 2.0  | MHz  |  |  |  |

| Clock Pulse Width                                                                | t <sub>CW</sub>    |                          | —                                 | 200  | —    | ns   |  |  |  |

| Data Setup Time                                                                  | t <sub>DS</sub>    |                          | —                                 | 200  | —    | ns   |  |  |  |

| Data Hold Time                                                                   | t <sub>DH</sub>    |                          | —                                 | 200  | _    | ns   |  |  |  |

| CS Off Time                                                                      | t <sub>CSL</sub>   |                          | —                                 | 20   | _    | μS   |  |  |  |

| CS Setup Time<br>(CS-Clock)                                                      | t <sub>CSS</sub>   |                          | _                                 | 200  | —    | ns   |  |  |  |

| CS Hold Time<br>(Clock-CS)                                                       | t <sub>CSH</sub>   |                          | _                                 | 200  | —    | ns   |  |  |  |

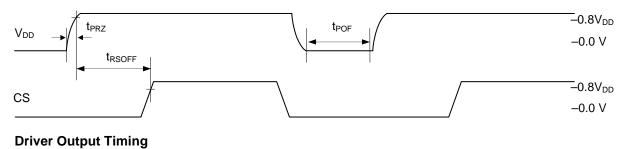

| CS Wait Time                                                                     | t <sub>RSOFF</sub> |                          | —                                 | 400  | —    | ns   |  |  |  |

| Output Slew Rate Time                                                            | t <sub>R</sub>     | C <sub>L</sub> = 100 pF  | t <sub>R</sub> = 20% to 80%       | —    | 2.0  | μS   |  |  |  |

|                                                                                  | t <sub>F</sub>     | $C_{L} = 100 \text{ pr}$ | t <sub>F</sub> = 80% to 20%       | —    | 2.0  | μS   |  |  |  |

| V <sub>DD</sub> Rise Time                                                        | t <sub>PRZ</sub>   | Mou                      | inted in a unit                   | _    | 100  | μS   |  |  |  |

| V <sub>DD</sub> Off Time                                                         | t <sub>POF</sub>   | Mounted in               | n a unit, V <sub>DD</sub> = 0.0 V | 5.0  | _    | ms   |  |  |  |

## Ta = -40 to +105°C, V<sub>DISP</sub> = 8.0 to 18.0 V, V<sub>DD</sub> = 4.5 to 5.5 V

# TIMING DIAGRAM

# **Data Input Timing**

# **Reset Timing**

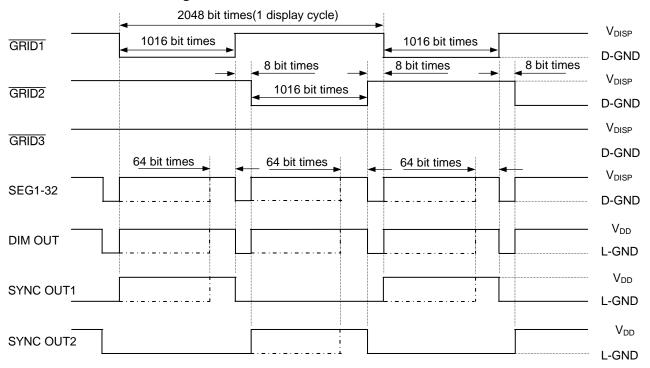

#### Output Timing (Duplex Operation) \*1bit time = 4/f<sub>OSC</sub> Solid line : The dimming data is 1016/1024 at the master mode Dotted line : The dimming data is 64/1024 at the master mode

## Output Timing (Triplex Operation) \*1bit time = 4/f<sub>OSC</sub> Solid line : The dimming data is 1016/1024 at the master mode Dotted line : The dimming data is 64/1024 at the master mode

|              | 3072 bit times(1 display cycle)                                            |                            |

|--------------|----------------------------------------------------------------------------|----------------------------|

| GRID1        | 1016 bit times<br>8 bit times<br>8 bit times<br>8 bit times<br>8 bit times | V <sub>DISP</sub><br>D-GND |

| GRID2        | 1016 bit times                                                             | V <sub>DISP</sub><br>D-GND |

| -<br>GRID3   | 64 bit times 64 bit times 64 bit times                                     | V <sub>DISP</sub><br>D-GND |

| -<br>SEG1-32 |                                                                            | V <sub>DISP</sub><br>D-GND |

| DIM OUT      |                                                                            | V <sub>DD</sub><br>L-GND   |

| SYNC OUT1    |                                                                            | V <sub>DD</sub><br>L-GND   |

| SYNC OUT2    |                                                                            | V <sub>DD</sub><br>L-GND   |

ML9212

# FUNCTIONAL DESCRIPTION

#### **Power-on Reset**

When power is turned on, ML9212 is initialized by the internal power-on reset circuit.

- The status of the internal circuit after initialization is as follows:

- The contents of the shift registers and latches are set to "0".

- The digital dimming duty cycle is set to "0".

- <u>All segment outputs are set to Low level.</u>

- $\overline{\mathsf{GRID1}}$  outputs are set to Low level.

- $\overline{\text{GRID2}}$  to  $\overline{3}$  outputs are set to High level.

#### **Data Transfer Method**

Data can be transferred between the rising edge and the next falling edge of chip select input.

The mode data, segment data and dimming data are written by a serial transfer method. The serial data is input to the shift register at the rising edge of a shift clock pulse.

The mode data (M0 to M2) must be transferred after the segment data and dimming data succeedingly.

When the chip select input falls, an internal LOAD signal is automatically generated and data is loaded to the latches.

#### **Function Mode**

Function mode is selected by the mode data (M0 to M2). The relation between function mode and mode data is as follows:

| FUNCTION MODE | OPERATING MODE                 | FUNCTION DATA                                                                                                                                                                                                    |   |   |  |  |  |

|---------------|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|--|--|--|

| FUNCTION MODE | OPERATING MODE                 | FUNCTION DATA           M0         M1         M2           0         0         0           1         0         0           0         1         0           1         1         0           1         1         0 |   |   |  |  |  |

| 0             | Segment Data for GRID1-3 Input | 0                                                                                                                                                                                                                | 0 | 0 |  |  |  |

| 1             | Segment Data for GRID1 Input   | 1                                                                                                                                                                                                                | 0 | 0 |  |  |  |

| 2             | Segment Data for GRID2 Input   | 0                                                                                                                                                                                                                | 1 | 0 |  |  |  |

| 3             | Segment Data for GRID3 Input   | 1                                                                                                                                                                                                                | 1 | 0 |  |  |  |

| 4             | Digital Dimming Data Input     | 0                                                                                                                                                                                                                | 0 | 1 |  |  |  |

#### Segment Data Input [Function Mode: 0 to 3]

- ML9212 receives the segment data when function mode 0 to 3 are selected.

- The same segment data is transferred to the 3 segment data latches corresponding to  $\overline{\text{GRID1}}$  to  $\overline{3}$  at the same time when the function mode 0 is selected.

- The segment data is transferred to only one segment data latch corresponding to the specified GRID when the function mode is 1, 2 or 3 is selected.

- Segment output (SEG1 to 32) becomes High level (lightning) when the segment data (S1 to S32) is set to "1".

[Data Format]

| Jinaej       |           |

|--------------|-----------|

| Input Data   | : 35 bits |

| Segment Data | : 32 bits |

| Mode Data    | : 3 bits  |

| _ | Bit                    | 1  | 2  | 3  | 4  |  | 29  | 30  | 31  | 32  | 33 | 34      | 35   |

|---|------------------------|----|----|----|----|--|-----|-----|-----|-----|----|---------|------|

|   | Input DATA             | S1 | S2 | S3 | S4 |  | S29 | S30 | S31 | S32 | MO | M1      | M2   |

|   | Segment Data (32 bits) |    |    |    |    |  |     |     |     |     |    | ode Dat | ta 🔶 |

#### LAPIS Semiconductor

ML9212

| SEG n        | 1   | 2   | 3   | 4   | 5   | 6   | 7   | 8   | 9   | 10  | 11  | 12  | 13  | 14  | 15  | 16  |

|--------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| Segment data | S1  | S2  | S3  | S4  | S5  | S6  | S7  | S8  | S9  | S10 | S11 | S12 | S13 | S14 | S15 | S16 |

| SEG n        | 17  | 18  | 19  | 20  | 21  | 22  | 23  | 24  | 25  | 26  | 27  | 28  | 29  | 30  | 31  | 32  |

| Segment data | S17 | S18 | S19 | S20 | S21 | S22 | S23 | S24 | S25 | S26 | S27 | S28 | S29 | S30 | S31 | S32 |

[Bit correspondence between segment output and segment data]

#### **Digital Dimming Data Input [Function Mode: 4]**

- ML9212 receives the digital dimming data when function mode 4 is selected.

- The output duty changes in the range of 0/1024 (0%) to 1016/1024 (99.2%) for each grid.

- The 10-bit digital dimming data is input from LSB.

[Data Format]

Input Data: 13 bitsDigital Dimming Data: 10 bitsMode Data: 3 bits

| Bit                         | 1  | 2  | 3  | 4  | 5  | 6  | 7  | 8      | 9  | 10  | 11 | 12 | 13 |

|-----------------------------|----|----|----|----|----|----|----|--------|----|-----|----|----|----|

| Input DATA                  | D1 | D2 | D3 | D4 | D5 | D6 | D7 | D8     | D9 | D10 | MO | M1 | M2 |

| LSB MSB Mode Data (10 bits) |    |    |    |    |    |    |    | ata —► |    |     |    |    |    |

```

(3 bits)

```

| (LSB)                                 | SB) Dimming Data (MSI |    |    |    |    |    | (MSB) |    |     |            |  |

|---------------------------------------|-----------------------|----|----|----|----|----|-------|----|-----|------------|--|

| D1                                    | D2                    | D3 | D4 | D5 | D6 | D7 | D8    | D9 | D10 | Duty Cycle |  |

| 0                                     | 0                     | 0  | 0  | 0  | 0  | 0  | 0     | 0  | 0   | 0/1024     |  |

| 1                                     | 0                     | 0  | 0  | 0  | 0  | 0  | 0     | 0  | 0   | 1/1024     |  |

| · · · · · · · · · · · · · · · · · · · |                       |    |    |    |    |    |       |    |     | :          |  |

| 1                                     | 1                     | 1  | 0  | 1  | 1  | 1  | 1     | 1  | 1   | 1015/1024  |  |

| 0                                     | 0                     | 0  | 1  | 1  | 1  | 1  | 1     | 1  | 1   | 1016/1024  |  |

| 1                                     | 0                     | 0  | 1  | 1  | 1  | 1  | 1     | 1  | 1   | 1016/1024  |  |

|                                       |                       |    | ÷  |    |    |    |       |    |     | :          |  |

| 1                                     | 1                     | 1  | 1  | 1  | 1  | 1  | 1     | 1  | 1   | 1016/1024  |  |

#### **Master Mode**

Master Mode is selected when  $M/\overline{S}$  pin is set at High level. The master mode operation is as follows:

- $\bullet$  The input levels of DIM IN, SYNC IN1 and SYNC IN2 are ignored, and these pins should be connected to L-GND or  $V_{\text{DD}}.$

- The pulse width of  $\overline{\text{GRID1}}$  to  $\overline{3}$  and SEG1 to 32 are controlled by the internal digital dimming circuit.

- The segment Latch1 to 3 corresponding to  $\overline{\text{GRID1}}$  to  $\overline{3}$  are selected by the internal timing generator.

### **Slave Mode**

Slave Mode is selected when  $M/\overline{S}$  pin is set at Low level. The slave mode operation is as follows:

- The internal dimming circuit is ignored.

- The pulse width of SEG1 to 32 are controlled by the pulse width of DIM IN signal.

- The segment Latch1 to 3 corresponding to  $\overline{\text{GRID1}}$  to  $\overline{3}$  are selected by SYNC IN1 and SYNC IN2 signals.

- The output levels of  $\overline{\text{GRID1}}$  to  $\overline{3}$  are set at High level. The output levels of DIM OUT, SYNC OUT1 and SYNC OUT2 are set at Low level.

[Correspondence between SYNC IN1, 2 and Segment Latch1 to 3]

[Correspondence between DIM IN and SEG1 to 32]

| SYNC IN 1 | SYNC IN 2 | Segment<br>Latch | GRID         |  |

|-----------|-----------|------------------|--------------|--|

| 0         | 0         | No               | No           |  |

| 1         | 0         | Latch1           | GRID1        |  |

| 0         | 1         | Latch2           | GRID2        |  |

| 1         | 1         | Latch3           | <b>GRID3</b> |  |

| DIM IN | SEG1 to 32 |  |  |  |  |

|--------|------------|--|--|--|--|

| 0      | Low        |  |  |  |  |

| 1      | High       |  |  |  |  |

|        |            |  |  |  |  |

Note: Low: Lights OFF High: Lights ON

# **APPLICATION CIRCUITS**

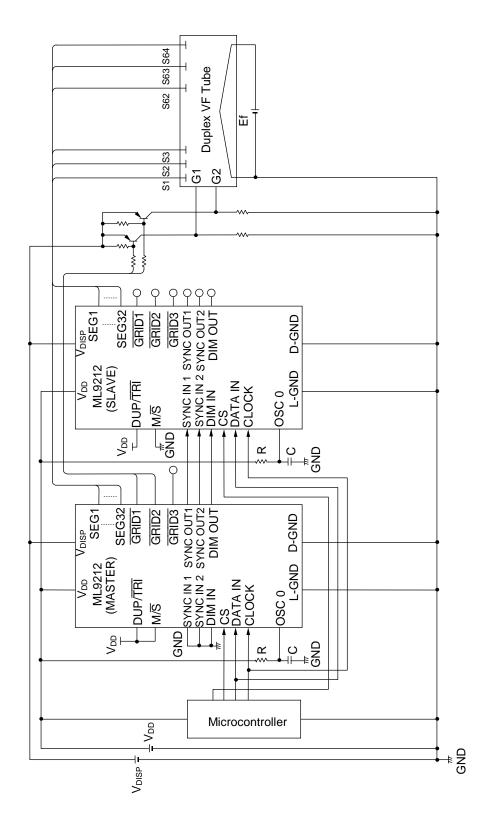

## 1. Circuit for the duplex VFD tube with 128 segments (2 Grid × 64 Anode)

# S63 S64 Triplex VF Tube S62 Ш S1 S2 S3 . 6 6 6⊦ q 9 99 SYNC IN 1 SYNC OUT1 SYNC IN 2 SYNC OUT2 DIM IN DIM OUT CS DATA IN CLOCK V<sub>DISP</sub> SEG1 SEG32 <u>GRID1</u> <u>GRID2</u> <u>GRID3</u> OSC 0 L-GND D-GND ML9212 (SLAVE) Vdd DUP/TRI <u>M/S</u> GŇD ບ ⊩⊢ <u>ک</u> GND≇ - - -V<sub>DISP</sub> SEG1 SYNC IN 1 SYNC OUT1 SYNC IN 2 SYNC OUT2 DIM IN DIM OUT CS DATA IN CLOCK SEG32 GRID2 <u>GRID3</u> **GRID1** D-GND V<sub>DD</sub> V ML9212 (MASTER) -OSC 0 L-GND DUP/TRI <u>M/S</u> GND V DD H GND ₿ ഺ C ╉╟ $\sim$ Microcontroller V<sub>DD</sub> ₿ND

# 2. Circuit for the triplex VFD tube with 192 segments (3 Grid × 64 Anode)

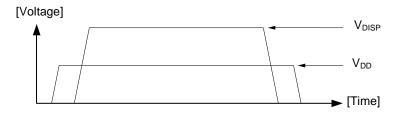

# NOTES ON TURNING POWER ON/OFF

- Connect L-GND and D-GND externally to be an equal potential voltage.

- To avoid wrong operations, turn on the driver power supply after turning on the logic power supply. Conversely, turn off the logic power supply after tuning off the driver power supply.

# **REVISION HISTORY**

|  | Document<br>No. |                | Pa                  | ge                 |                 |

|--|-----------------|----------------|---------------------|--------------------|-----------------|

|  |                 | Date           | Previous<br>Edition | Current<br>Edition | Description     |

|  | FEDL9212-01     | Nov., 26, 2002 | -                   | -                  | Final edition 1 |

#### NOTICE

No copying or reproduction of this document, in part or in whole, is permitted without the consent of LAPIS Semiconductor Co., Ltd.

The content specified herein is subject to change for improvement without notice.

The content specified herein is for the purpose of introducing LAPIS Semiconductor's products (hereinafter "Products"). If you wish to use any such Product, please be sure to refer to the specifications, which can be obtained from LAPIS Semiconductor upon request.

Examples of application circuits, circuit constants and any other information contained herein illustrate the standard usage and operations of the Products. The peripheral conditions must be taken into account when designing circuits for mass production.

Great care was taken in ensuring the accuracy of the information specified in this document. However, should you incur any damage arising from any inaccuracy or misprint of such information, LAPIS Semiconductor shall bear no responsibility for such damage.

The technical information specified herein is intended only to show the typical functions of and examples of application circuits for the Products. LAPIS Semiconductor does not grant you, explicitly or implicitly, any license to use or exercise intellectual property or other rights held by LAPIS Semiconductor and other parties. LAPIS Semiconductor shall bear no responsibility whatsoever for any dispute arising from the use of such technical information.

The Products specified in this document are intended to be used with general-use electronic equipment or devices (such as audio visual equipment, office-automation equipment, communication devices, electronic appliances and amusement devices).

The Products specified in this document are not designed to be radiation tolerant.

While LAPIS Semiconductor always makes efforts to enhance the quality and reliability of its Products, a Product may fail or malfunction for a variety of reasons.

Please be sure to implement in your equipment using the Products safety measures to guard against the possibility of physical injury, fire or any other damage caused in the event of the failure of any Product, such as derating, redundancy, fire control and fail-safe designs. LAPIS Semiconductor shall bear no responsibility whatsoever for your use of any Product outside of the prescribed scope or not in accordance with the instruction manual.

The Products are not designed or manufactured to be used with any equipment, device or system which requires an extremely high level of reliability the failure or malfunction of which may result in a direct threat to human life or create a risk of human injury (such as a medical instrument, transportation equipment, aerospace machinery, nuclear-reactor controller, fuel-controller or other safety device). LAPIS Semiconductor shall bear no responsibility in any way for use of any of the Products for the above special purposes. If a Product is intended to be used for any such special purpose, please contact a ROHM sales representative before purchasing.

If you intend to export or ship overseas any Product or technology specified herein that may be controlled under the Foreign Exchange and the Foreign Trade Law, you will be required to obtain a license or permit under the Law.

Copyright 2002 - 2011 LAPIS Semiconductor Co., Ltd.