# Universal Hexadecimal Counter

The MC10136 is a high speed synchronous counter that can count up, count down, preset, or stop count at frequencies exceeding 100 MHz. The flexibility of this device allows the designer to use one basic counter for most applications, and the synchronous count feature makes the MC10136 suitable for either computers or instrumentation.

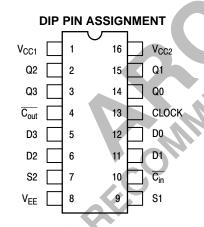

Three control lines (S1, S2, and Carry In) determine the operation mode of the counter. Lines S1 and S2 determine one of four operations; preset (program), increment (count up), decrement (count down), or hold (stop count). Note that in the preset mode a clock pulse is necessary to load the counter, and the information present on the data inputs (D0, D1, D2, and D3) will be entered into the counter. Carry Out goes low on the terminal count, or when the counter is being preset.

This device is not designed for use with gated clocks. Control is via S1 and S2.

- $P_D = 625 \text{ mW typ/pkg}$  (No Load)

- $f_{count} = 150 \text{ MHz typ}$

- $t_{pd} = 3.3 \text{ ns typ} (C-Q)$

- 7.0 ns typ (C-C<sub>out</sub>)

- 5.0 ns typ ( $\overline{C_{in}}$ - $C_{out}$ )

|     | FUNCTION TABLE |    |    |                        |  |  |  |  |  |

|-----|----------------|----|----|------------------------|--|--|--|--|--|

|     | <b>C</b> in    | S1 | S2 | Operating Mode         |  |  |  |  |  |

| DEN | X              | L  | L  | Preset (Program)       |  |  |  |  |  |

|     | L              | L  | Н  | Increment (Count Up)   |  |  |  |  |  |

|     | Н              | L  | Н  | Hold Count             |  |  |  |  |  |

|     | L              | Н  | L  | Decrement (Count Down) |  |  |  |  |  |

|     | Н              | Н  | L  | Hold Count             |  |  |  |  |  |

|     | Х              | Н  | Н  | Hold (Stop Count)      |  |  |  |  |  |

## **ON Semiconductor**

http://onsemi.com

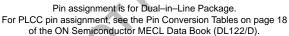

WL = Wafer Lot

YY = Year WW = Work Week

## ORDERING INFORMATION

| Device    | Package | Shipping        |  |  |  |  |

|-----------|---------|-----------------|--|--|--|--|

| MC10136L  | CDIP-16 | 25 Units / Rail |  |  |  |  |

| MC10136P  | PDIP-16 | 25 Units / Rail |  |  |  |  |

| MC10136FN | PLCC-20 | 46 Units / Rail |  |  |  |  |

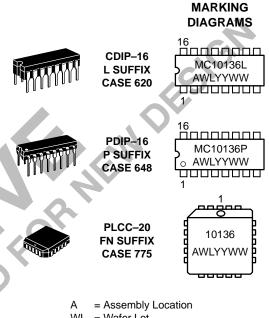

#### LOGIC DIAGRAM

**NOTE:** Flip-flops will toggle when all  $\overline{T}$  inputs are low.

# SEQUENTIAL TRUTH TABLE\*

| INPUTS |    |    |    |    |    |             | OUTPUTS |    |    |    |    |              |

|--------|----|----|----|----|----|-------------|---------|----|----|----|----|--------------|

| S1     | S2 | D0 | D1 | D2 | D3 | Carry<br>In | Clock   | Q0 | Q1 | Q2 | Q3 | Carry<br>Out |

| L      | L  | L  | Ч  | Н  | Н  | X           | Н       | L  | L  | Н  | Н  | L            |

| L      | н  | X  | X  | X  | X  | L           | Н       | н  | L  | н  | Н  | Н            |

| L      | н  | X  | X  | X  | X  | L           | Н       | L  | Н  | н  | Н  | Н            |

| L      | Н  | Х  | X  | X  | X  | L           | Н       | Н  | Н  | Н  | Н  | L            |

| L      | Н  | Х  | X  | Х  | X  | Н           | L       | Н  | Н  | Н  | Н  | Н            |

| L      | Н  | Х  | X  | X  | Х  | Н           | Н       | Н  | Н  | Н  | Н  | Н            |

| н      | Н  | Х  | Х  | X  | Х  | Х           | Н       | Н  | Н  | Н  | Н  | Н            |

| L      | L  | H  | H  | L  | L  | Х           | Н       | Н  | Н  | L  | L  | L            |

| Н      | L  | X  | Х  | Х  | Х  | L           | Н       | L  | Н  | L  | L  | Н            |

| Н      | L  | X  | X  | Х  | Х  | L           | Н       | Н  | L  | L  | L  | Н            |

| н      | L  | X  | Х  | Х  | Х  | L           | Н       | L  | L  | L  | L  | L            |

| Н      |    | X  | Х  | Х  | Х  | L           | Н       | Н  | Н  | Н  | Н  | Н            |

\* Truth table shows logic states assuming inputs vary in sequence shown from top to bottom.

\*\* A clock H is defined as a clock input transition from a low to a high logic level. DEMICE

#### **ELECTRICAL CHARACTERISTICS**

|                                                             |                                                                                        | Pin<br>Under                 | Test Limits              |                            |                          |                          |                            |                          |                            |      |

|-------------------------------------------------------------|----------------------------------------------------------------------------------------|------------------------------|--------------------------|----------------------------|--------------------------|--------------------------|----------------------------|--------------------------|----------------------------|------|

|                                                             |                                                                                        |                              | −30°C                    |                            | +25°C                    |                          |                            | +8                       |                            |      |

| Characteristic                                              | Symbol                                                                                 | Test                         | Min                      | Max                        | Min                      | Тур                      | Max                        | Min                      | Max                        | Unit |

| Power Supply Drain Current                                  | Ι <sub>Ε</sub>                                                                         | 8                            |                          | 138                        |                          | 100                      | 125                        |                          | 138                        | mAdc |

| Input Current                                               | l <sub>inH</sub>                                                                       | 5,6,11,12<br>7<br>9,10<br>13 |                          | 350<br>425<br>390<br>460   |                          |                          | 220<br>265<br>245<br>290   |                          | 220<br>265<br>245<br>290   | μAdc |

|                                                             | I <sub>inL</sub>                                                                       | All                          | 0.5                      |                            | 0.5                      |                          |                            | 0.3                      |                            | μAdc |

| Output Voltage Logic 1                                      | V <sub>OH</sub>                                                                        | 14 (2.)                      | -1.060                   | -0.890                     | -0.960                   |                          | -0.810                     | -0.890                   | -0.700                     | Vdc  |

| Output Voltage Logic 0                                      | V <sub>OL</sub>                                                                        | 14 (2.)                      | -1.890                   | -1.675                     | -1.850                   |                          | -1.650                     | -1.825                   | -1.615                     | Vdc  |

| Threshold Voltage Logic 1                                   | V <sub>OHA</sub>                                                                       | 14 (2.)                      | -1.080                   |                            | -0.980                   |                          |                            | -0.910                   |                            | Vdc  |

| Threshold Voltage Logic 0                                   | V <sub>OLA</sub>                                                                       | 14 (2.)                      |                          | -1.655                     |                          |                          | -1.630                     |                          | -1.595                     | Vdc  |

| Switching Times (50Ω Load)<br>Propagation Delay Clock Input | t <sub>13+14+</sub><br>t <sub>13+14-</sub><br>t <sub>13+4+</sub><br>t <sub>13+4-</sub> | 14<br>14<br>4<br>4           | 0.8<br>0.8<br>2.0<br>2.0 | 4.8<br>4.8<br>10.9<br>10.9 | 1.0<br>1.0<br>2.5<br>2.5 | 3.3<br>3.3<br>7.0<br>7.0 | 4.5<br>4.5<br>10.5<br>10.5 | 1.4<br>1.4<br>2.4<br>2.4 | 5.0<br>5.0<br>11.5<br>11.5 | ns   |

| Carry In to Carry Out                                       | t <sub>10–4–</sub><br>t <sub>10+4+</sub>                                               | 4 (3.)<br>4                  | 1.6<br>1.6               | 7.4<br>7.4                 | 1.6<br>1.6               | 5.0<br>5.0               | 6.9<br>6.9                 | 1.9<br>1.9               | 7.5<br>7.5                 |      |

| Setup Time Data Inputs                                      | t <sub>12+13+</sub><br>t <sub>12–13+</sub>                                             | 14<br>14                     | 3.5<br>3.5               |                            | 3.5<br>3.5               |                          |                            | 3.5<br>3.5               |                            |      |

| Select Inputs                                               | t <sub>9+13+</sub><br>t <sub>7+13+</sub>                                               | 14<br>14                     | 6.0<br>6.0               |                            | 6.0<br>6.0               | S'                       |                            | 6.0<br>6.0               |                            |      |

| Carry In Input                                              | t <sub>10–13+</sub><br>t <sub>10+13+</sub>                                             | 14<br>14                     | 2.5<br>1.5               |                            | 2.5<br>1.5               |                          |                            | 3.0<br>1.5               |                            |      |

| Hold Time Data Inputs                                       | t <sub>13+12+</sub><br>t <sub>13+12-</sub>                                             | 14<br>14                     | 0<br>0                   |                            | 0<br>0                   |                          |                            | 0<br>0                   |                            |      |

| Select Inputs                                               | t <sub>13+9+</sub><br>t <sub>13+7+</sub>                                               | 14<br>14                     | -1.0<br>-1.0             | S.                         | -1.0<br>-1.0             |                          |                            | -1.0<br>-1.0             |                            |      |

| Carry In Input                                              | t <sub>13+10</sub> –<br>t <sub>13+10+</sub>                                            | 14<br>14                     | 0<br>0                   |                            | 0<br>0                   |                          |                            | 0<br>0                   |                            |      |

| Counting Frequency                                          | f <sub>countup</sub><br>f <sub>countdown</sub>                                         | 14<br>14                     | 125<br>125               |                            | 125<br>125               | 150<br>150               |                            | 125<br>125               |                            | MHz  |

| Rise Time (20 to 80%)                                       | t <sub>4+</sub><br>t <sub>14+</sub>                                                    | 4<br>14                      | 0.9<br>0.9               | 3.3<br>3.3                 | 1.1<br>1.1               | 2.0<br>2.0               | 3.3<br>3.3                 | 1.1<br>1.1               | 3.5<br>3.5                 | ns   |

| Fall Time (20 to 80%)                                       | t <sub>4-</sub><br>t <sub>14-</sub>                                                    | 4<br>14                      | 0.9<br>0.9               | 3.3<br>3.3                 | 1.1<br>1.1               | 2.0<br>2.0               | 3.3<br>3.3                 | 1.1<br>1.1               | 3.5<br>3.5                 |      |

Individually test each input; apply V<sub>ILmin</sub> to pin under test.

Measure output after clock pulse V<sub>IL</sub> V<sub>IH</sub> appears at clock input (Pin 13).

Before test set all Q outputs to a logic high.

To preserve reliable performance, the MC10136 (plastic packaged device only) is to be operated in ambient temperatures above 70°C only when 500lfpm blown air or equivalent heat sinking is provided. DEVIC

#### ELECTRICAL CHARACTERISTICS (continued)

|                    |                    | @ Test Te                                      | mperature            | V <sub>IHmax</sub>                        | V <sub>ILmin</sub> | V <sub>IHAmin</sub> | V <sub>ILAmax</sub> | V <sub>EE</sub> |                           |  |

|--------------------|--------------------|------------------------------------------------|----------------------|-------------------------------------------|--------------------|---------------------|---------------------|-----------------|---------------------------|--|

|                    |                    |                                                | –30°C                | -0.890                                    | -1.890             | -1.205              | -1.500              | -5.2            |                           |  |

|                    |                    | +25°C                                          |                      | -0.810                                    | -1.850             | -1.105              | -1.475              | -5.2            |                           |  |

|                    |                    | +85°C                                          |                      | -0.700                                    | -1.825             | -1.035              | -1.440              | -5.2            |                           |  |

|                    |                    |                                                | Pin<br>Under<br>Test | TEST VOLTAGE APPLIED TO PINS LISTED BELOW |                    |                     |                     |                 |                           |  |

| Characte           | eristic            | Symbol                                         |                      | V <sub>IHmax</sub>                        | V <sub>ILmin</sub> | V <sub>IHAmin</sub> | V <sub>ILAmax</sub> | V <sub>EE</sub> | (V <sub>CC</sub> )<br>Gnd |  |

| Power Supply Drai  | n Current          | ١ <sub>E</sub>                                 | 8                    |                                           |                    |                     |                     | 8               | 1, 16                     |  |

| Input Current      |                    | I <sub>inH</sub>                               | 5,6,11,12            | 5,6,11,12                                 |                    |                     |                     | 8               | 1, 16                     |  |

|                    |                    |                                                | 7<br>9,10<br>13      | 7<br>9,10<br>13                           |                    |                     |                     | 8<br>8<br>8     | 1, 16<br>1, 16<br>1, 16   |  |

|                    |                    | l <sub>inL</sub>                               | All                  | 13                                        | Note 1.            |                     |                     | 8               | 1, 16                     |  |

| Output Voltage     | Logic 1            | V <sub>OH</sub>                                | 14 (2.)              | 12                                        | 7, 9               |                     |                     | 8               | 1, 16                     |  |

| Output Voltage     | Logic 0            | V <sub>OL</sub>                                | 14 (2.)              |                                           | 7, 9               |                     |                     | 8               | 1, 16                     |  |

| Threshold Voltage  | Logic 1            | V <sub>OHA</sub>                               | 14 (2.)              |                                           | 7, 9               | 12                  |                     | 8               | 1, 16                     |  |

| Threshold Voltage  | Logic 0            | V <sub>OLA</sub>                               | 14 (2.)              |                                           | 7, 9               |                     | 12                  | 8               | 1, 16                     |  |

| Switching Times    | (50 $\Omega$ Load) |                                                |                      | +1.11V                                    | +0.31V             | Pulse In            | Pulse Out           | –3.2 V          | +2.0 V                    |  |

| Propagation Delay  |                    | t <sub>13+14+</sub>                            | 14                   | 12                                        |                    | 13                  | 14                  | 8               | 1, 16                     |  |

|                    |                    | t <sub>13+14</sub>                             | 14                   | 7                                         |                    | 13                  | 14                  | 8               | 1, 16                     |  |

|                    |                    | t <sub>13+4+</sub><br>t <sub>13+4–</sub>       | 4<br>4               | 7<br>7                                    |                    | 13<br>13            | 4 4                 | 8<br>8          | 1, 16<br>1, 16            |  |

| Carry              | In to Carry Out    | t <sub>10-4-</sub><br>t <sub>10+4+</sub>       | 4 (3.)<br>4          | 777                                       | 13<br>13           | 10<br>10            | 4<br>4              | 8<br>8          | 1, 16<br>1, 16            |  |

| Setup Time         | Data Inputs        | t <sub>12+13+</sub><br>t <sub>12–13+</sub>     | 14<br>14             |                                           | 7, 9<br>7, 9       | 12, 13<br>12, 13    | 14<br>14            | 8<br>8          | 1, 16<br>1, 16            |  |

|                    | Select Inputs      | t <sub>9+13+</sub><br>t <sub>7+13+</sub>       | 14<br>14             |                                           |                    | 9, 13<br>7, 13      | 14<br>14            | 8<br>8          | 1, 16<br>1, 16            |  |

|                    | Carry In Inputs    | t <sub>10–13+</sub><br>t <sub>10+13+</sub>     | 14<br>14             | 7<br>7                                    | 9<br>9             | 10, 13<br>10, 13    | 14<br>14            | 8<br>8          | 1, 16<br>1, 16            |  |

| Hold Time          | Data Inputs        | t <sub>13+12+</sub><br>t <sub>13+12</sub> -    | 14<br>14             |                                           | 7, 9<br>7, 9       | 12, 13<br>12, 13    | 14<br>14            | 8<br>8          | 1, 16<br>1, 16            |  |

|                    | Select Inputs      | t <sub>13+9+</sub><br>t <sub>13+7+</sub>       | 14<br>14             |                                           |                    | 9, 13<br>7, 13      | 14<br>14            | 8<br>8          | 1, 16<br>1, 16            |  |

|                    | Carry In Inputs    | t <sub>13+10</sub> -<br>t <sub>13+10+</sub>    | 14<br>14             | 7<br>7                                    | 9                  | 10, 13<br>10, 13    | 14<br>14            | 8<br>8          | 1, 16<br>1, 16            |  |

| Counting Frequence | су                 | f <sub>countup</sub><br>f <sub>countdown</sub> | 14<br>14             | 7<br>9                                    |                    | 13<br>13            | 14<br>14            | 8<br>8          | 1, 16<br>1, 16            |  |

| Rise Time          | (20 to 80%)        | t <sub>4+</sub><br>t <sub>14+</sub>            | 4<br>14              | 7<br>7                                    |                    | 13<br>13            | 4<br>14             | 8<br>8          | 1, 16<br>1, 16            |  |

| Fall Time          | (20 to 80%)        | t <sub>4-</sub><br>t <sub>14-</sub>            | 4<br>14              | 7<br>7                                    |                    | 13<br>13            | 4<br>14             | 8<br>8          | 1, 16<br>1, 16            |  |

Individually test each input; apply V<sub>ILmin</sub> to pin under test.

Measure output after clock pulse VII ap

V<sub>IL</sub> V<sub>IH</sub> appears at clock input (Pin 13).

3. Before test set all Q outputs to a logic high.

4. To preserve reliable performance, the MC10136 (plastic packaged device only) is to be operated in ambient temperatures above 70°C only when 500lfpm blown air or equivalent heat sinking is provided.

Each MECL 10,000 series circuit has been designed to meet the dc specifications shown in the test table, after thermal equilibitum has been established. The circuit is in a test socket or mounted on a printed circuit board and transverse air flow greater than 500 linear fpm is maintained. Outputs are terminated through a 50-ohm resistor to -2.0 volts. Test procedures are shown for only one gate. The other gates are tested in the same manner.

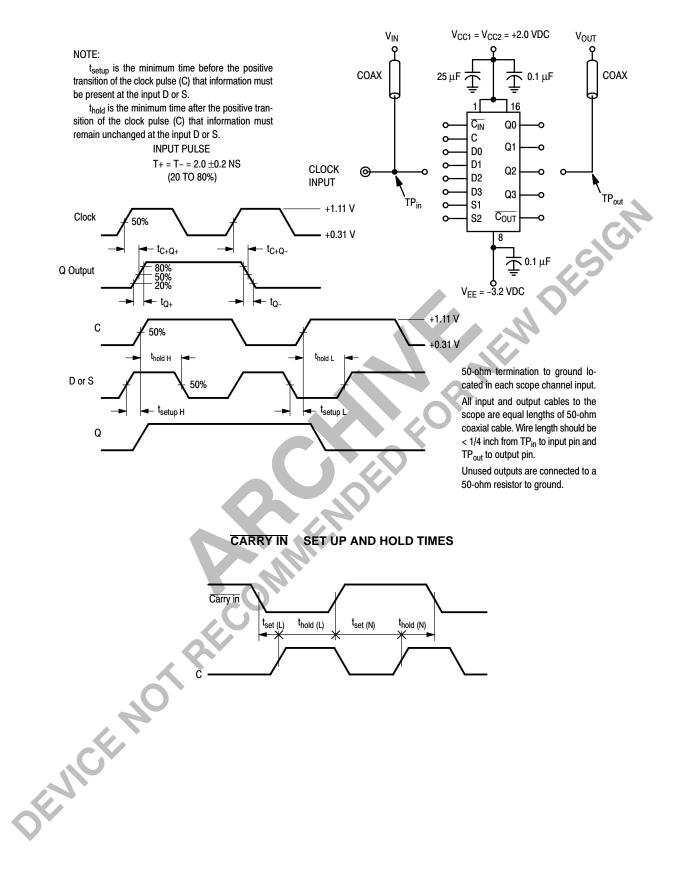

### SWITCHING TIME TEST CIRCUIT AND WAVEFORMS @ 25°C

#### **APPLICATIONS INFORMATION**

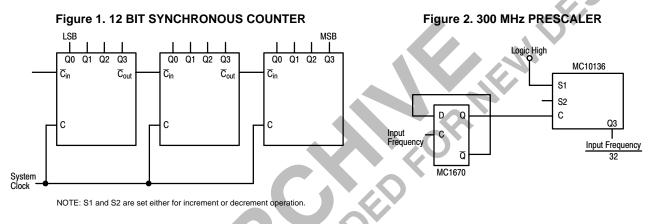

To provide more than four bits of counting capability several MC10136 counters may be cascaded. The Carry In input overrides the clock when the counter is either in the increment mode or the decrement mode of operation. This input allows several devices to be cascaded in a fully synchronous multistage counter as illustrated in Figure 1. The carry is advanced between stages as shown with no external gating. The Carry In of the first device may be left open. The system clock is common to all devices.

The various operational modes of the counter make it useful for a wide variety of applications. If used with MECL III devices, prescalers with input toggle frequencies in excess of 300 MHz are possible. Figure 2 shows such a prescaler using the MC10136 and MC1670. Use of the MC10231 in place of the MC1670 permits 200 MHz operation. The MC10136 may also be used as a programmable counter. The configuration of Figure 3 requires no additional gates, although maximum frequency is limited to about 50 MHz. The divider modulus is equal to the program input plus one (M = N + 1), therefore, the counter will divide by a modulus varying from 1 to 16.

A second programmable configuration is also illustrated in Figure 4. A pulse swallowing technique is used to speed the counter operation up to 110 MHz typically. The divider modulus for this figure is equal to the program input (M =N). The minimum modulus is 2 because of the pulse swallowing technique, and the modulus may vary from 2 to 15. This programmable configuration requires an additional gate, such as 1/2MC10109 and a flip-flop such as 1/2MC10131.

Figure 4. 100 MHz PROGRAMMABLE COUNTER

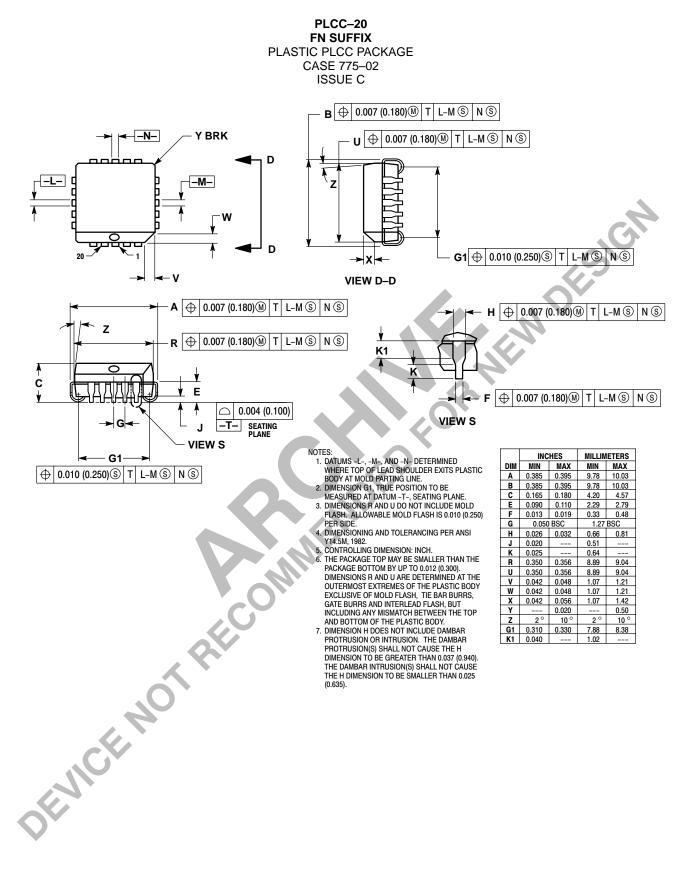

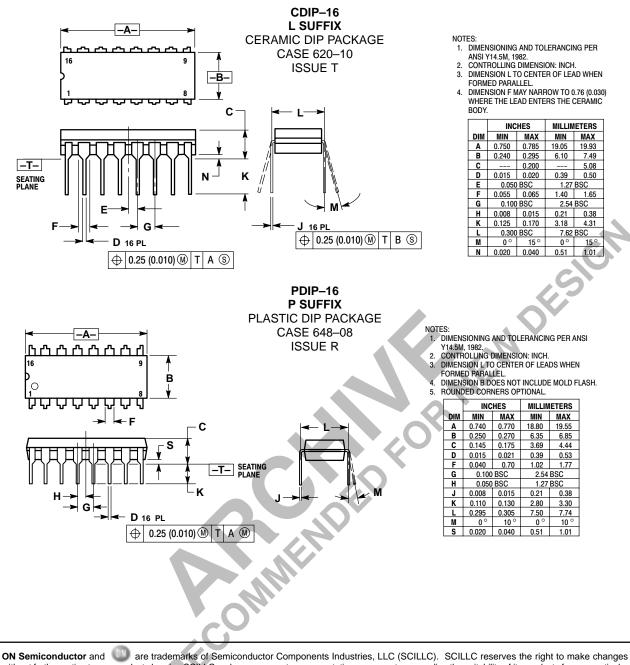

#### PACKAGE DIMENSIONS

**ON Semiconductor** and are trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer.

## PUBLICATION ORDERING INFORMATION

#### Literature Fulfillment:

Literature Distribution Center for ON Semiconductor

P.O. Box 5163, Denver, Colorado 80217 USA

Phone: 303–675–2175 or 800–344–3860 Toll Free USA/Canada Fax: 303–675–2176 or 800–344–3867 Toll Free USA/Canada Email: ONlit@hibbertco.com

N. American Technical Support: 800-282-9855 Toll Free USA/Canada

JAPAN: ON Semiconductor, Japan Customer Focus Center 4–32–1 Nishi–Gotanda, Shinagawa–ku, Tokyo, Japan 141–0031 Phone: 81–3–5740–2700 Email: r14525@onsemi.com

ON Semiconductor Website: http://onsemi.com

For additional information, please contact your local Sales Representative.