# Processor Digital Signal Processor

## **CMOS**

# **16-bit Fixed-point DSP**

# **MB86330**

## DESCRIPTION

The MB86330 is a 16-bit fixed-point DSP (Digital Signal Processor) that is based on Fujitsu-specific Dual-MAC architecture, and can implement product addition operations and double transfer at a high rate and under low power consumption.

The DSP supports a set of instructions optimum for digital signal processing in communications applications such as handy phones.

The MB86330 consists of a core section and a peripheral section. For detailed specifications of the core section, see MB86330DSP Core Section Specifications.

## FEATURES

PACKAGE

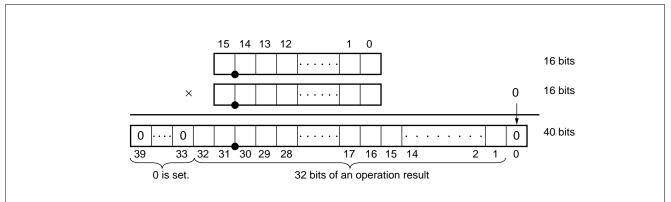

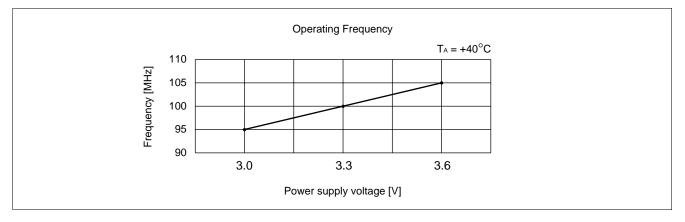

- Fixed-point operations Multiplication: 16 bits × 16 bits → 31 bits Addition: 40 bits + 40 bits → 40 bits Product addition: 40 bits ±16 bits × 16 bits → 40 bits Maximum operation speed: 100 MIPS at 3.3 V

- Memory configuration

Data RAM: Two sectors that can be accessed concurrently

An external RAM (ERAM) is supported.

Memory mapped I/O system characterized by allocation of I/O devices in the memory space

Instruction RAM: 48 Kwords × 16 bits

Table RAM: 16 Kwords × 16 bits

(Continued)

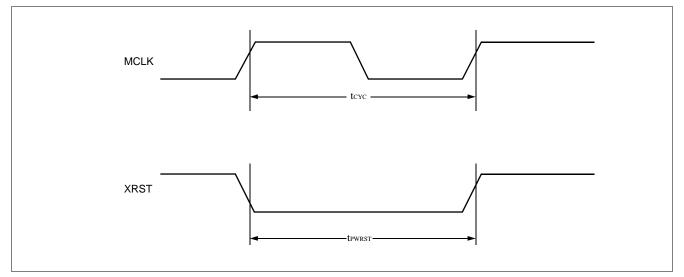

# 256-pin Ceramic PGA

- Addressing

Two independent address units

Eight general-purpose registers

Addressing function that can update a register

Circular addressing

Two address update registers

- Supply voltage: 3.3 V (single type of supply voltage)

- Ceramic package: PGA-256

## PIN ASSIGNMENT

(Top view) O 114 0 173 0 224 0 251 113 0 172 223 0 111 170 221 0 ○ 118 ○ 177 ○ 228 117 176 227 0  $\bigcirc_{115}\\ \bigcirc_{174}\\ \bigcirc_{225}\\ \bigcirc$ 0 168 0 167 219 0 O 218 O <sup>253</sup> () $\bigcirc$ Extra index pin 198 143 80 9  $\bigcirc 243 \\ 200 \\ 145 \\ 82 \\ 11 \\ 0 \\ 82 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0 \\ 11 \\ 0$  $\bigcirc^{244}_{202}\bigcirc^{202}_{147}\bigcirc^{84}_{84}\bigcirc^{13}_{13}\bigcirc$ Ć  $\bigcirc$  $\bigcup_{196}^{196}$  $\bigcup_{139}^{194} \bigcirc_{76}^{76} \bigcirc_{5}^{5} \bigcirc$ 142 79 8 149 86 15  $\bigcirc^{203}_{148} \bigcirc^{85}_{85} \bigcirc^{14}_{14} \bigcirc$ (PGA-256C-A03)

| Pin<br>no. | I/O | Pin<br>name |

|------------|-----|-------------|------------|-----|-------------|------------|-----|-------------|------------|-----|-------------|

| 1          | 0   | PAO27       | 33         | I/O | ED13        | 65         | 0   | PAO7        | 97         | I/O | EDI         |

| 2          | I   | ICAD0       | 34         |     | N.C.        | 66         | 0   | PAO10       | 98         | I/O | ED3         |

| 3          | 0   | PAO30       | 35         | I/O | ICDT12      | 67         | 0   | ST2         | 99         | _   | N.C.        |

| 4          | 0   | IRO0        | 36         | I/O | ICDT10      | 68         | 0   | PAO13       | 100        | I/O | ED10        |

| 5          | 0   | IRO3        | 37         | I/O | ICDT6       | 69         | 0   | PAO15       | 101        | I/O | ED12        |

| 6          | I   | ICAD1       | 38         |     | N.C.        | 70         | 0   | FF          | 102        | I/O | ED15        |

| 7          | 0   | IRO8        | 39         | I/O | ICDT3       | 71         | 0   | PAO21       | 103        | I/O | ICDT13      |

| 8          | 0   | IRO10       | 40         |     | N.C.        | 72         | 0   | PAO23       | 104        | I/O | ICDT11      |

| 9          | 0   | IRO14       | 41         | 0   | AINT6       | 73         | 0   | PAO24       | 105        | I/O | ICDT9       |

| 10         | I   | ICAD3       | 42         | 0   | AINT5       | 74         | 0   | PAO28       | 106        | I/O | ICDT5       |

| 11         | 0   | IRO17       | 43         |     | INT4        | 75         | 0   | PAO31       | 107        | I/O | ICDT2       |

| 12         | 0   | IRO20       | 44         | Ι   | SCZC        | 76         | 0   | IRO1        | 108        | 0   | AINT7       |

| 13         | 0   | IRO23       | 45         |     | N.C.        | 77         | 0   | IRO4        | 109        | I   | INT6        |

| 14         | 0   | IRO26       | 46         |     | N.C.        | 78         | 0   | IRO6        | 110        | I   | INT5        |

| 15         | 0   | IRO28       | 47         |     | N.C.        | 79         | I   | ICAD2       | 111        | I   | INT3        |

| 16         | 0   | IRO30       | 48         |     | N.C.        | 80         | 0   | IRO13       | 112        | —   | N.C.        |

| 17         | —   | N.C.        | 49         | Ι   | F0          | 81         | 0   | IRO16       | 113        | -   | N.C.        |

| 18         |     | N.C.        | 50         | I   | MOD0        | 82         | 0   | IRO18       | 114        | Ι   | MCLK        |

| 19         | 0   | PAGE1       | 51         | 0   | AINT2       | 83         | 0   | IRO21       | 115        | I   | BREAK       |

| 20         | 0   | XERD        | 52         | 0   | AINT1       | 84         | —   | N.C.        | 116        | Ι   | MOD2        |

| 21         | I   | WMD0        | 53         |     | N.C.        | 85         | 0   | IRO27       | 117        | —   | N.C.        |

| 22         | 0   | EA1         | 54         |     | N.C.        | 86         | _   | N.C.        | 118        | I   | INT1        |

| 23         | 0   | EA4         | 55         | I   | SMCK        | 87         |     | N.C.        | 119        | —   | N.C.        |

| 24         | 0   | EA5         | 56         |     | SMEN        | 88         | _   | N.C.        | 120        | —   | N.C.        |

| 25         | 0   | EA9         | 57         | 0   | PDXED       | 89         | 0   | BTACT       | 121        | —   | N.C.        |

| 26         | 0   | EA11        | 58         |     | SYI1        | 90         | 0   | XEWR        | 122        | —   | VS          |

| 27         |     | N.C.        | 59         | -   | SCI1        | 91         | I   | WMD1        | 123        | I   | SY10        |

| 28         | 0   | EA15        | 60         | 0   | SDO0        | 92         | 0   | EA2         | 124        | I   | SDI1        |

| 29         | I/O | ED2         | 61         | 0   | SDO1        | 93         | _   | N.C.        | 125        | I   | SYO0        |

| 30         | I/O | ED6         | 62         | 0   | PAO0        | 94         | 0   | EA7         | 126        | I   | SYO1        |

| 31         | I/O | ED8         | 63         | 0   | PAO4        | 95         | 0   | EA10        | 127        | 0   | XMONI       |

| 32         | _   | N.C.        | 64         | -   | ICCN        | 96         | 0   | EA14        | 128        | 0   | PAO3        |

N.C.: Pin not connected

(Continued)

| Pin<br>no. | I/O | Pin<br>name |

|------------|-----|-------------|------------|-----|-------------|------------|-----|-------------|------------|-----|-------------|

| 129        | 0   | PAO6        | 161        | I/O | ED11        | 193        | 0   | PAO26       | 225        | —   | N.C.        |

| 130        | 0   | PAO8        | 162        | I/O | ED14        | 194        | —   | VS          | 226        | —   | VS          |

| 131        | 0   | PAO11       | 163        | I/O | ICDT14      | 195        | —   | N.C.        | 227        | —   | N.C.        |

| 132        | 0   | ST1         | 164        |     | N.C.        | 196        | _   | VS          | 228        | _   | VS          |

| 133        | 0   | PAO14       | 165        | I/O | ICDT8       | 197        | 0   | IRO7        | 229        | I   | SMDT        |

| 134        | 0   | PAO17       | 166        | I/O | ICDT4       | 198        | 0   | IRO11       | 230        | —   | VS          |

| 135        | 0   | PAO20       | 167        | I/O | ICDT1       | 199        | —   | VS          | 231        | I   | SCI0        |

| 136        | 0   | PAO22       | 168        | I   | INT7        | 200        | —   | N.C.        | 232        | —   | VS          |

| 137        | 0   | PAO25       | 169        | —   | N.C.        | 201        | 0   | IRO24       | 233        | 0   | ADBRK       |

| 138        | 0   | PAO29       | 170        | 0   | AINT3       | 201        | _   | VS          | 234        | 0   | PAO1        |

| 139        |     | N.C.        | 171        | —   | N.C.        | 203        | 0   | IRO31       | 235        |     | VS          |

| 140        | 0   | IRO2        | 172        | I   | PSTOP       | 204        | _   | VS          | 236        | I   | XICOPE      |

| 141        | 0   | IRO5        | 173        | I   | PM          | 205        | 0   | PAGE0       | 237        | 0   | ST0         |

| 142        | 0   | IRO9        | 174        | I   | F1          | 206        |     | VS          | 238        |     | VS          |

| 143        | 0   | IRO12       | 175        | Ι   | MOD1        | 207        | 0   | EA0         | 239        | 0   | PAO18       |

| 144        | 0   | IRO15       | 176        | I   | INT2        | 208        | _   | VS          | 240        | —   | VS          |

| 145        | 0   | IRO19       | 177        | I   | XRST        | 209        | 0   | EA8         | 241        | —   | VD          |

| 146        | 0   | IRO22       | 178        | —   | N.C.        | 210        | 0   | EA12        | 242        | —   | VD          |

| 147        | 0   | IRO25       | 179        | —   | N.C.        | 211        | _   | VS          | 243        | —   | VD          |

| 148        | 0   | IRO29       | 180        | I   | TCIF        | 212        | I/O | ED5         | 244        | —   | VD          |

| 149        | —   | N.C.        | 181        | I   | SDI0        | 213        | I/O | ED9         | 245        | —   | VD          |

| 150        | —   | N.C.        | 182        | I   | SCO0        | 214        | _   | VS          | 246        | —   | VD          |

| 151        | I   | BOOT        | 183        | 0   | PACK        | 215        | I/O | ICDT15      | 247        | —   | VD          |

| 152        | 0   | XEREQ       | 184        | I   | SCO1        | 216        | _   | VS          | 248        | —   | VD          |

| 153        |     | N.C.        | 185        | 0   | PAO2        | 217        | I/O | ICDT7       | 249        |     | VD          |

| 154        | 0   | EA3         | 186        | 0   | PAO5        | 218        | _   | VS          | 250        | —   | VD          |

| 155        | 0   | EA6         | 187        | 0   | PAO9        | 219        | I/O | ICDT0       | 251        | —   | VD          |

| 156        |     | N.C.        | 188        | 0   | PAO12       | 220        |     | VS          | 252        | _   | VD          |

| 157        | 0   | EA13        | 189        | I   | XICWE       | 221        | 0   | AINT4       | 253        |     | VD          |

| 158        | I/O | ED0         | 190        | 0   | PAO16       | 222        | 0   | SCKOUT      | 254        |     | VD          |

| 159        | I/O | ED4         | 191        | 0   | PAO19       | 223        |     | VS          | 255        |     | VD          |

| 160        | I/O | ED7         | 192        | 0   | L           | 224        |     | N.C.        | 256        | —   | VD          |

N.C.: Pin not connected

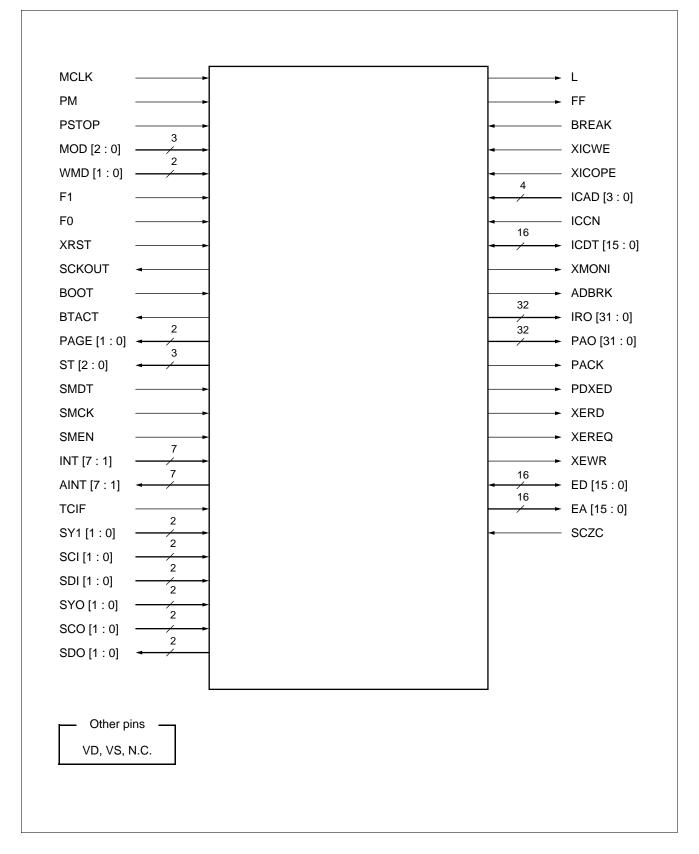

## ■ EXTERNAL PIN LAYOUT

## ■ PIN DESCRIPTION

| Pin no.            | Pin name      | Bit | I/O | Active | Pull up<br>or<br>pull down |                                                          | I          | Function      |                        |

|--------------------|---------------|-----|-----|--------|----------------------------|----------------------------------------------------------|------------|---------------|------------------------|

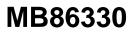

| 114                | MCLK          | 1   | I   |        | _                          | Master clo                                               | ock input  |               |                        |

|                    |               |     |     |        |                            | MCLK                                                     |            | $\frown \_$   |                        |

|                    |               |     |     |        |                            | SCKout                                                   | ٦          | <u> </u>      |                        |

|                    |               |     |     |        |                            | (Internal sy<br>clock)                                   | /stem      | 1 machine     | cycle                  |

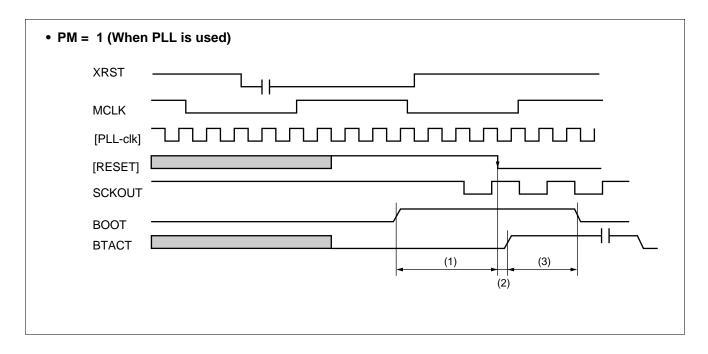

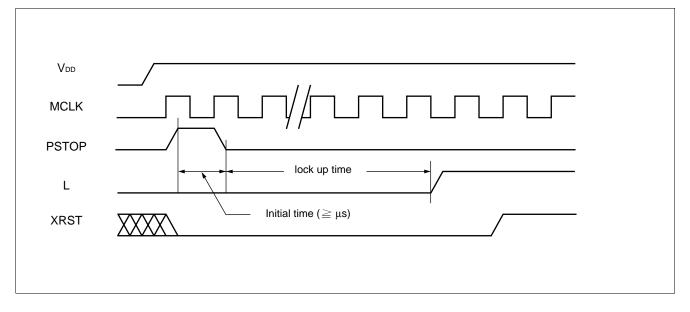

| 173                | PM            | 1   | I   |        | Pull up                    | Internal master clock input ca<br>0: MCLK, 1: PLL output |            |               | n be selected.         |

| 172                | PSTOP         | 1   | I   | Н      |                            | PLL operation setup<br>0: PLL operation, 1: PLL stop     |            |               |                        |

| 50,                | MOD           | 3   | Ι   |        | Pull down                  | Operating mode                                           |            |               |                        |

| 116,<br>175        | [2:0]         |     |     |        |                            | MOD2 MOD1 MOD0                                           |            |               | Operating<br>mode      |

|                    |               |     |     |        |                            | 0                                                        | 0 0 0      |               | Single chip<br>mode    |

|                    |               |     |     |        |                            | Other than above                                         |            |               | Disabled               |

| 21,                | WMD           | 2   | I   |        | Pull down                  | External memory WAIT mode                                |            |               | )                      |

| 91                 | [1:0]         |     |     |        |                            |                                                          |            | Wait<br>cycle | Can data be rewritten? |

|                    |               |     |     |        |                            | 0 0 0 cyc                                                |            | No            |                        |

|                    |               |     |     |        |                            | 0                                                        | 1          | 5 сус         | No                     |

|                    |               |     |     |        |                            | 1                                                        | 0          | 15 сус        | Yes                    |

|                    |               |     |     |        |                            | 1                                                        | 1          | 30 cyc        | Yes                    |

| 174                | F1            | 1   | Ι   |        |                            | Flag input                                               | 1 (level s | ense)         |                        |

| 49                 | F0            | 1   | Ι   |        | _                          | Flag input                                               | 0 (level s | ense)         |                        |

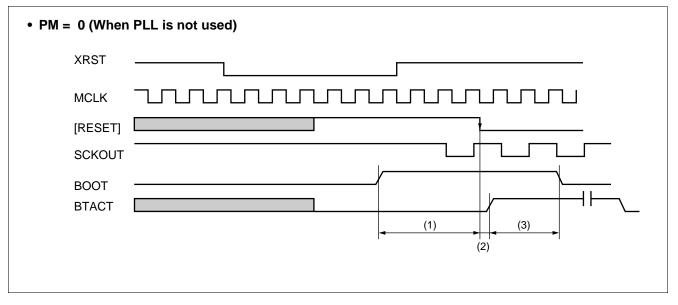

| 177                | XRST          | 1   | Ι   | L      |                            | Reset inpu                                               | ut         |               |                        |

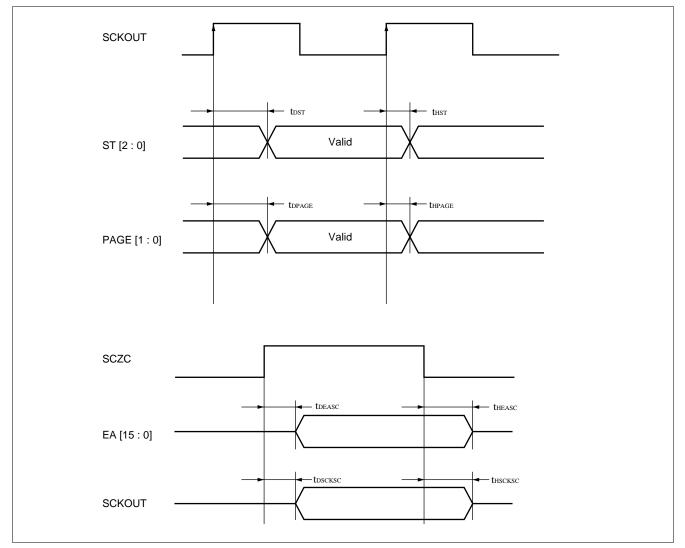

| 222                | SCKOUT        | 1   | 0   |        |                            | Internal sy                                              | vstem cloo | ck output     |                        |

| 44                 | SCZC          | 1   | I   | Н      | Pull down                  | Hi-z contro<br>[15:0] (SC                                |            |               | POUT and EA            |

| 151                | BOOT          | 1   | I   | Н      |                            | Input for a                                              | BOOT m     | ode contre    | ol signal              |

| 89                 | BTACT         | 1   | 0   | Н      |                            | Output for signal                                        | a BOOT     | mode stat     | us indication          |

| 19,<br>205         | PAGE<br>[1:0] | 2   | 0   |        |                            | Output for selection of                                  |            |               | y/page                 |

| 67,<br>132,<br>237 | ST<br>[2:0]   | 3   | 0   | _      |                            | Internal st                                              | atus outp  | ut            |                        |

| Pin no.                                                          | Pin name       | Bit | I/O | Active | Pull up<br>or<br>pull down | Function                                                                                                  |

|------------------------------------------------------------------|----------------|-----|-----|--------|----------------------------|-----------------------------------------------------------------------------------------------------------|

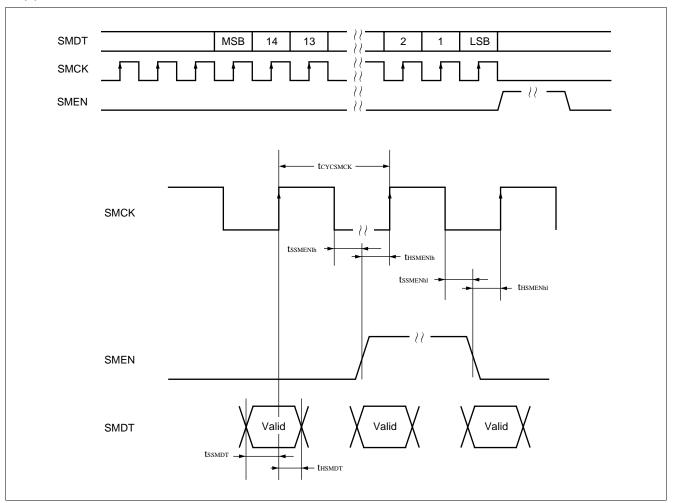

| 229                                                              | SMDT           | 1   | I   |        |                            | Serial input data (16 bits) for operating mode (SMODE) setup                                              |

| 55                                                               | SMCK           | 1   | I   |        |                            | Serial input clock for operating mode (SMODE) setup                                                       |

| 56                                                               | SMEN           | 1   | Ι   | Н      | —                          | Pulse input for operating mode (SMODE) setup<br>Upon completion of setup, a positive pulse is<br>entered. |

| 43, 109 to 111,<br>118, 168, 176                                 | INT<br>[7:1]   | 7   | I   | L      | Pull up                    | Input for INT7 to INT1 interrupt request signals                                                          |

| 41, 42, 51, 52,<br>108, 170, 221                                 | AINT<br>[7:1]  | 7   | 0   | L      |                            | Output for INT7 to INT1 interrupt acknowl edge signals                                                    |

| 180                                                              | TCIF           | 1   | I   | Н      |                            | Used for DC setup. "0": PCM, "1": TCH<br>Used to set serial port 1.                                       |

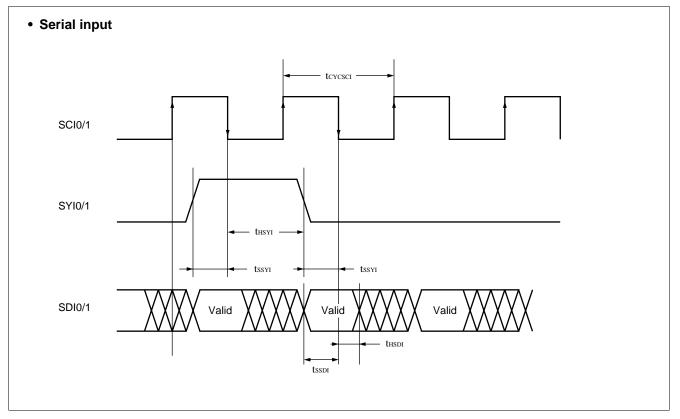

| 58,<br>123                                                       | SYI<br>[1:0]   | 2   | I   | Н      |                            | Input pins for synchronization signals for serial input port 1/0                                          |

| 59,<br>231                                                       | SCI<br>[1:0]   | 2   | Ι   |        |                            | Clock input for serial input port 1/0                                                                     |

| 124,<br>181                                                      | SDI<br>[1:0]   | 2   | I   |        |                            | Data input for serial input port 1/0                                                                      |

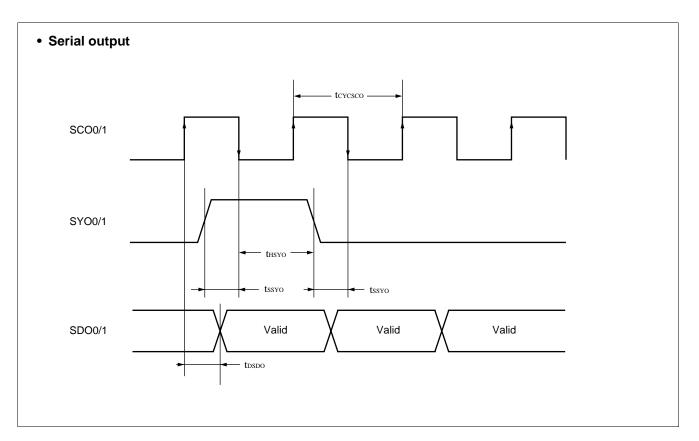

| 125,<br>126                                                      | SYO<br>[1:0]   | 2   | I   | Н      |                            | Synchronization signal input for serial output port 1/0                                                   |

| 182,<br>184                                                      | SCO<br>[1:0]   | 2   | I   |        |                            | Clock input for serial output port 1/0                                                                    |

| 60,<br>61                                                        | SDO<br>[1:0]   | 2   | 0   |        |                            | Data output for serial output port 1/0                                                                    |

| 192                                                              | L              | 1   | 0   |        |                            | PLL status output                                                                                         |

| 70                                                               | FF             | 1   | 0   |        |                            | Output for test                                                                                           |

| 115                                                              | BREAK          | 1   | Ι   | L      | Pull up                    | Break input for the emulator                                                                              |

| 189                                                              | XICWE          | 1   | Ι   | L      | Pull up                    | Input for an emulator write signal                                                                        |

| 236                                                              | XICOPE         | 1   | I   | L      | Pull up                    | Input for an emulator read signal                                                                         |

| 2, 6, 10, 79                                                     | ICAD<br>[3:0]  | 4   | I   |        | Pull down                  | Address input for the emulator                                                                            |

| 64                                                               | ICCN           | 1   | I   | Н      | Pull down                  | Input for an emulator connection signal                                                                   |

| 35 to 37,39,<br>103 to 107, 163,<br>165 to 167,<br>215, 217, 219 | ICDT<br>[15:0] | 16  | I/O |        | Pull down                  | I/O for a data bus used to access the emulator                                                            |

| 127                                                              | XMONI          | 1   | 0   | L      |                            | Output for indicating emulator monitor mode status                                                        |

| 233                                                              | ADBRK          | 1   | 0   | Н      | —                          | Output for indicating occurrence of an ADBKP register event for the emulator                              |

| Pin no.                                                                                                                                                                                               | Pin name      | Bit | I/O | Active | Pull up<br>or<br>pull down | Function                                            |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-----|-----|--------|----------------------------|-----------------------------------------------------|

| 4, 5, 7 to 9,<br>11 to 16, 76 to 78,<br>80 to 83, 85,<br>140 to 148, 197,<br>198, 201, 203                                                                                                            | IRO<br>[31:0] | 32  | 0   |        |                            | Instruction register output for the emulator        |

| 1, 3, 62, 63, 65,<br>66, 68, 69,<br>71 to 75,<br>128 to 131,<br>133 to 138,<br>185 to 188,<br>190, 191, 193,<br>234, 239                                                                              | PAO<br>[31:0] | 32  | 0   |        |                            | Program address output for the emulator             |

| 183                                                                                                                                                                                                   | PACK          | 1   | 0   |        | —                          | Output for a PAO fetch clock for the emulator       |

| 57                                                                                                                                                                                                    | PDXED         | 1   | 0   | _      | _                          | Output for test                                     |

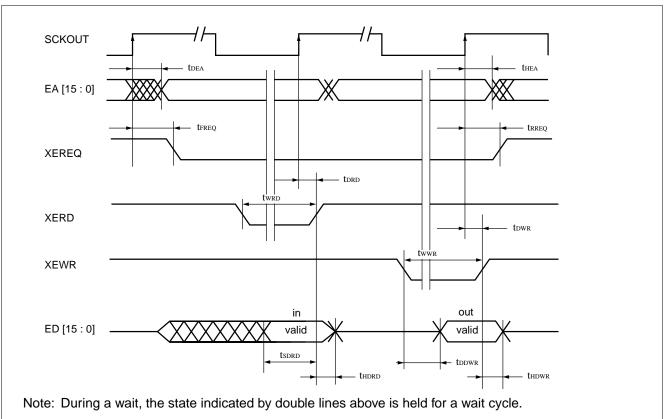

| 20                                                                                                                                                                                                    | XERD          | 1   | 0   | L      | _                          | Output for an ERAM reading signal                   |

| 152                                                                                                                                                                                                   | XEREQ         | 1   | 0   | L      | _                          | Output for an ERAM access request signal            |

| 90                                                                                                                                                                                                    | XEWR          | 1   | 0   | L      | _                          | Output for an ERAM writing signal                   |

| 29 to 31, 33,<br>97, 98,<br>100 to 102,<br>158 to 162,<br>212, 213                                                                                                                                    | ED<br>[15:0]  | 16  | I/O |        | Pull up                    | External data bus I/O pins                          |

| 22 to 26, 28,<br>92, 94 to 96,<br>154, 155, 157,<br>207, 209, 210                                                                                                                                     | EA<br>[15:0]  | 16  | 0   | _      | _                          | Output for the ERAM address                         |

| 241 to 256                                                                                                                                                                                            | VD            |     |     |        |                            | Power supply for the digital circuit (3.3 V, input) |

| 122, 194, 196,<br>199, 202, 204,<br>206, 208, 211,<br>214, 216, 218,<br>220, 223, 226,<br>228, 230, 232,<br>235, 238, 240                                                                             | VS            |     |     |        |                            | GND (input) for the digital circuit                 |

| 17, 18, 27, 32,<br>34, 38, 40,<br>45 to 48, 53, 54,<br>84, 86 to 88, 93,<br>99, 112, 113,<br>117,119 to 121,<br>139, 149, 150,<br>153, 156, 164,<br>169, 171, 178,<br>179, 195, 200,<br>224, 225, 227 | N.C.          |     |     |        |                            | Pins not connected                                  |

## ■ HANDLING DEVICES

## 1. Take Care So that the Maximum Rated Value Is Not Exceeded. (Preventing Latchup)

Latchup may occur on CMOS ICs if voltage higher than VD or lower than VS is applied to input and output pins other than medium- and high-voltage pins or if higher than the voltage which shows on "1. Absolute Maximum Ratings" in section "I Electrical Characteristics" is applied between VD and VS.

When latchup occurs, power supply current increases rapidly and might thermally damage elements. When using, take great care not to exceed the absolute maximum ratings.

## 2. Treatment of Unused Input Pins

Leaving unused input pins open could cause malfunctions. They should be connected to a pull-up or pull-down resistor.

## 3. Treatment of N.C. Pins

Be sure to leave (internally connected) N.C. pins open.

## 4. Treatment of Pins Connected to Pull-up/Pull-down Resistors

With neither a pull-up resistor nor a pull-down resistor connected, the pin state is determined depending on the input level that reflects an internal resistor. When controlling the pin state, however, connect a pull-up or pull-down resistor.

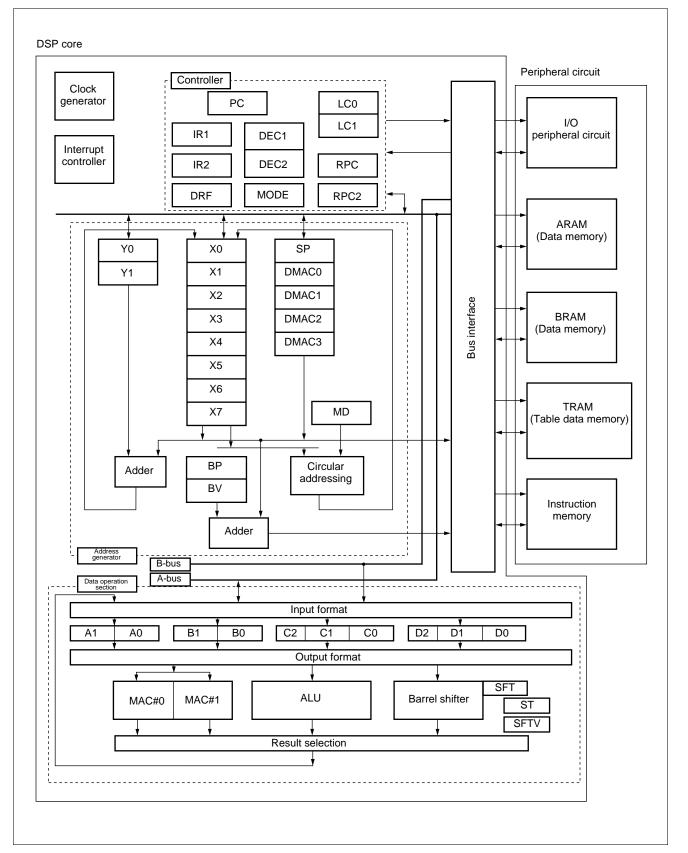

## BLOCK DIAGRAM

## ■ DESCRIPTION OF BLOCK FUNCTIONS

#### • Clock generator (CLOCK Gen.)

Generates a clock required for the DSP to control a system clock stop in the waste state and an entire clock stop for sleeping.

#### • Interrupt controller

Controls an INT interrupt, an overflow interrupt, and a DMA interrupt.

#### • Controller

Generates a program address and decodes an instruction to control the entire DSP.

#### • Address generator

Generates an address required for memory access. It supports a circular addressing function to control the DMA access pointer and the stack pointer.

#### • Data operation section

Performs data operations such as product addition, arithmetic operations (multiplication, division, addition and subtraction), logic operations, and shift operations.

#### Bus interface

Controls access to the memory space including instruction reading, data memory access and mapped I/O access.

#### • ARAM/BRAM

This is a data memory for data operations. A and B use different banks, enabling double transfer without a wait. (ARAM = 4 kwords, BRAM = 4 kwords)

## TRAM (Table data memory)

Sets table data required for applications.

## Instruction memory Cate preserve data

Sets program data.

#### • Mapped I/O

Supports a macro valid for applications Serial I/O: Two serial ports for transmitting CODEC data. One serial input 1 system for setting operating mode (SMODE)

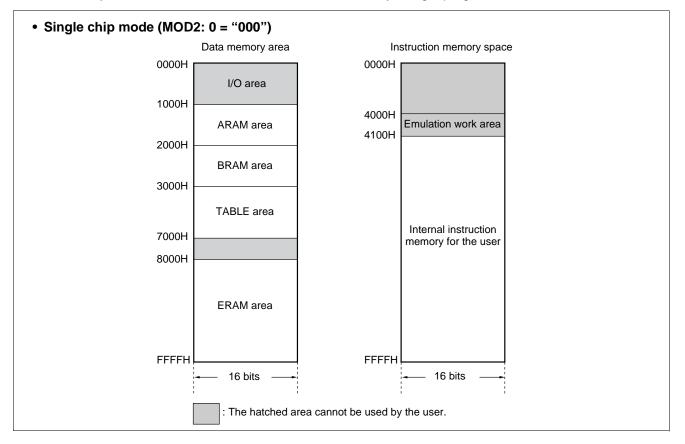

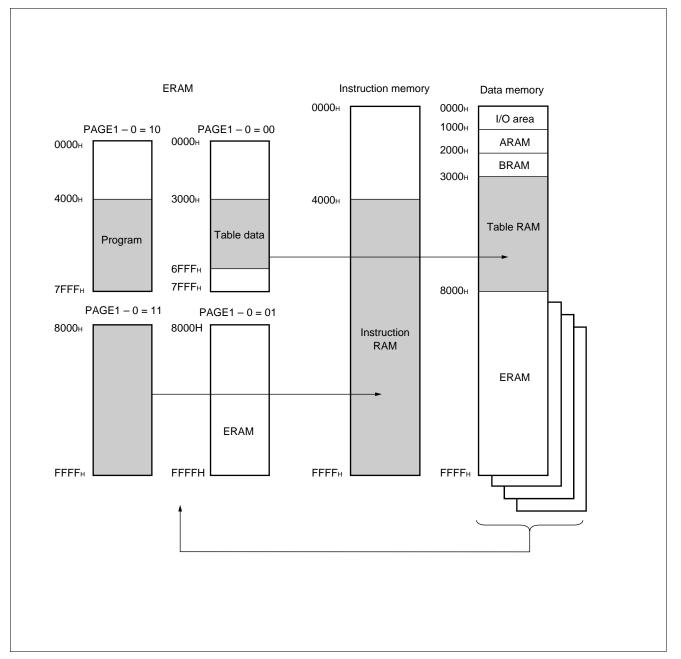

## MEMORY SPACE

#### Configuration of the memory space

The memory space consists of a data memory space and an instruction memory space. The I/O, ARAM, BRAM, TABLE, and ERAM (external memory) areas are allocated in the data memory space, while the instruction memory is allocated in the program memory space. The I/O, TABLE, ERAM (external memory), ARAM and BRAM areas in the data memory space are, however, assigned a particular data bus. The memory for any two areas can, therefore, be accessed concurrently during one cycle. What memory is accessed is determined automatically by an address value.

Addresses allocated for the memories, and their maximum size are determined as follows. Select a memory size to be allocated in this range.

#### • Memory space mode

You can select a method for allocating the data memory space and the program memory space by operating mode. Determine operating mode by mode pins (MOD2, MOD1 and MOD0) as follows.

| MOD2 | MOD1             | MOD0               | Operating mode |  |  |  |  |

|------|------------------|--------------------|----------------|--|--|--|--|

| 0    | 0                | 0 Single chip mode |                |  |  |  |  |

|      | Other than above | 9                  | Disabled       |  |  |  |  |

#### Memory map for single chip mode

The program for single chip mode (MOD2: 0 = "000") is operated by the internal program RAM (which externally downloads a program). Five areas for I/O, ARAM, BRAM, TABLE and ERAM are allocated on the data memory space, with the instruction memory allocated on a program memory space completely different from the data memory space. Although the instruction memory can have an independent address space for 64 kwords, therefore, you cannot access data in the instruction memory using a program.

The ERAM area is used by the DSP to access the data memory space. Because the ERAM area ranges from 8000<sub>H</sub> to FFFF<sub>H</sub>, however, PAGE is created in units of 32 kwords. PAGE is selected automatically.

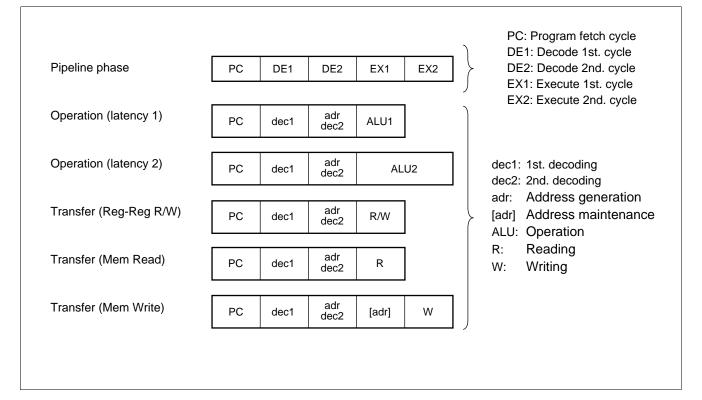

## ■ BASIC PIPELINE OPERATION

The DSP splits the contents of processing in one cycle to increase the number of pipeline sectors for high-speed operation. For operations using product adders such as product addition and multiplication, and for operations using 40-bit adders such as 40-bit addition, the processing latency is two cycles.

## ■ PRODUCT ADDITION

For product addition and multiplication, the latency is two cycles. Because it is provided with a dual product adder (MAC) for alternate processing every cycle, however, the DSP can process n successive product addition (multiplication) steps in (n + 1) cycles.

| eration latency 2         MSM (1)         MSM (3)         ···         MSM (n - 1)           MSM (2)         MSM (4)         ···         MSM (n)           (n + 1) cycles         ···         ··· |                     |     |       | 1     |        |            | _     | 1       |         | 1     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-----|-------|-------|--------|------------|-------|---------|---------|-------|

|                                                                                                                                                                                                  | Operation latency 2 | MSM | l (1) | MSN   | VI (3) |            |       | MSM     | (n - 1) |       |

| (n + 1) cycles                                                                                                                                                                                   |                     |     | MSI   | M (2) | MSI    | VI (4)     |       | · · · · | MSN     | И (n) |

|                                                                                                                                                                                                  |                     |     |       |       |        | (n + 1) cy | /cles |         |         |       |

## ■ REGISTER TABLE

| Register<br>name | Bit<br>length | Register type                    | Initial value | Register configuration                                  |

|------------------|---------------|----------------------------------|---------------|---------------------------------------------------------|

| A0               | 16            | Data register                    | Undefined     | bit 31 bit 16 bit 15 bit 0                              |

| A1               | 16            | Data register                    | _             | A1 A0 AX                                                |

| AX               | 32            | Data register                    | -             |                                                         |

| B0               | 16            | Data register                    | -             | bit 31 bit 16 bit 15 bit 0                              |

| B1               | 16            | Data register                    | -             | B1 B0 BX                                                |

| BX               | 32            | Data register                    | -             |                                                         |

| C0               | 16            | Accumulator                      | Undefined     |                                                         |

| C1               | 16            | Accumulator                      | -             |                                                         |

| C2               | 8             | Accumulator<br>(guard register)  |               | bit 39 bit 32 bit 31 bit 16 bit 15 bit 0<br>C2 C1 C0 CX |

| СХ               | 40            | Accumulator                      | -             |                                                         |

| D0               | 16            | Accumulator                      | -             | bit 39 bit 32 bit 31 bit 16 bit 15 bit 0                |

| D1               | 16            | Accumulator                      | -             | D2 D1 D0 DX                                             |

| D2               | 8             | Accumulator<br>(guard register)  |               |                                                         |

| DX               | 40            | Accumulator                      | -             |                                                         |

| X0               | 16            | Address register                 | Undefined     |                                                         |

| X1               | 16            | Address register                 | -             | bit 15 bit 0 bit 15 bit 0                               |

| X2               | 16            | Address register                 | -             | Y0 X0                                                   |

| X3               | 16            | Address register                 | -             | Y1 X1                                                   |

| X4               | 16            | Address register                 | -             | X2                                                      |

| X5               | 16            | Address register                 | -             | X3                                                      |

| X6               | 16            | Address register                 | -             | X4                                                      |

| X7               | 16            | Address register                 | 1             | X5                                                      |

| Y0               | 16            | Address register update register |               | X6<br>X7                                                |

| Y1               | 16            | Address register update register |               |                                                         |

| Register<br>name | Bit<br>length | Register type             | Initial value | Register configuration                       |

|------------------|---------------|---------------------------|---------------|----------------------------------------------|

| BP               | 16            | Base pointer              | Undefined     |                                              |

| BV               | 16            | Circular register         |               |                                              |

| MD               | 16            | Modulo register           |               | bit 15 bit 0 bit 15 bit 0                    |

| RPC              | 16            | Repeat counter 1          |               | BP ST                                        |

| RPC2             | 16            | Repeat counter 2          |               | BV bit 15 bit 0                              |

| DOSTR            | 16            | DO start address register |               | MD MODE<br>RPC DRF                           |

| DOEND            | 16            | DO end address register   |               | RPC2     bit 5     bit 0       DOSTR     SFT |

| LC0              | 16            | Loop counter              |               | DOEND                                        |

| LC1              | 16            | Loop counter              |               | LCO                                          |

| SFT              | 6             | Shift register            |               | LC1                                          |

| SFTV             | 16            | Shift register            |               | bit 15 bit 0                                 |

| ST               | 16            | Status register           | 0000000в      | SFTV                                         |

| MODE             | 16            | Mode register             | 0000000в      |                                              |

| DRF              | 16            | Flag holding register     |               |                                              |

| DMAC0            | 16            | DMA counter               | Undefined     |                                              |

| DMAC1            | 16            | DMA counter               |               | bit 15 bit 0 bit 15 bit 0                    |

| DMAC2            | 16            | DMA counter               |               | PC DMACO                                     |

| DMAC3            | 16            | DMA counter               |               | SP DMAC1<br>DMAC2                            |

| PC               | 16            | Program counter           | FFFD          | DMAC2<br>DMAC3                               |

| SP               | 16            | Stack pointer             | Undefined     | DIVINOS                                      |

## REGISTERS

#### • Data registers (A0, A1, B0 and B1)

Each of the data registers consists of four words (16 bits). They can be used as four word-length registers (16 bits) and two long-word registers (32 bits) to execute various arithmetic operation instructions, logic operation instructions, and transfer instructions.

## • Accumulators (C0 to C1, and D0 to D2)

The accumulators can be linked as two 40-bit registers (CX and DX) to execute various arithmetic operation instructions, logic operation instructions, and transfer instructions. The 40-bit length registers (CX and DX) can be specified as destinations for product addition instructions. Four 16-bit length accumulators (C0, C1, D0 and D1), and two 8-bit length accumulators (C2 and D2) are supported.

## • Address registers (X0 to X7)

Eight 16-bit address registers are supported. An address register is used to specify an operand address for transfer. Immediate values (1 to -2) or the address update registers (Y0 and Y1) can be used to update address registers. They can also be updated automatically by transfer.

## • Address update registers (Y0 and Y1)

Two 16-bit address update registers are supported. The address update registers are used to update address registers during addressing.

#### • Base pointer (BP)

The base pointer consists of 16 bits. The contents of the base pointer plus a 7-bit immediate value are generated as the address value during direct 7-bit length addressing.

#### • Circular register (BV)

The circular register, which consists of 16 bits, provides an offset value for circular addressing.

#### • Modulo register (MD)

The modulo register, which consists of 16 bits, is used to specify an addressing range for circular addressing.

#### • Repeat counter (RPC)

The repeat counter, which consists of 16 bits, is used to specify the number of times the REP/DO instruction is repeated. During execution of the repeat instruction, the repeat counter is decremented by one every repeat operation cycle.

#### • Repeat counter 2 (RPC2)

Repeat counter 2, which consists of 16 bits, is used to specify the number of times the REP2 instruction is repeated. During execution of the repeat 2 instruction, repeat counter 2 is decremented by one every repeat operation cycle.

#### • DO address registers (DOSTR and DOEND)

These registers maintain a loop start address (DOSTR)/end address (DOEND) for the DO instruction. They can process only PUSH/POP.

#### Loop counters (LC0 and LC1)

Each of the loop counters consists of 16 bits. They store the number of times repetition is made in a specified address range.

#### (Continued)

#### • Shift register (SFT)

The SFT register consists of signed 6 bits. This shift value storage register stores the number of bits shifted during execution of the shift instruction.

#### • Shift register (SFTV)

The SFTV register, which consists of 16 bits, is used to store the results of CMLT and CMGT instruction.

## • Status register (ST)

The status register, which consists of 16 bits, is assigned bits for storing information about results of operations (carry and overflow) and for setting operating mode.

#### • Mode register (MODE)

This register is used to specify modes of operations and transfer, and interrupts.

#### • Flag holding register (DRF)

This register holds flags for the DO, REP and REP2 instructions. It can process only PUSH/POP. This register is cleared by the PUSH instruction.

## • DMA counters (DMAC0 to DMAC3)

When a DMA interrupt occurs, this register stores the address of the data transfer source or the data transfer destination.

## • Program counter (PC)

The program counter, which consists of 16 bits, points to the memory address that stores an instruction code to be executed by the CPU. While it is updated automatically by instruction execution, the program counter can be rewritten by a conditional branch, a subroutine call instruction, an interrupt, and a reset. Executing the repeat instruction stops a program counter update.

#### • Stack pointer (SP)

The stack pointer, which consists of 16 bits, stores addresses for saving and transferring the contents of registers upon execution of the PUSH/POP instruction, the subroutine call instruction, or an interrupt.

## ■ DETAILED DESCRIPTION OF SPECIAL REGISTERS

## (1) Status Register

| bit 15 | bit 14 | bit 13 | bit 12 | bit 11 | bit 10 | bit 9 | bit 8 | bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |

|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| IT     | OV3    | OV1    | INT2   | INT1   | INT0   | MDMA  | СР    | RND   | ITG   | V3    | V2    | V1    | Ν     | Z     | С     |

| Bit abbreviation | Bit name                          | Description                                                                                                                                                                         |

|------------------|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| С                | Carry flag                        | Set when carry occurs as a result of operation execution.<br>Reset when no carry occurs.<br>Not changed by transfer instruction execution.                                          |

| Z                | Zero flag                         | Set when the operation result is 0.<br>Reset when the operation result is not 0.<br>Not changed by transfer instruction execution.                                                  |

| N                | Negative flag                     | Set when the operation result is smaller than 0.<br>Reset when the operation result is equal to or greater than 0.<br>Not changed by transfer instruction execution.                |

| V1               | Overflow flag 1                   | Set when the operation result overflows.<br>Reset when the operation result does not overflow.<br>Not changed by transfer instruction execution.                                    |

| V2               | Overflow flag 2                   | Set when the operation result overflows.<br>Set V2 is reset only by hardware or by ST programming by the<br>transfer instruction.<br>Not changed by transfer instruction execution. |

| V3               | Overflow flag 3                   | Set when the operation result of an instruction stored in CX or DX cannot be expressed by 32 bits (but by 40 bits). Reset when the operation result can be expressed by 32 bits.    |

| ITG              | Operating mode specification flag | Specify this when executing multiplication in integral mode.                                                                                                                        |

| RND              | Rounding mode setup               | Used to set ON/OFF of rounding processing when data is transferred from a register consisting of 32 or more bits to a 16-bit register.                                              |

| CP               | Clip flag                         | Used to specify whether the operation result is to be clipped when overflow occurs during the operation.                                                                            |

| MDMA             | DMA enable flag                   | Enables a DMA interrupt. (0: Disabled)                                                                                                                                              |

| INT0             | Interrupt enable flag             | INT0 (SMODE) interrupt enable flag<br>0: Disabled, 1: Enabled                                                                                                                       |

| INT1             | Interrupt enable flag             | INT1 interrupt enable flag<br>0: Disabled, 1: Enabled                                                                                                                               |

| INT2             | Interrupt enable flag             | INT2 interrupt enable flag<br>0: Disabled, 1: Enabled                                                                                                                               |

| OV1              | V1 interrupt enable flag          | Operation overflow interrupt enable flag. An interrupt is generated when V1 is set.<br>0: An interrupt is disabled. 1: An interrupt is enabled.                                     |

| OV3              | V3 interrupt enable flag          | Operation overflow interrupt enable flag. An interrupt is generated when V3 is set.<br>0: An interrupt is disabled. 1: An interrupt is enabled.                                     |

| IT               | Interrupt enable flag             | OV1, OV3 and INT0 to INT7 interrupt enable flag<br>0: An interrupt is disabled. 1: An interrupt is enabled.                                                                         |

## (2) Mode Register

| bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| INT7  | INT6  | INT5  | INT4  | INT3  | _     | NCT   | NOG   |

| Bit abbreviation | Bit name                                   | Description                                                                                                    |

|------------------|--------------------------------------------|----------------------------------------------------------------------------------------------------------------|

| NOG              | Operating mode specification               | <ul> <li>0: Ordinary mode<br/>The guard bit is used.</li> <li>1: NOG mode<br/>No guard bit is used.</li> </ul> |

| NCT              | Transferred data<br>clipping specification | 0: Transferred data is clipped.<br>1: Transferred data is not clipped.                                         |

| —                | Indeterminate                              | Reserved                                                                                                       |

| INT3             | Interrupt enable flag                      | INT3 interrupt enable flag<br>0: Disabled, 1: Enabled                                                          |

| INT4             | Interrupt enable flag                      | INT4 interrupt enable flag<br>0: Disabled, 1: Enabled                                                          |

| INT5             | Interrupt enable flag                      | INT5 interrupt enable flag<br>0: Disabled, 1: Enabled                                                          |

| INT6             | Interrupt enable flag                      | INT6 interrupt enable flag<br>0: Disabled, 1: Enabled                                                          |

| INT7             | Interrupt enable flag                      | INT7 interrupt enable flag<br>0: Disabled, 1: Enabled                                                          |

## (3) DRF Register

| bit 7  | bit 6  | bit 5  | bit 4  | bit 3  | bit 2  | bit 1 | bit 0 |

|--------|--------|--------|--------|--------|--------|-------|-------|

| REPF23 | REPF22 | REPF21 | REPF13 | REPF12 | REPF11 | DOF1  | DOF2  |

| Bit abbreviation | Bit name    | Description                                                                                    |

|------------------|-------------|------------------------------------------------------------------------------------------------|

| DOF2             | DO flag 2   | Internal operation status holding flag.                                                        |

| DOF1             | DO flag 1   | <ul> <li>Only PUSH and POP are available.</li> <li>Cleared by the PUSH instruction.</li> </ul> |

| REPF11           | REP1 flag 1 |                                                                                                |

| REPF12           | REP1 flag 2 |                                                                                                |

| REPF13           | REP1 flag 3 |                                                                                                |

| REPF21           | REP2 flag 1 |                                                                                                |

| REPF22           | REP2 flag 2 |                                                                                                |

| REPF23           | REP2 flag 3 |                                                                                                |

## ■ ADDRESSING

#### • Types of addressing

When reading/writing data from/to the memory, you can use a direct addressing method for specifying a 16-bit length address space with an immediate value, and an indirect addressing method for referencing that space by an address register. The DSP supports eight address registers, two update registers, the base pointer, the circular register, and the modulo register for addressing.

#### • Addressing classification

Three indirect addressing means (AD0 to AD2) by address registers can be used to transfer a register value to a memory, data from a memory to a register, and data between memories. The available addressing means is determined depending on the type of a register for data transfer, double transfer and transfer accompanied by an operation. All addressing is performed in units of words.

#### • Addressing modes

| Μ                   | ode             | Mnemonic                                                                                                                                                                                                                                                         | Effective address                                                                                                                                        | Register update                                                                                                                     | Description                                                                            |

|---------------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

|                     | irect<br>essing | (imm16)                                                                                                                                                                                                                                                          | imm16                                                                                                                                                    | Not updated                                                                                                                         | 16-bit direct addressing                                                               |

|                     | AD0             | (Xk + + 1)<br>(Xk + + 0)<br>(Xk 1)<br>(Xk + + Y0)                                                                                                                                                                                                                | Xk<br>Xk<br>Xk<br>Xk<br>Xk                                                                                                                               | +1<br>Not updated<br>-1<br>Y0                                                                                                       | Xk can be assigned X0,<br>X1, X2 and X3.                                               |

|                     | AD1             | $\begin{array}{c} (Xm ++ 3) \\ (Xm ++ 2) \\ (Xm ++ 1) \\ (Xm ++ 0) \\ (Xm 1) \\ (Xm 2) \\ (Xm 3) \\ (Xm ++ Y1) \end{array}$                                                                                                                                      | Xm<br>Xm<br>Xm<br>Xm<br>Xm<br>Xm<br>Xm<br>Xm<br>Xm                                                                                                       | +3<br>+2<br>+1<br>Not updated<br>-1<br>-2<br>-3<br>Y1                                                                               | Xm can be assigned X4,<br>X5 and X6.                                                   |

| Indirect addressing |                 | [BV+X7 + + 3]<br>[BV+X7 + + 2]<br>[BV+X7 + + 1]<br>[BV+X7 + + 0]<br>[BV+X7 1]<br>[BV+X7 2]<br>[BV+X7 3]<br>[BV+X7 + + Y1]                                                                                                                                        | BV+X7<br>BV+X7<br>BV+X7<br>BV+X7<br>BV+X7<br>BV+X7<br>BV+X7<br>BV+X7                                                                                     | +3<br>+2<br>+1<br>Not updated<br>-1<br>-2<br>-3<br>Y1                                                                               | For circular addressing,<br>only X7 can be used.                                       |

| Ind                 | AD2             | $\begin{array}{c} (BP+disp7) \\ (Xn + + 2) \\ (Xn + + 1) \\ (Xn + + 0) \\ (Xn 1) \\ (Xn 2) \\ (Xn 3) \\ (Xn + + Y0) \\ (Xn + + Y1) \\ [BV+Xn + + 2] \\ [BV+Xn + + 1] \\ [BV+Xn + + 1] \\ [BV+Xn 1] \\ [BV+Xn 3] \\ [BV+Xn + + Y0] \\ [BV+Xn + + Y1] \end{array}$ | BP+disp7<br>Xn<br>Xn<br>Xn<br>Xn<br>Xn<br>Xn<br>Xn<br>Xn<br>Xn<br>BV+Xn<br>BV+Xn<br>BV+Xn<br>BV+Xn<br>BV+Xn<br>BV+Xn<br>BV+Xn<br>BV+Xn<br>BV+Xn<br>BV+Xn | Not updated<br>+2<br>+1<br>Not updated<br>-1<br>-2<br>-3<br>Y0<br>Y1<br>+2<br>+1<br>Not updated<br>-1<br>-2<br>-3<br>Y0<br>Y1<br>+1 | Xn can be assigned X0,<br>X1, X2, X3, X4, X5, X6<br>and X7.<br>disp7 is signed 7 bits. |

[]: Indicates circular addressing.

AD0 : For "AD0," you cannot specify circular addressing.

AD1 : For "AD1," circular addressing mode is set automatically when "X7" is selected as the address register. With "0" set in the "MD" and "BV" registers, the same operation as ordinary addressing is performed even if "X7" is selected as the address register.

AD2 : disp7 in "AD2" is signed 7 bits.

## ■ BASIC CONFIGURATION OF THE DATA OPERATION SECTION

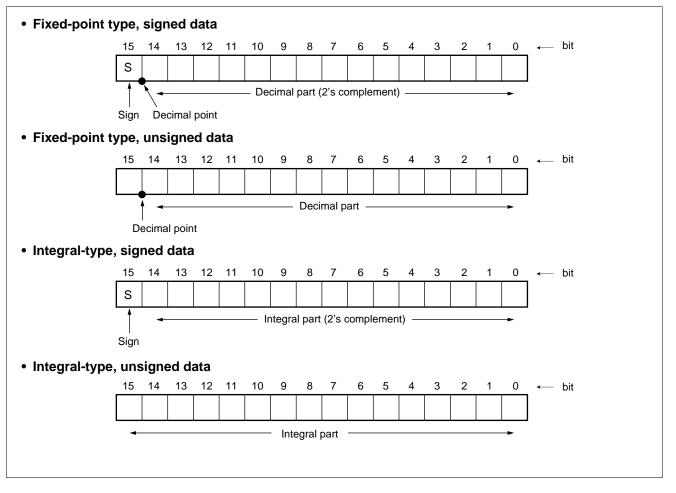

## 1. Data Format

Integral type and fixed-point data can be handled regardless of whether the data is signed or unsigned. For signed data, the most significant bit indicates a sign. A number of 1 indicates negative data, which is expressed by 2's complement. The decimal point for fixed-point type data is located between the sign bit (bit 14) and its right bit (bit 15). When the accumulator value resulting from execution of a multiplication instruction is transferred to a 16-bit length register or memory, the decimal point is returned to the original position (between bits 14 and 15).

Since a value is handled in 2's complement format for addition and subtraction, no distinction is made in the result of an operation by the above four data format. Since, for multiplication, the result of an operation varies with whether data is signed or unsigned, three combinations of "signed data x signed data," "signed data  $\times$  unsigned data," and "unsigned data  $\times$  unsigned data" exist for multiplication instructions.

For the fixed-point type and the integral type, the result of multiplication varies with the decimal point position. When fixed-point type data is multiplied, the result of the operation is stored into the accumulator with one bit shifted to the left in comparison with integral type data. The "ITG" bit in the status register is used to switch between the fixed-point type and the integral type. With this bit set at 0, an operation is executed in the fixed-point type format.

## 2. Multiplication in Fixed-point Type Mode

With the "ITG" bit in the status register set at 0, fixed-point type mode is set up, and multiplication is executed in the following format. You can use ordinary mode and NOG mode in which the guard bit is not used.

#### (1) Ordinary Mode

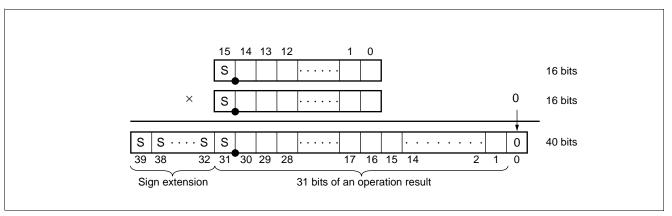

#### • Fixed-point type multiplication (signed data × signed data)

31 bits of the result of a signed operation are stored into bits 1 to 31 in the accumulator shifted to the left by one bit. "0" is set to bit 0, with the same value as at bit 31 set to bits 32 to 39.

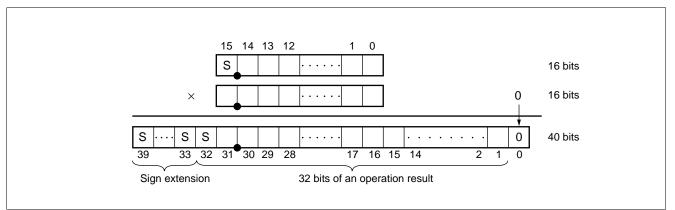

#### • Fixed-point type multiplication (signed data × unsigned data)

32 bits of the result of a signed operation are stored into bits 1 to 32 in the accumulator shifted to the left by one bit. "0" is set to bit 0, with the same value as at bit 32 set to bits 33 to 39.

Fixed-point type multiplication (unsigned data × unsigned data)

32 bits of the result of an unsigned operation are stored into bits 1 to 32 in the accumulator shifted to the left by one bit. "0" is set to bit 0, and bits 33 to 39.

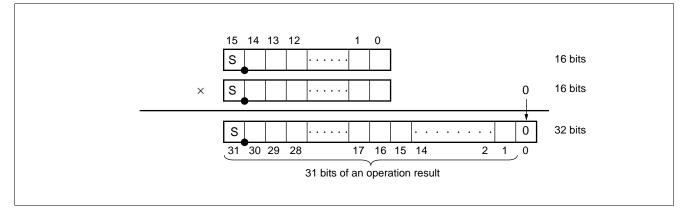

## (2) NOG Mode

In this mode, the CX and DX registers are handled as a 32-bit accumulator in which detected overflow is clipped.

• Fixed-point type multiplication (signed data x signed data) 31 bits of the result of a signed operation are stored into bits 1 to 31 in the accumulator shifted to the left by one bit. "0" is set at bit 0.

## ■ INTERRUPT

A software interrupt and a hardware interrupt are available. Interrupts are assigned specified types of priority. When interrupts occur concurrently, an interrupt with higher priority is executed earlier.

| Priority | Soft/hard | Interrupt type | Interrupt branch destination | Cause of an interrupt                                           |

|----------|-----------|----------------|------------------------------|-----------------------------------------------------------------|

| 1        | Hard      | RST            | 0xFFFE                       | Hardware reset<br>External reset signal input                   |

| 2        | Hard      | BREAK          | 0×0002*                      | Setup of emulator operation mode<br>External break signal input |

|          | Soft      | TRAP           |                              | Setup of emulator operation mode<br>Software (TRAP instruction) |

| 3        | Soft      | V1             | 0xFFFC                       | Occurrence of arithmetic operation overflow (V1)                |

| 4        |           | V3             | 0×FFFA                       | Occurrence of arithmetic operation overflow (V3)                |

| 5        | Hard      | DMA0           |                              | DMA0 signal input (for data input)                              |

| 6        |           | DMA1           |                              | DMA1 signal input (for data input)                              |

| 7        |           | DMA2           |                              | DMA2 signal input (for data output)                             |

| 8        |           | DMA3           |                              | DMA3 signal input (for data output)                             |

| 9        |           | INT0           | 0×FFF8                       | SDOME interrupt signal input                                    |

| 10       |           | INT1           | 0×FFF6                       | External interrupt signal input (INT1)                          |

| 11       |           | INT2           | 0×FFF4                       | External interrupt signal input (INT2)                          |

| 12       |           | INT3           | 0×FFF2                       | External interrupt signal input (INT3)                          |

| 13       |           | INT4           | 0×FFF0                       | External interrupt signal input (INT4)                          |

| 14       |           | INT5           | 0xFFEE                       | External interrupt signal input (INT5)                          |

| 15       |           | INT6           | 0xFFEC                       | External interrupt signal input (INT6)                          |

| 16       |           | INT7           | 0×FFEA                       | External interrupt signal input (INT7)                          |

\* : Memory space for a debug instruction

Notes: • Emulator operation mode is set by a hardware interrupt resulting from external break signal input and by a software interrupt by the TRAP instruction.

• Any interrupts other than a reset are disabled during downloading.

## ■ INSTRUCTIONS

| M        | Onenetien                                                                                       |                                                                                    | Flag change    |                |                |                |                |                |  |  |

|----------|-------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|----------------|----------------|----------------|----------------|----------------|----------------|--|--|

| Mnemonic | Operation                                                                                       | overview                                                                           | Ν              | Ζ              | С              | V1             | V2             | V3             |  |  |

| ABS      | Absolute value calculation                                                                      | A0, A1, B0, B1, C0, C1,<br>D0, D1, AX, BX, CX, DX                                  | 0              | $\updownarrow$ | _              | $\updownarrow$ | $\uparrow$     | $\updownarrow$ |  |  |

| ADD      | Addition                                                                                        | A0, A1, B0, B1, C0, C1,<br>D0, D1, AX, BX, CX, DX                                  | $\updownarrow$ | $\updownarrow$ | $\updownarrow$ | $\updownarrow$ | Ŷ              | $\updownarrow$ |  |  |

| ADD      | Addition with transfer                                                                          | $\begin{array}{c} Acc \leftarrow S1 + A1 \\ reg \leftrightarrow (AD1) \end{array}$ | $\updownarrow$ | $\updownarrow$ | $\updownarrow$ | $\updownarrow$ | $\uparrow$     | $\updownarrow$ |  |  |

| ADDC     | Addition with carry                                                                             | A0, A1, B0, B1, C0, C1,<br>D0, D1, AX, BX, CX, DX                                  | $\updownarrow$ | $\updownarrow$ | $\updownarrow$ | $\updownarrow$ | $\uparrow$     | $\updownarrow$ |  |  |

| ADSB     | Addition and subtraction                                                                        | A0, A1, B0, B1                                                                     | $\uparrow$     | $\updownarrow$ | $\updownarrow$ | $\updownarrow$ | $\uparrow$     | _              |  |  |

| ADX      | Address register addition                                                                       | $Xn \leftarrow Xn + Immediate$<br>value                                            | -              | -              | -              | _              | -              | -              |  |  |

| AND      | Logical AND                                                                                     | A0, A1, B0, B1, C0, C1,<br>D0, D1                                                  | $\updownarrow$ | $\updownarrow$ | -              | -              | -              | _              |  |  |

|          | Logical AND                                                                                     | ST                                                                                 | $\downarrow$   | $\downarrow$   | $\downarrow$   | $\downarrow$   | $\downarrow$   | $\downarrow$   |  |  |

| ASL      | $\begin{array}{c} MSB \square \square \dotsb \square \leftarrow 0 \\ C  \checkmark \end{array}$ | A0, A1, B0, B1, C0, C1,<br>D0, D1, AX, BX, CX, DX                                  | \$             | $\updownarrow$ | $\updownarrow$ | $\updownarrow$ | $\uparrow$     | $\updownarrow$ |  |  |

| ASL      | $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                            | $CX, DX  reg \leftrightarrow (AD1)$                                                | \$             | $\updownarrow$ | $\updownarrow$ | $\updownarrow$ | $\uparrow$     | \$             |  |  |

| ASR      | $MSB \leftarrow \Box\Box \cdots \Box\Box \rightarrow C$                                         | A0, A1, B0, B1, C0, C1,<br>D0, D1, AX, BX, CX, DX                                  | $\updownarrow$ | $\updownarrow$ | $\updownarrow$ | $\updownarrow$ | $\uparrow$     | $\updownarrow$ |  |  |

| BRcc     | Conditional relative branch                                                                     |                                                                                    | -              | _              | _              | -              | _              | _              |  |  |

| CALL     | Subroutine jump                                                                                 |                                                                                    | -              | _              | _              | -              | _              | -              |  |  |

| CMGT     | Transfer with (major) comparison conditions                                                     | A0, A1, B0, B1, C0, C1,<br>D0, D1, AX, BX, CX, DX                                  | \$             | $\updownarrow$ | $\updownarrow$ | $\updownarrow$ | $\uparrow$     | $\updownarrow$ |  |  |

| CMLT     | Transfer with (minor) comparison conditions                                                     | A0, A1, B0, B1, C0, C1,<br>D0, D1, AX, BX, CX, DX                                  | \$             | $\updownarrow$ | $\updownarrow$ | $\updownarrow$ | ↑              | $\updownarrow$ |  |  |

| CMP      | Comparison                                                                                      | A0, A1, B0, B1, C0, C1,<br>D0, D1, AX, BX, CX, DX                                  | $\updownarrow$ | $\updownarrow$ | $\updownarrow$ | $\updownarrow$ | $\uparrow$     | $\updownarrow$ |  |  |

| DO       | Block repetition                                                                                | RPC/imm 10                                                                         | -              | _              | _              | _              | _              | -              |  |  |

| DSTP     | Division support                                                                                | AX, BX, CX, DX/A0, A1,<br>B0, B1, C0, C1, D0, D1                                   | $\updownarrow$ | $\updownarrow$ | -              | $\updownarrow$ | $\updownarrow$ | $\updownarrow$ |  |  |

| JPC0     | Conditional absolute branch                                                                     |                                                                                    | -              | _              | _              | -              | _              | -              |  |  |

| JPC1     | Conditional absolute branch                                                                     |                                                                                    | -              | _              | _              | _              | _              | -              |  |  |

| JUMP     | Absolute branch                                                                                 |                                                                                    | -              | _              | _              | _              | _              | -              |  |  |

| LSL      | $C \leftarrow \Box \Box \cdots \Box \Box \leftarrow 0$                                          | A0, A1, B0, B1, C0, C1,<br>D0, D1, AX, BX, CX, DX                                  | \$             | \$             | $\updownarrow$ | -              | -              | -              |  |  |

| LSR      | $0 \to \square \square \square \to C$                                                           | A0, A1, B0, B1, C0, C1,<br>D0, D1, AX, BX, CX, DX                                  | $\updownarrow$ | $\updownarrow$ | $\updownarrow$ | _              | -              | -              |  |  |

| Mnemonic | Operation                                                            | overview                                                                                                                                                                                                                                                                                                                                                                                     | Flag change    |                |   |                |            |                |  |

|----------|----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|----------------|---|----------------|------------|----------------|--|

| whemonic | Operation                                                            | overview                                                                                                                                                                                                                                                                                                                                                                                     | Ν              | Ζ              | С | V1             | V2         | ٧3             |  |

| MOV      | Data transfer or duplicate<br>transfer                               | Inter-register transfer<br>REG $\leftrightarrow$ REG<br>Transfer between a<br>memory and a register<br>MEM $\leftrightarrow$ REG<br>Duplicate transfer<br>B0 $\leftarrow$ (AD0), A1 $\leftarrow$ (AD1)<br>B0 $\leftarrow$ (AD0), B1 $\leftarrow$ (AD1)<br>Immediate value transfer<br>to a register<br>REG $\leftarrow$ Immediate value<br>Inter-memory transfer<br>(AD0) $\leftarrow$ (AD1) | _              | -              | - | -              | -          | _              |  |