# **General Description**

The MAX2383 upconverter and PA driver IC is designed for emerging ARIB (Japan) and ETSI-UMTS (Europe) W-CDMA applications. The IC includes an upconversion mixer with variable gain control, an LO buffer, and a variable-gain PA driver for output power control.

The MAX2383 is designed to support the IMT-2000 frequency band. It includes a differential IF input port, an LO input port, and PA driver input/output ports. The upconverter mixer incorporates an AGC with over 30dB of gain control. The IC provides automatic throttle-back of PA driver and mixer current as output power is reduced. The main signal path and the LO buffer can be shutdown independently. The on-chip LO buffer can be kept ON while the main transmitter path is being turned on and off to minimize VCO pulling during TX gated-transmission.

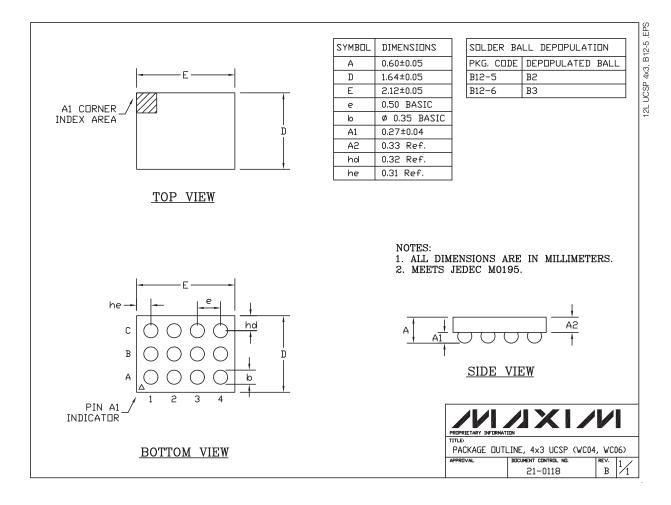

The MAX2383 is specified for +2.7V to +3.0V single supply and is housed in an ultra-miniature 3 x 4 UCSP™ package for optimum cost- and space-reduction and for best RF performance. The IC is targeted for the 2270MHz to 2580MHz LO frequency range. It is fabricated using an advanced high-frequency bipolar process. The mixer and PA driver linearity have been optimized to provide excellent RF performance in the 1920MHz to 1980MHz band, while drawing minimal current. The mixer's performance is optimized for a -10dBm ±3dB LO drive at the LO buffer input port. The LO port can be configured to be driven either singleended or differentially.

The MAX2383 achieves excellent noise and image suppression without the use of an interstage TX SAW bandpass filter, thereby saving valuable board space, cost, and supply current.

For LNA and downconverter mixer companion ICs, see the MAX2387/MAX2388/MAX2389 data sheet.

**Applications** Japanese 3G Cellular Phones (ARIB) European 3G Cellular Phones (UMTS) Chinese 3G Cellular Phones (TD-SCDMA) PCS Phones

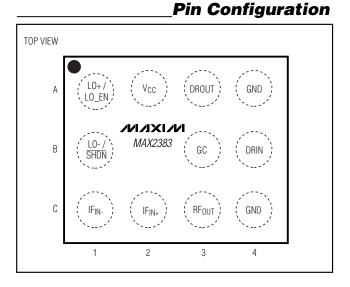

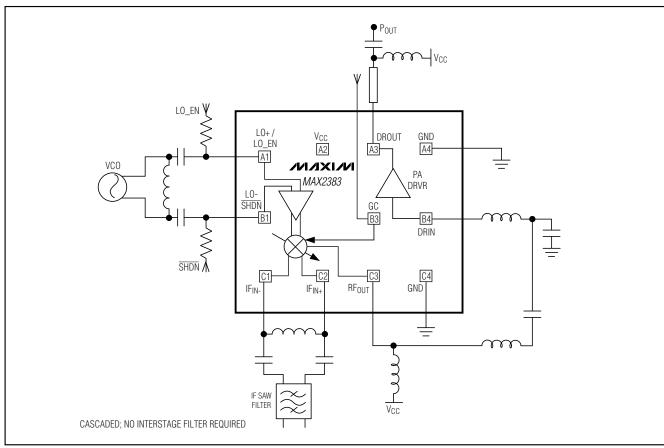

Pin Configuration appears at end of data sheet. Typical Operating Circuit appears at end of data sheet.

UCSP is a trademark of Maxim Integrated Products, Inc.

###

**Features**

- +6dBm Output Power with -46dBc ACPR

- Ultra-Miniature UCSP Package

- Upconverter Gain-Control Range: 35dB

- Automatic Dynamic Current Control

- 12mA Quiescent Supply Current

- On-Chip LO Buffer with Disable

- ♦ Low Out-of-Band Noise Power in RX Band: ≤ -144dBm/Hz at +6dBm POUT

- No Interstage TX SAW Bandpass Filter Required

### **Ordering Information**

| PART         | TEMP RANGE     | PIN-PACKAGE |  |  |  |  |

|--------------|----------------|-------------|--|--|--|--|

| MAX2383EBC-T | -40°C to +85°C | 3 x 4 UCSP  |  |  |  |  |

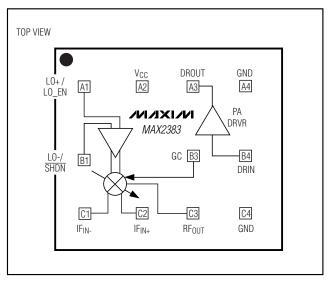

# Block Diagram

Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim/Dallas Direct! at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>CC</sub> , RF <sub>OUT</sub> to GND0.3V to +6.0             | / |

|--------------------------------------------------------------------|---|

| AC Signals+1.0V Peal                                               | < |

| SHDN, LO_EN, V <sub>GC</sub> to GND0.3V to (V <sub>CC</sub> + 0.3V |   |

| Digital Input Current±10mA                                         | À |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ )              |   |

| 12-Pin UCSP (derate 80mW/°C above +70°C) 628mV                     | V |

| Operating Temperature Range  | 40°C to +85°C  |

|------------------------------|----------------|

| Junction Temperature         | +150°C         |

| Storage Temperature Range    | 65°C to +160°C |

| Lead Temperature (Bump Refle | w)+235°C       |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

**CAUTION!** ESD SENSITIVE DEVICE

# DC ELECTRICAL CHARACTERISTICS

(V<sub>CC</sub> = +2.7V to +3.0V,  $\overline{SHDN}$  = +1.5V, T<sub>A</sub> = -40°C to +85°C. Typical values are at V<sub>CC</sub> = +2.85V, T<sub>A</sub> = +25°C, unless otherwise noted.)

| PARAMETER                        | SYMBOL          | CONDITIONS                                                            | MIN | ТҮР  | МАХ | UNITS |

|----------------------------------|-----------------|-----------------------------------------------------------------------|-----|------|-----|-------|

| Supply Voltage                   | Vcc             |                                                                       | 2.7 | 2.85 | 3.0 | V     |

| Operating Supply Current         | laa             | $P_{DROUT} = +6dBm, V_{GC} = 2.0V$                                    |     | 34   | 44  | mA    |

| Operating Supply Current         | Icc             | P <sub>IF</sub> ≤ -35dBm, V <sub>GC</sub> = 1.4V                      |     | 12   | 20  | ША    |

| Shutdown Supply Current          | Icc             | $\overline{\text{SHDN}}$ = 0.5V, LO_EN = 0.5V, V <sub>GC</sub> = 0.5V |     | 0.5  | 10  | μA    |

| LO Buffer Current                | Icc             | $\overline{\text{SHDN}}$ = 0.5V, LO_EN = 1.5V, V <sub>GC</sub> = 2V   |     | 6    | 8   | mA    |

| Digital Input Logic High         | VIH             |                                                                       | 1.5 |      | Vcc | V     |

| Digital Input Logic Low          | VIL             |                                                                       | 0   |      | 0.5 | V     |

| Input Logic High Current         | IIН             |                                                                       |     |      | 1   | μA    |

| Input Logic Low Current          | ١ <sub>١L</sub> |                                                                       | -1  |      |     | μA    |

| Recommended Gain-Control Voltage | V <sub>GC</sub> |                                                                       | 0.5 |      | 2.0 | V     |

| Gain-Control Input Bias Current  | IGC             | $0.5V \le V_{GC} \le 2.0V$                                            | -5  |      | 5   | μA    |

# **AC ELECTRICAL CHARACTERISTICS**

(MAX2383 EV Kit;  $V_{CC} = +2.7V$  to +3.0V;  $\overline{SHDN} = LO_EN = +1.5V$ ; IF source impedance =  $400\Omega$  (differential), IF input level = -16dBm (differential); LO input level = -10dBm, differential LO drive from  $150\Omega$  source impedance; mixer upconverter and PA driver are cascaded directly through an interstage matching network; DROUT drives a  $50\Omega$  load impedance;  $V_{GC} = 2.0V$ ;  $f_{IF} = 380MHz$ ,  $f_{RF} = 1920MHz$  to 1980MHz,  $f_{LO} = 2300MHz$  to 2360MHz;  $T_A = -40^{\circ}C$  to  $+85^{\circ}C$ . Typical values are at  $V_{CC} = +2.85V$ ,  $T_A = +25^{\circ}C$ , unless otherwise noted.) (Note 1)

| PARAMETER                | SYMBOL          | CONDITIONS                 |                     | MIN  | ТҮР       | МАХ  | UNITS |

|--------------------------|-----------------|----------------------------|---------------------|------|-----------|------|-------|

| CASCADED PERFORMANCE (m  | easured fro     | m IF input to DROUT (      | (PA driver output)) |      |           |      |       |

| IF Frequency             | fIF             | (Note 2)                   |                     |      | 200–600   |      | MHz   |

| RF Frequency Range       | f <sub>RF</sub> | (Note 2)                   |                     | 1920 |           | 1980 | MHz   |

| LO Frequency Range       | fLO             | High-side LO case (Note 2) |                     |      | 2270-2580 | )    | MHz   |

| Output Power (meets ACPR | Departure       |                            | $3\sigma$ limit     | 4.4  | +6        |      | dBm   |

| specifications)          | Pdrout          | $V_{GC} = 2.0V$            | $6\sigma$ limit     | 3.8  | +6        |      | иып   |

| Power Gain               | GP              | $V_{GC} = 2.0V$            |                     | 17   | 19.5      |      | dB    |

## AC ELECTRICAL CHARACTERISTICS (continued)

(MAX2383 EV Kit; V<sub>CC</sub> = +2.7V to +3.0V; SHDN = LO\_EN = +1.5V; IF source impedance =  $400\Omega$  (differential), IF input level = -16dBm (differential); LO input level = -10dBm, differential LO drive from 150 $\Omega$  source impedance; mixer upconverter and PA driver are cascaded directly through an interstage matching network; DROUT drives a 50 $\Omega$  load impedance; V<sub>GC</sub> = 2.0V; f<sub>IF</sub> = 380MHz, f<sub>RF</sub> = 1920MHz to 1980MHz, f<sub>LO</sub> = 2300MHz to 2360MHz; T<sub>A</sub> = -40°C to +85°C. Typical values are at V<sub>CC</sub> = +2.85V, T<sub>A</sub> = +25°C, unless otherwise noted.) (Note 1)

| PARAMETER                          | SYMBOL | CONDITIONS                                                                       | MIN | ТҮР  | MAX  | UNITS      |

|------------------------------------|--------|----------------------------------------------------------------------------------|-----|------|------|------------|

| Gain-Control Range                 |        | $V_{GC}$ = 0.5V to 2.0V, $P_{IF} \le -35$ dBm                                    | 25  | 35   |      | dB         |

| Adjacent Channel Power Ratio       | ACPR1  | V <sub>GC</sub> = 2.0V (5MHz offset / 3.84MHz BW)                                |     |      | -46  | dBc        |

| Alternate Channel Power Ratio      | ACPR2  | V <sub>GC</sub> = 2.0V (10MHz offset / 3.84MHz BW)                               |     |      | -56  | dBc        |

| Out-of-Band Noise Power in RX Band |        | V <sub>GC</sub> = 2.0V, P <sub>DROUT</sub> = +6dBm<br>(TX: 1980MHz; RX: 2110MHz) |     | -144 | -140 | dBm/<br>Hz |

| TX In-Band Noise Power             |        | $V_{GC} = 2.0V, P_{DROUT} = +6dBm$                                               |     | -139 | -135 | dBm/<br>Hz |

| TX In-Band Noise Power             |        | V <sub>GC</sub> = 0.5V, P <sub>DROUT</sub> = -35dBm                              |     | -147 |      | dBm/<br>Hz |

| Recommended LO Input Level         | PLO    | Differential                                                                     | -13 | -10  | -7   | dBm        |

**Note 1:** Minimum and maximum values are guaranteed by design and characterization over temperature and supply voltages. **Note 2:** Operation outside this frequency range is possible, but has not been verified.

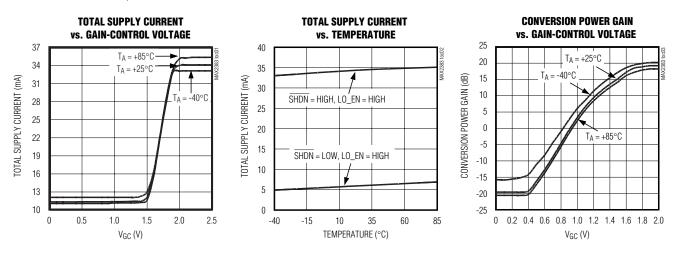

# **Typical Operating Characteristics**

(MAX2383 EV Kit; V<sub>CC</sub> = +2.85V; SHDN = LO\_EN = V<sub>CC</sub>, V<sub>GC</sub> = 2.0V; IF source impedance = 400 $\Omega$  (differential), IF input level = -16dBm (differential); LO input level = -10dBm, differential LO drive from 150 $\Omega$  source impedance; mixer upconverter and PA driver are cascaded through an interstage matching network; DROUT drives a 50 $\Omega$  load impedance; f<sub>IF</sub> = 380MHz, f<sub>RF</sub> = 1950 MHz, f<sub>LO</sub> = 2330MHz; T<sub>A</sub> = +25°C.)

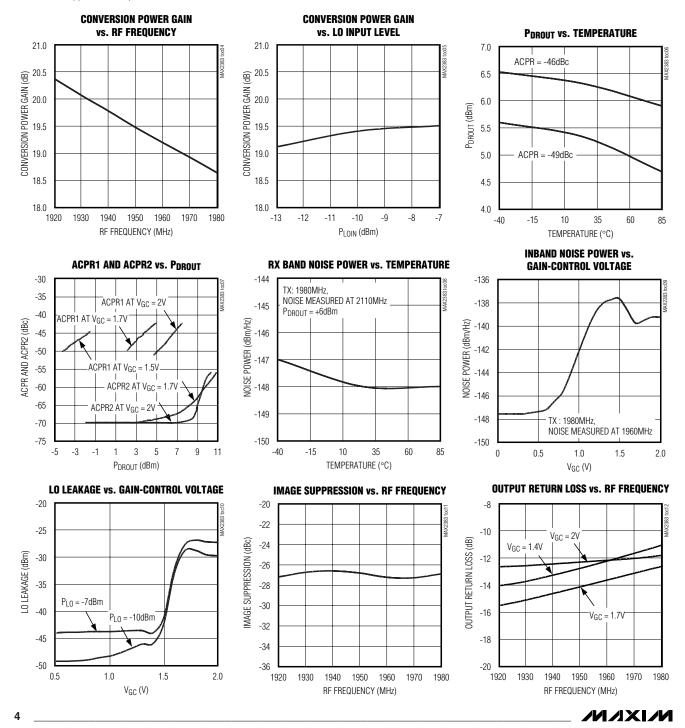

# **Typical Operating Characteristics (continued)**

(MAX2383 EV Kit; V<sub>CC</sub> = +2.85V; SHDN = LO\_EN = V<sub>CC</sub>, V<sub>GC</sub> = 2.0V; IF source impedance =  $400\Omega$  (differential), IF input level = -16dBm (differential); LO input level = -10dBm, differential LO drive from  $150\Omega$  source impedance; mixer upconverter and PA driver are cascaded through an interstage matching network; DROUT drives a  $50\Omega$  load impedance; f<sub>IF</sub> = 380MHz, f<sub>RF</sub> = 1950 MHz, f<sub>LO</sub> = 2330MHz; T<sub>A</sub> =  $+25^{\circ}$ C.)

# Pin Description

| PIN | NAME              | FUNCTION                                                                                                                                                                    |

|-----|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1+ | LO_EN<br>/LO+     | LO Buffer Enable Pin. When LOW, the LO buffer shuts off. Also noninverting input for LO port. It can be AC-<br>coupled to GND, when the LO is driven single-ended.          |

| A2  | V <sub>CC</sub>   | Power-Supply Pin. Bypass with a 330pF capacitor to GND as close to the pin as possible.                                                                                     |

| A3  | DROUT             | PA Driver Output Pin. Externally matched to $50\Omega$ .                                                                                                                    |

| A4  | GND               | Ground Reference for RF                                                                                                                                                     |

| B1  | SHDN/<br>LO-      | Shutdown Pin. When LOW, the entire part shuts off, except for LO buffer. Also inverting input for LO port. It can be AC-coupled to GND, when the LO is driven single-ended. |

| B3  | GC                | Power Control Input Pin (0.5V to 2.0V for control voltage)                                                                                                                  |

| B4  | DRIN              | PA Driver Input Pin (interstage node). Can be externally matched to $50\Omega$ .                                                                                            |

| C1  | IF <sub>IN-</sub> | Inverting IF Input (400 $\Omega$ differential nominal impedance between IF <sub>IN+</sub> and IF <sub>IN-</sub> )                                                           |

| C2  | IF <sub>IN+</sub> | Noninverting IF Input (400 $\Omega$ differential nominal impedance between IF <sub>IN+</sub> and IF <sub>IN-</sub> )                                                        |

| C3  | RFOUT             | Upconverter Output Port (interstage node). Can be externally matched to $50\Omega$ .                                                                                        |

| C4  | GND               | Ground Reference for RF                                                                                                                                                     |

### **Detailed Description**

#### Variable-Gain Mixer

The MAX2383 contains a double-balanced Gilbert cell mixer merged with a gain-control circuit, followed by a mixer buffer. The mixer is driven differentially at its IF ports. The LO input for the mixer is conditioned through a low-noise, inductively loaded buffer. The mixer differential output is driven through an on-chip balun into a single-ended common emitter amplifier, which drives the output pin (RFOUT). The mixer buffer is a singleended in/out common emitter stage with inductive degeneration and an external inductive load. Additionally, these circuits are biased from "VCS" generators, designed to produce a low-noise constant degeneration voltage at the user's current source. These bias circuits also provide the control required to selectively power-down the circuit and also provide for gain control and current throttle-back.

#### **PA Driver**

The PA buffer is a single-ended in/out common emitter stage with inductive degeneration and an external inductive load.

#### **Applications Information**

#### **LO Buffer Inputs**

The external LO is interfaced either differentially or single-ended to the differential LO buffer. Those two pins also function as the control inputs for the device. Hence, they are DC-coupled to the chip-control circuitry, and AC-coupled to the LO port. SHDN and LO\_EN

turn off the whole IC when both pins are pulled LOW. LO\_EN helps reduce VCO pulling in gated-transmission mode by providing means to keep the LO buffer on while the upconverter and driver turn on and off. To avoid loading of the LO buffer, connect a  $10k\Omega$  isolation resistor between the LO\_EN/LO+ pin and the LO\_EN logic input, and a  $10k\Omega$  isolation resistor between the SHDN/LO- pin and the SHDN logic input.

#### **Differential IF Inputs**

The MAX2383 has a differential IF input port for interfacing to differential IF filters. The IF pins should be ACcoupled to the IF ports. The typical IF frequency is 380MHz, but the device can operate from 200MHz to 600MHz. The differential impedance between the two IF inputs is approximately  $400\Omega$  in parallel with 1.0pF.

#### Interstage Matching

The mixer buffer drives the following PA driver through an interstage matching network connected between the mixer's RF<sub>OUT</sub> pin and the PA driver's input pin (DRIN). This off-chip matching network, which consists of two series inductors and a parallel capacitor, is designed to achieve better than 25dBc image suppression with no current consumption penalty. The quality factor of this off-chip resonant circuit determines the image suppression level and usable bandwidth from the point of view of passband gain flatness.

#### **PA Driver Output**

The PA driver output, DROUT, is an open-collector output that requires an external inductor to  $V_{CC}$  for proper biasing. The output matching components are chosen

for optimum linearity and return loss. It is important to tune the interstage matching network components along with the driver output matching components, to achieve the desired cascaded ACPR performance from the whole device.

### Layout Issues

For best performance, pay attention to power-supply issues as well as to the layout of the signal lines. The EV kit can be used as a layout example. Ground connections followed by supply bypass are the most important.

#### Power-Supply and SHDN Bypassing

Bypass V<sub>CC</sub> with a 330pF capacitor to GND as close as possible to the V<sub>CC</sub> pin. Use separate vias to the ground plane for each of the bypass capacitors and minimize trace length to reduce inductance. Use three separate vias to the ground plane for each ground pin.

#### **Power-Supply Layout**

To minimize coupling between different sections of the IC, the ideal power-supply layout is a star configuration with a large decoupling capacitor at a central V<sub>CC</sub> node. The V<sub>CC</sub> traces branch out from this central node, each going to a separate V<sub>CC</sub> node in the PC board. At the end of each trace is a bypass capacitor that has low ESR at the RF frequency of operation. This arrangement provides local decoupling at each V<sub>CC</sub> pin. At high frequencies, any signal leaking out of one supply pin sees a relatively high impedance (formed by the V<sub>CC</sub> trace inductance) to the central V<sub>CC</sub> node, and an even higher impedance to ground through the bypass capacitor.

#### Impedance-Matching Network Layout

The DROUT and interstage matching networks are very sensitive to layout-related parasitic. To minimize parasitic inductance, keep all traces short and place components as close as possible to the chip. To minimize parasitic capacitance, minimize the area of the plane.

# **UCSP** Reliability

The chip-scale package (UCSP) represents a unique package that greatly reduces board space compared to other packages. UCSP reliability is integrally linked to the user's assembly methods, circuit board material, and usage environment. The user should closely review these areas when considering use of a UCSP. This form factor may not perform equally to a packaged product through traditional mechanical reliability tests. Performance through Operating Life Test and Moisture Resistance remains uncompromised as it is primarily determined by the wafer-fabrication process.

Mechanical stress performance is a greater consideration for a UCSP. UCSP solder joint contact integrity must be considered since the package is attached through direct solder contact to the user's PC board. Testing done to characterize the UCSP reliability performance shows that it is capable of performing reliably through environmental stresses. Results of environmental stress tests and additional usage data and recommendations are detailed in the UCSP application note, which can be found on Maxim's website, www.maxim-ic.com.

### **Chip Information**

TRANSISTOR COUNT: 998

# **Typical Operating Circuit**

**MAX2383**

## **Package Information**

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to **www.maxim-ic.com/packages**.)

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

\_\_\_\_\_\_Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600

Printed USA

© 2003 Maxim Integrated Products

8

is a registered trademark of Maxim Integrated Products.