This product is obsolete.

This information is available for your convenience only.

For more information on Zarlink's obsolete products and replacement product lists, please visit

http://products.zarlink.com/obsolete\_products/

DS3580-3.2

# **MA5104**

# **RADIATION HARD 4096 x 1 BIT STATIC RAM**

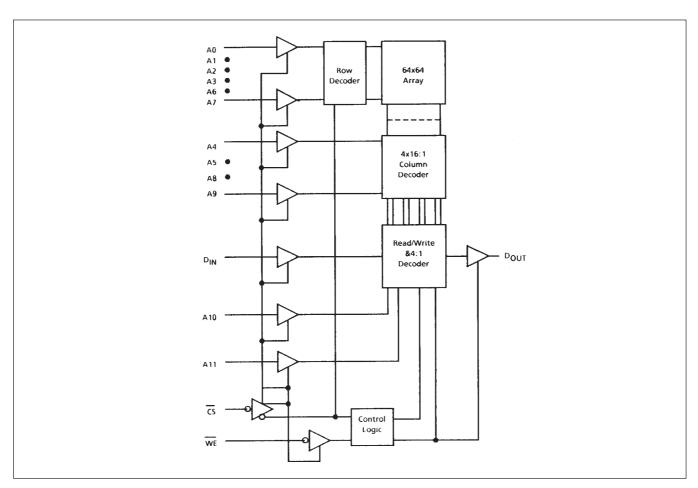

The MA5104 4k Static RAM is configured as 4096 x 1 bits and manufactured using CMOS-SOS high performance, radiation hard,  $3\mu m$  technology.

The device has separate input and output terminals controlled by Chip Select and Write Enable. The design uses a 6 transistor cell and has full static operation with no clock or timing strobe required. Address input buffers are deselected when Chip Select is in the HIGH state.

| Operation Mode | <u>cs</u> | S WE I/O |        | Power |

|----------------|-----------|----------|--------|-------|

| Read           | L         | Н        | D OUT  | ISB1  |

| Write          | L         | L        | D IN   |       |

| Standby        | Н         | Х        | High Z | ISB2  |

Figure 1: Truth Table

#### **FEATURES**

- 3µm CMOS-SOS Technology

- Latch-up Free

- Fast Access Time 90ns Typical

- Total Dose 10<sup>6</sup> Rad(Si)

- Transient Upset >1010 Rad(Si)/sec

- SEU <10<sup>-10</sup> Errors/bitday

- Single 5V Supply

- Three State Output

- Low Standby Current 10µA Typical

- -55°C to +125°C Operation

- All Inputs and Outputs Fully TTL or CMOS Compatible

- Fully Static Operation

Figure 2: Block Diagram

#### **CHARACTERISTICS AND RATINGS**

| Symbol          | Parameter             | Min. | Max.                 | Units |

|-----------------|-----------------------|------|----------------------|-------|

| V <sub>CC</sub> | Supply Voltage        | -0.5 | 7                    | V     |

| VI              | Input Voltage         | -0.3 | V <sub>DD</sub> +0.3 | V     |

| T <sub>A</sub>  | Operating Temperature | -55  | 125                  | °C    |

| Ts              | Storage Temperature   | -65  | 150                  | °C    |

Stresses above those listed may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these conditions, or at any other condition above those indicated in the operations section of this specification, is not Implied Exposure to absolute maxlmum rating conditions for extended perlods may affect device reliability.

Figure 3: Absolute Maximum Ratings

#### Notes for Tables 4 and 5:

- 1. Characteristics apply to pre radiation at  $T_A$  = -55°C to +125°C with  $V_{DD}$  = 5V  $\pm 10\%$  and to post 100k Rad(Si) total dose radiation at  $T_A = 25^{\circ}\text{C}$  with  $V_{DD} = 5\text{V} \pm 10\%$  (characteristics at higher radiation levels available on request). 2. Worst case at  $T_A = +125^{\circ}\text{C}$ , guaranteed but not tested at  $T_A = -55^{\circ}\text{C}$ .

- GROUP A SUBGROUPS 1, 2, 3.

| Symbol           | Parameter                       | Conditions                                         | Min.               | Тур. | Max.            | Units |

|------------------|---------------------------------|----------------------------------------------------|--------------------|------|-----------------|-------|

| V <sub>DD</sub>  | Supply voltage                  | -                                                  | 4.5                | 5.0  | 5.5             | V     |

| V <sub>IH</sub>  | Input High Voltage              | -                                                  | V <sub>DD</sub> /2 | -    | V <sub>DD</sub> | V     |

| V <sub>IL</sub>  | Input Low Voltage               | -                                                  | V <sub>SS</sub>    | -    | 0.8             | V     |

| V <sub>OH</sub>  | Output High Voltage             | I <sub>OH1</sub> = -1mA                            | 2.4                | -    | -               | V     |

| V <sub>OL</sub>  | Output Low Voltage              | I <sub>OL</sub> = 2mA                              | -                  | -    | 0.4             | V     |

| ILI              | Input Leakage Current (note 2)  | All inputs except <u>CS</u>                        | -                  | -    | ±10             | μΑ    |

| I <sub>LO</sub>  | Output Leakage Current (note 2) | Output disabled, $V_{OUT} = V_{SS}$ or $V_{DD}$    | -                  | -    | ±20             | μΑ    |

| I <sub>PUI</sub> | Input Pull-Up Current           | $V_{IN} = V_{SS}$ on <u>CS</u> input only          | -                  | -    | -100            | μΑ    |

| I <sub>PDI</sub> | Input Leakage Current           | $V_{IN} = V_{SS}$ on <u>CS</u> input only          | -                  | -    | 5               | μΑ    |

| I <sub>DD</sub>  | Power Supply Current            | f <sub>RC</sub> = 1MHz, <u>CS</u> = 50% mark:space | -                  | 12   | 16              | mA    |

| I <sub>SB1</sub> | Selected Supply Current         | <u>CS</u> = V <sub>SS</sub>                        | -                  | 25   | 35              | mA    |

| I <sub>SB2</sub> | Standby Supply Current          | Chip disabled                                      | -                  | 50   | 3000            | μΑ    |

Figure 4: Electrical Characteristics

| Symbol           | Parameter                          | Conditions                               | Min. | Тур. | Max. | Units |

|------------------|------------------------------------|------------------------------------------|------|------|------|-------|

| $V_{DR}$         | V <sub>CC</sub> for Data Retention | $\underline{CS} = V_{DR}$                | 2.0  | -    | -    | V     |

| I <sub>DDR</sub> | Data Retention Current             | $\underline{CS} = V_{DR}, V_{DR} = 2.0V$ | -    | 30   | 2000 | μΑ    |

Figure 5: Data Retention Characteristics

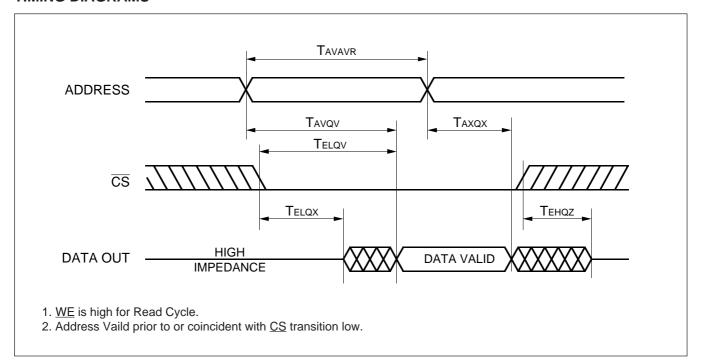

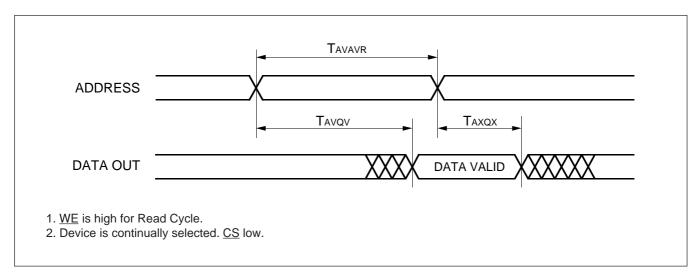

#### **AC CHARACTERISTICS**

Conditions of Test for Tables 5 and 6:

- 1. Input pulse =  $V_{ss}$  to 3.0V. 2. Times measurement reference level = 1.5V.

- 3. Transition is measured at  $\pm 500 \text{mV}$  from steady state.

- 4. This parameter is sampled and not 100% tested.

#### Notes for Tables 6 and 7:

Characteristics apply to pre-radiation at  $T_A$  = -55°C to +125°C with  $V_{DD}$  = 5V±10% and to post 100k Rad(Si) total dose radiation at  $T_A$  = 25°C with  $V_{DD}$  = 5V ±10%. GROUP A SUBGROUPS 9, 10, 11.

| Symbol                | Parameter                       |     | Max | Units |

|-----------------------|---------------------------------|-----|-----|-------|

| T <sub>AVAVR</sub>    | Read Cycle Time                 | 135 | -   | ns    |

| T <sub>AVQV</sub>     | Address Access Time             |     | 135 | ns    |

| T <sub>ELQV</sub>     | Chip Select to Output Valid     |     | 135 | ns    |

| T <sub>ELQX</sub> (4) | Chip Select to Output Active    |     | -   | ns    |

| T <sub>ELQZ</sub> (4) | Chip Select to Output Tri State |     | 50  | ns    |

| T <sub>AXQX</sub>     | Output Hold from Address Change | 10  | -   | ns    |

Figure 6: Read Cycle AC Electrical Characteristics

| Symbol                | Parameter                        |     | Max | Units |

|-----------------------|----------------------------------|-----|-----|-------|

| T <sub>AVAVW</sub>    | Write Cycle Time                 | 135 | -   | ns    |

| T <sub>AVWL</sub>     | Address Set Up Time              | 10  | -   | ns    |

| T <sub>wtwh</sub>     | Write Pulse Width                | 50  | -   | ns    |

| T <sub>whav</sub>     | Write Recovery Time              | 5   | -   | ns    |

| T <sub>DVWH</sub>     | Data Set Up Time                 |     | -   | ns    |

| T <sub>NHDX</sub>     | Data Hold Time                   |     | -   | ns    |

| T <sub>WLQZ</sub> (4) | Write Enable to Output Tri State | 10  | 50  | ns    |

| T <sub>ELWL</sub>     | Chip Selection to Write Low      | 25  | -   | ns    |

| T <sub>ELWH</sub>     | Chip Selection to End of Write   |     | -   | ns    |

| T <sub>AVWH</sub>     | Address Valid to End of Write    |     | -   | ns    |

| T <sub>WHQX</sub> (4) | Output Active from End to Write  | 5   | -   | ns    |

Figure 7: Write Cycle AC Electrical Characteristics

| Symbol           | Parameter          | Conditions          | Min. | Тур. | Max. | Units |

|------------------|--------------------|---------------------|------|------|------|-------|

| C <sub>IN</sub>  | Input Capacitance  | V <sub>1</sub> = 0V | -    | 6    | 10   | pF    |

| C <sub>OUT</sub> | Output Capacitance | V <sub>0</sub> = 0V | -    | 8    | 12   | pF    |

Note:  $T_A = 25$ °C and f = 1MHz. Data obtained by characterisation or analysis; not routinely measured.

Figure 8: Capacitance

| arameter           | Conditions                                                                                     |

|--------------------|------------------------------------------------------------------------------------------------|

| asic Functionality | $V_{DD} = 4.5V - 5.5V$ , FREQ = 1MHz                                                           |

|                    | $V_{_{ L}} = V_{_{SS}}, \ V_{_{ H}} = V_{_{DD}}, \ V_{_{OL}} \le 1.5 V, \ V_{_{OH}} \ge 1.5 V$ |

|                    | TEMP = -55°C to +125°C, GPS PATTERN SET                                                        |

|                    | GROUP A SUBGROUPS 7, 8A, 8B                                                                    |

| _                  |                                                                                                |

Figure 9: Functionality

| Subgroup | Definition                                                      |  |  |  |  |

|----------|-----------------------------------------------------------------|--|--|--|--|

| 1        | Static characteristics specified in Tables 4 and 5 at +25°C     |  |  |  |  |

| 2        | Static characteristics specified in Tables 4 and 5 at +125°C    |  |  |  |  |

| 3        | Static characteristics specified in Tables 4 and 5 at -55°C     |  |  |  |  |

| 7        | Functional characteristics specified in Table 9 at +25°C        |  |  |  |  |

| 8A       | Functional characteristics specified in Table 9 at +125°C       |  |  |  |  |

| 8B       | Functional characteristics specified in Table 9 at -55°C        |  |  |  |  |

| 9        | Switching characteristics specified in Tables 6 and 7 at +25°C  |  |  |  |  |

| 10       | switching characteristics specified in Tables 6 and 7 at +125°C |  |  |  |  |

| 11       | Switching characteristics specified in Tables 6 and 7 at -55°C  |  |  |  |  |

Figure 10: Definition of Subgroups

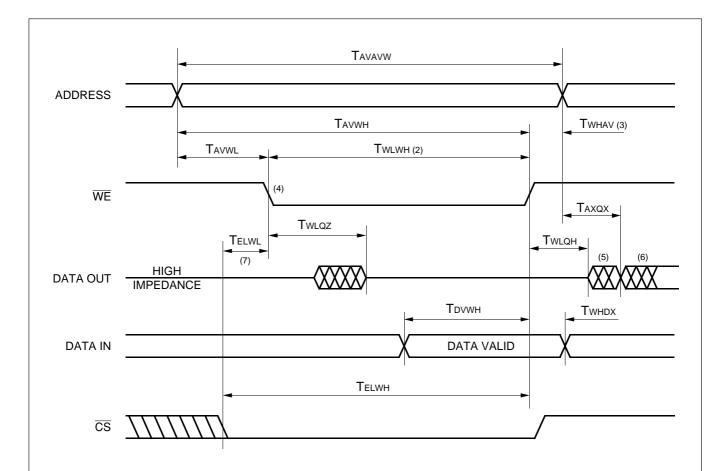

# **TIMING DIAGRAMS**

Figure 11a: Read Cycle 1

Figure 11b: Read Cycle 2

- 1. WE must be high during all address transitions.

- 2. A write occurs during the overlap (T $_{WLWH}$ ) of a low  $\underline{CS}$ , a high CE and a low  $\underline{WE}$ .

- 3.  $T_{WHAV}$  is measured from either  $\underline{CS}$  or  $\underline{WE}$  going high or CE going low, whichever is the earlier, to the end of the write cycle.

- 4. If the  $\underline{CS}$  low transition occurs simultaneously with, or after, the  $\underline{WE}$  low transition, the output remains in the high impedance state.

- 5. DATA OUT is the write data of the current cycle, if selected.

- 6. DATA OUT is the read data of the next address, if selected.

- 7.  $T_{\text{ELWL}}$  must be met to prevent memory corruption.

Figure 12: Write Cycle

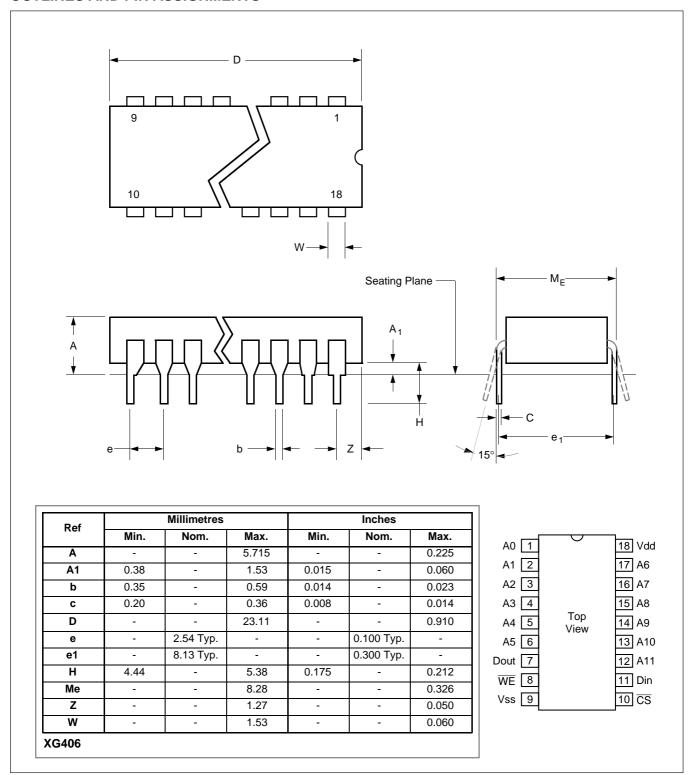

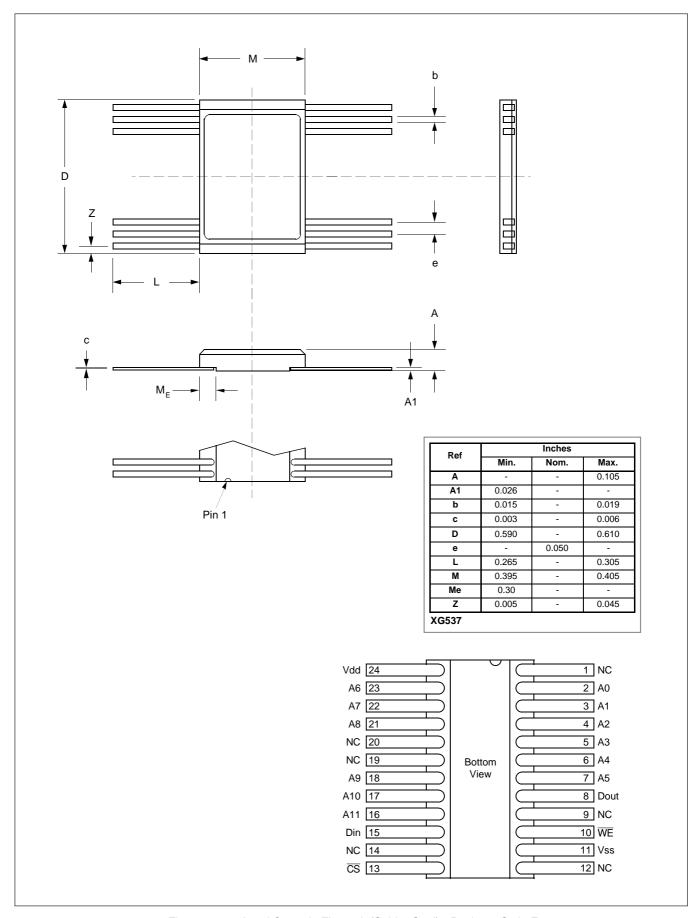

# **OUTLINES AND PIN ASSIGNMENTS**

Figure 13: 18-Lead Ceramic DIL (Solder Seal) - Package Style C

Figure 14: 24-Lead Ceramic Flatpack (Solder Seal) - Package Style F

|          | Packag | e Option |        | Burnin   |          |         |           |

|----------|--------|----------|--------|----------|----------|---------|-----------|

| Function | F      | С        | Via    | Static 1 | Static 2 | Dynamic | Radiation |

| A0       | 2      | 1        | R      | 0V       | 5V       | F0      | 5V        |

| A1       | 3      | 2        | R      | 0V       | 5V       | F1      | 5V        |

| A2       | 4      | 3        | R      | ٥V       | 5V       | F2      | 5V        |

| A3       | 5      | 4        | R      | 0V       | 5V       | F3      | 5V        |

| A4       | 6      | 5        | R      | 0V       | 5V       | F4      | 5V        |

| A5       | 7      | 6        | R      | 0V       | 5V       | F5      | 5V        |

| DOUT     | 8      | 7        | R      | 0V       | 5V       | LOAD    | 5V        |

| WEB      | 10     | 8        | R      | 0V       | 5V       | F12     | 5V        |

| VSS      | 11     | 9        | Direct | 0V       | 0V       | 0V      | 0V        |

| CSB      | 13     | 10       | R      | 0V       | 5V       | 0V      | 5V        |

| DIN      | 15     | 11       | R      | 0V       | 5V       | F13     | 5V        |

| A11      | 16     | 12       | R      | 0V       | 5V       | F11     | 5V        |

| A10      | 17     | 13       | R      | 0V       | 5V       | F10     | 5V        |

| A9       | 18     | 14       | R      | 0V       | 5V       | F9      | 5V        |

| A8       | 21     | 15       | R      | 0V       | 5V       | F8      | 5V        |

| A7       | 22     | 16       | R      | 0V       | 5V       | F7      | 5V        |

| A6       | 23     | 17       | R      | 0V       | 5V       | F6      | 5V        |

| VDD      | 24     | 18       | Direct | 5V       | 5V       | 5V      | 5V        |

<sup>1.</sup> F0=150KHz, F1=F0/2, F2=F0/4, F3=F0/8 etc.

Figure 15: Burnin and Radiation Configuration

<sup>2.</sup> Burnin R=1k

<sup>3.</sup> Radiation R=10k

#### **RADIATION TOLERANCE**

#### **Total Dose Radiation Testing**

For product procured to guaranteed total dose radiation levels, each wafer lot will be approved when all sample devices from each lot pass the total dose radiation test.

The sample devices will be subjected to the total dose radiation level (Cobalt-60 Source), defined by the ordering code, and must continue to meet the electrical parameters specified in the data sheet. Electrical tests, pre and post irradiation, will be read and recorded.

GEC Plessey Semiconductors can provide radiation testing compliant with MIL-STD-883 test method 1019, Ionizing Radiation (Total Dose).

| Total Dose (Function to specification)*      | 1x10 <sup>5</sup> Rad(Si)             |

|----------------------------------------------|---------------------------------------|

| Transient Upset (Stored data loss)           | 5x10 <sup>10</sup> Rad(Si)/sec        |

| Transient Upset (Survivability)              | >1x10 <sup>12</sup> Rad(Si)/sec       |

| Neutron Hardness (Function to specification) | >1x10 <sup>15</sup> n/cm <sup>2</sup> |

| Single Event Upset**                         | 3.4x10 <sup>-9</sup> Errors/bit day   |

| Latch Up                                     | Not possible                          |

<sup>\*</sup> Other total dose radiation levels available on request

Figure 16: Radiation Hardness Parameters

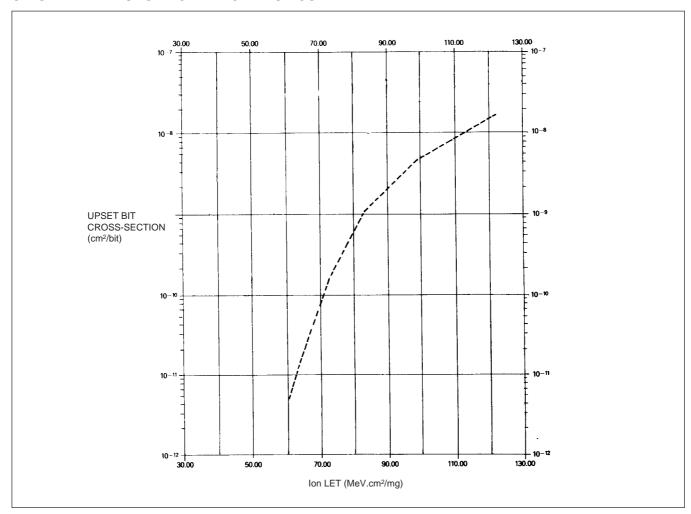

# SINGLE EVENT UPSET CHARACTERISTICS

Figure 17: Typical Per-Bit Upset Cross-Section vs Ion LET

<sup>\*\*</sup> Worst case galactic cosmic ray upset - interplanetary/high altitude orbit

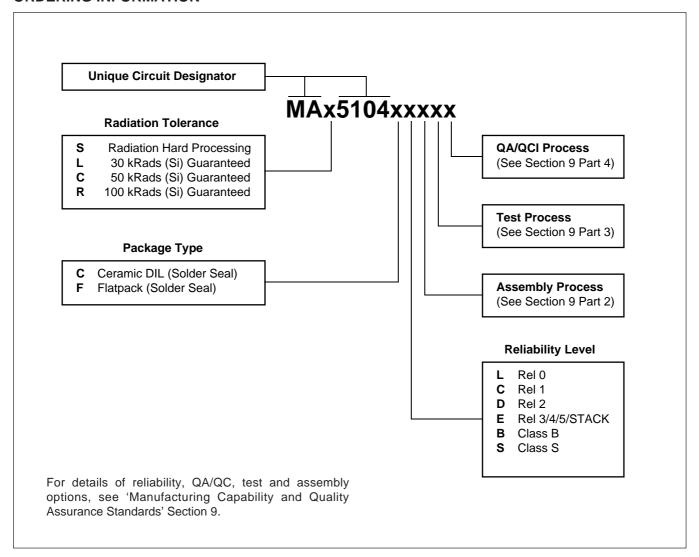

#### ORDERING INFORMATION

**HEADQUARTERS OPERATIONS**

#### **GEC PLESSEY SEMICONDUCTORS**

Cheney Manor, Swindon, Wiltshire, SN2 2QW, United Kingdom.

Tel: (01793) 518000 Fax: (01793) 518411

## **GEC PLESSEY SEMICONDUCTORS**

P.O. Box 660017,

1500 Green Hills Road, Scotts Valley, California 95067-0017, United States of America.

Tel: (408) 438 2900 Fax: (408) 438 5576

#### CUSTOMER SERVICE CENTRES

- FRANCE & BENELUX Les Ulis Cedex Tel: (1) 64 46 23 45 Fax: (1) 64 46 06 07

- GERMANY Munich Tel: (089) 3609 06-0 Fax: (089) 3609 06-55

- ITALY Milan Tel: (02) 66040867 Fax: (02) 66040993

- JAPAN Tokyo Tel: (03) 5276-5501 Fax: (03) 5276-5510

- NORTH AMERICA Scotts Valley, USA Tel: (408) 438 2900 Fax: (408) 438 7023

- SOUTH EAST ASIA Singapore Tel: (65) 3827708 Fax: (65) 3828872

- SWEDEN Stockholm Tel: 46 8 702 97 70 Fax: 46 8 640 47 36

- TAIWAN, ROC Taipei Tel: 886 2 5461260 Fax: 886 2 7190260

- UK, EIRE, DENMARK, FINLAND & NORWAY Swindon, UK Tel: (01793) 518527/518566 Fax: (01793) 518582

These are supported by Agents and Distributors in major countries world-wide.

© GEC Plessey Semiconductors 1995 Publication No. DS3580-3.2 April 1995

TECHNICAL DOCUMENTATION - NOT FOR RESALE. PRINTED IN UNITED KINGDOM.

This publication is issued to provide information only which (unless agreed by the Company in writing) may not be used, applied or reproduced for any purpose nor form part of any order or contract nor to be regarded as a representation relating to the products or services concerned. No warranty or guarantee express or implied is made regarding the capability, performance or suitability of any product or service. Information concerning possible methods of use is provided as a guide only and does not constitute any guarantee that such methods of use will be satisfactory in a specific piece of equipment. It is the user's responsibility to fully determine the performance and suitability of any equipment using such information and to ensure that any publication or data used is up to date and has not been superseded. These products are not suitable for use in any medical products whose failure to perform may result in significant injury or death to the user. All products and services provided subject to the Company's conditions of sale, which are available on request.