# PRELIMINARY M30240

# M30240 Group Specification

| Description                                      |         |

|--------------------------------------------------|---------|

| Features                                         | 1-3     |

| Applications                                     | 1-3     |

| Pin Configuration                                | 1-4     |

| Block Diagram                                    |         |

| Performance outline                              | 1-6     |

| Pin Description                                  | 1-8     |

| Overview                                         |         |

| Operation of Functional Blocks                   | 1-11    |

| Central Processing Unit (CPU)                    | 1-11    |

| Processor Mode                                   | 1-14    |

| Memory                                           |         |

| SFR MAP                                          | 1-16    |

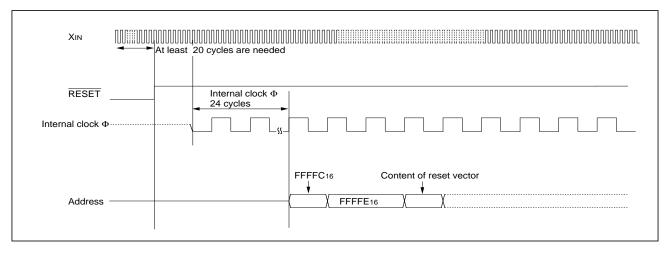

| Reset                                            | 1-22    |

| Software Reset                                   | 1-23    |

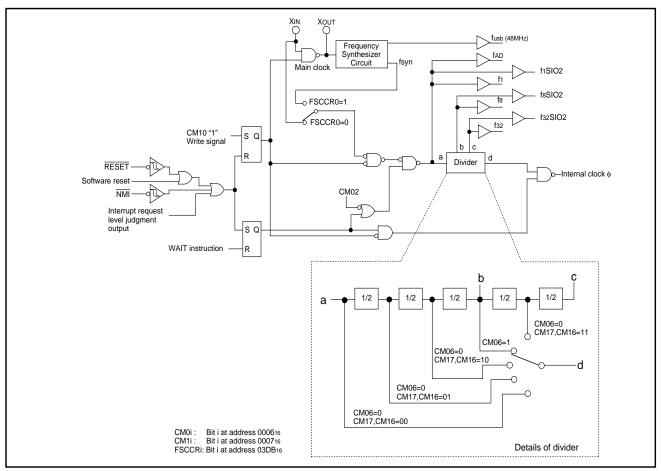

| Clock-Generating Circuit                         | 1-23    |

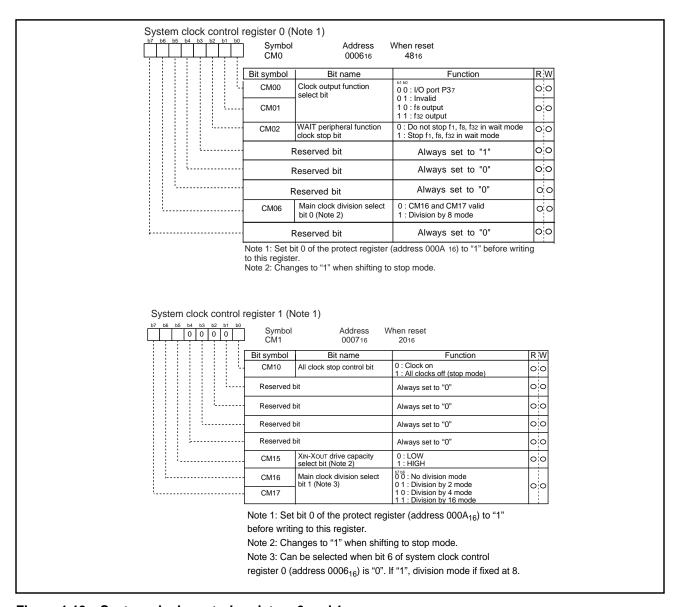

| Clock Control                                    | 1-24    |

| Stop Mode                                        |         |

| Wait Mode                                        |         |

| Status Transition Of the Internal Clock $\Phi$ . | 1-26    |

| Power Control                                    | 1-27    |

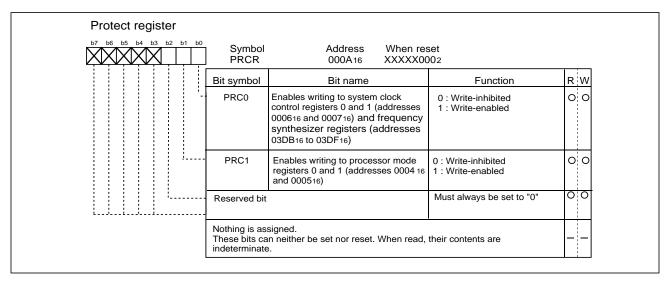

| Protection                                       | 1-28    |

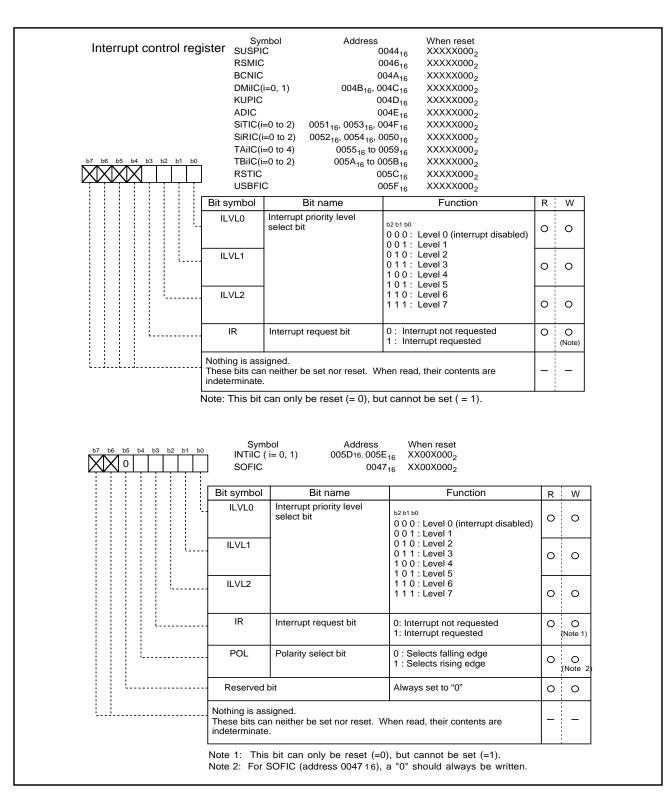

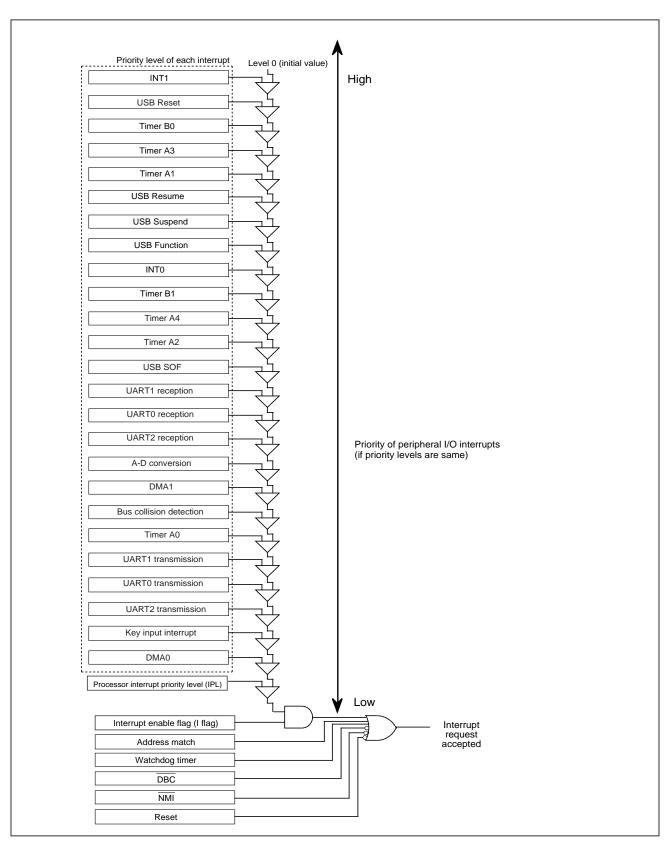

| Interrupts                                       | 1-29    |

| NMI Interrupt                                    | 1-35    |

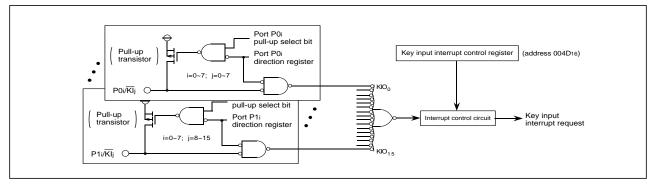

| Key-Input Interrupt                              | 1-36    |

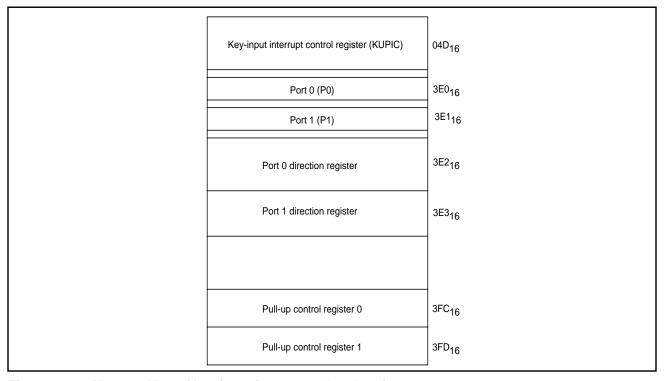

| Address Match Interrupt                          | 1-38    |

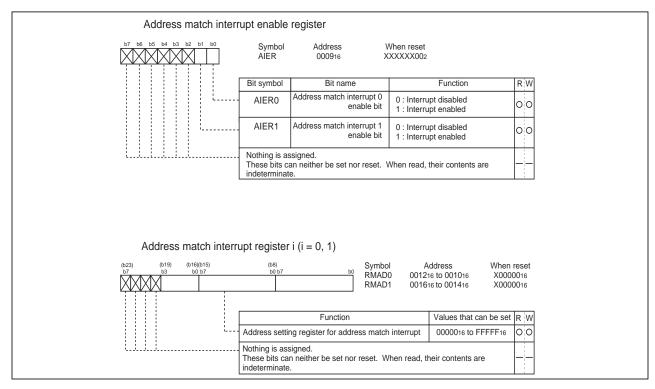

| Watchdog Timer                                   |         |

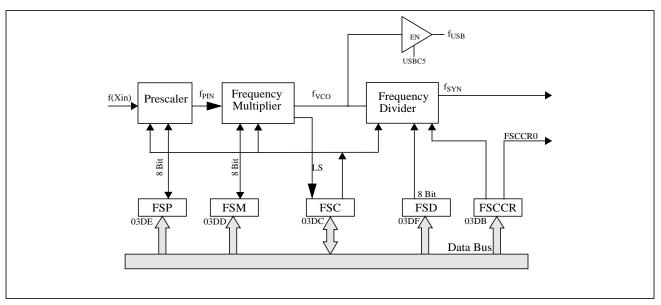

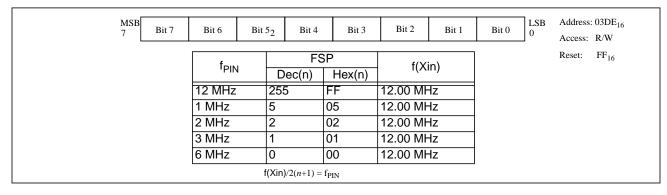

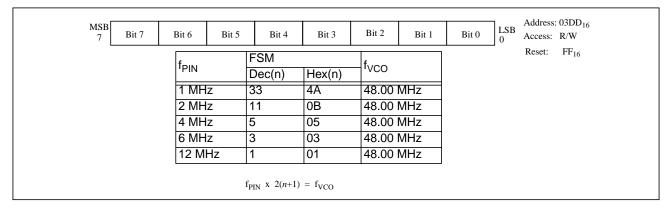

| Frequency Synthesizer Circuit                    | 1-41    |

| Universal Serial Bus                             |         |

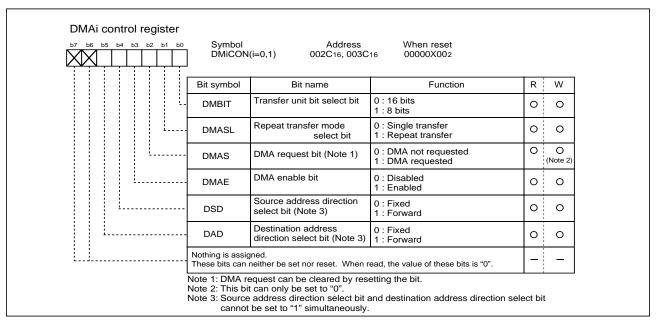

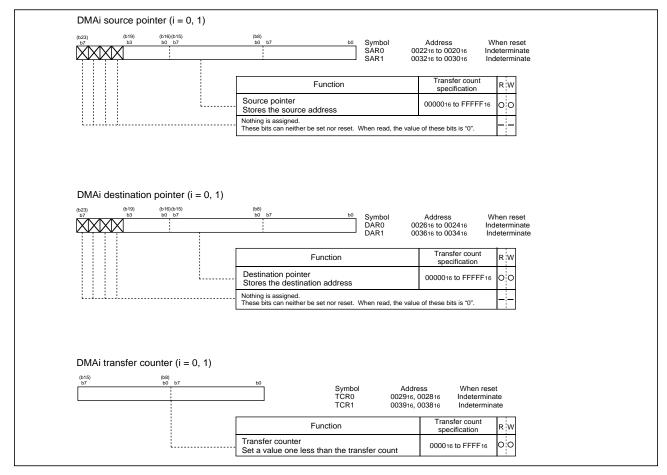

| DMAC                                             | 1-63    |

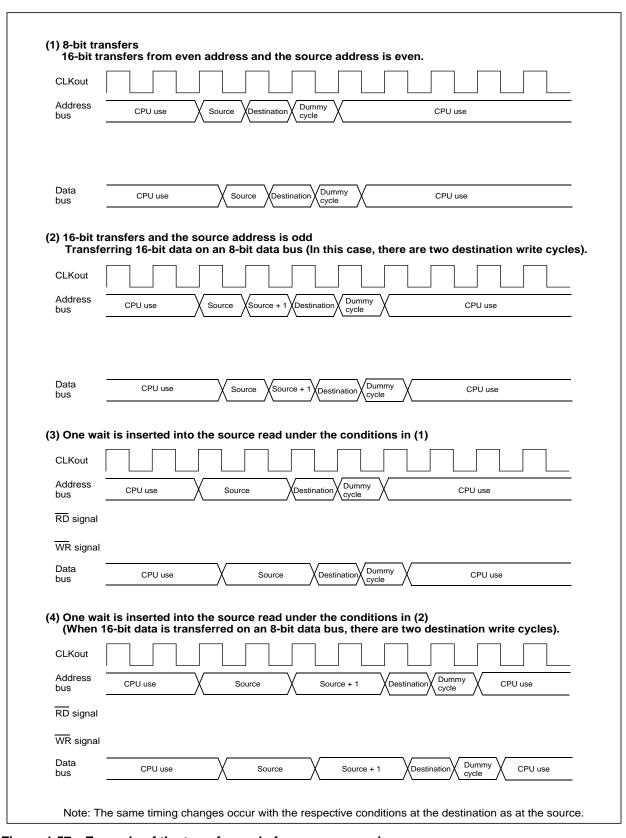

| Timers                                           | 1-68    |

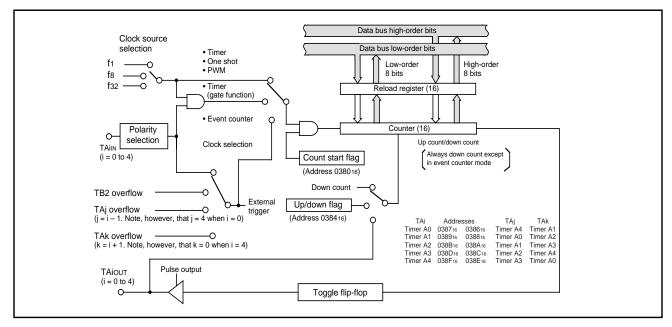

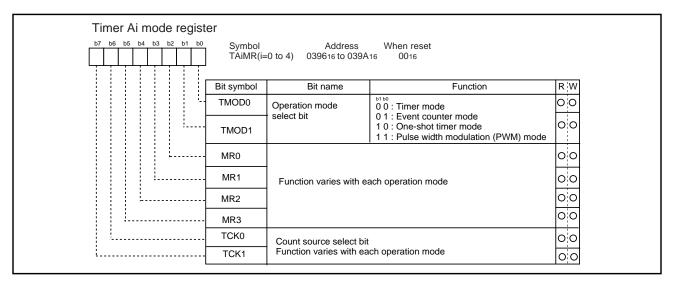

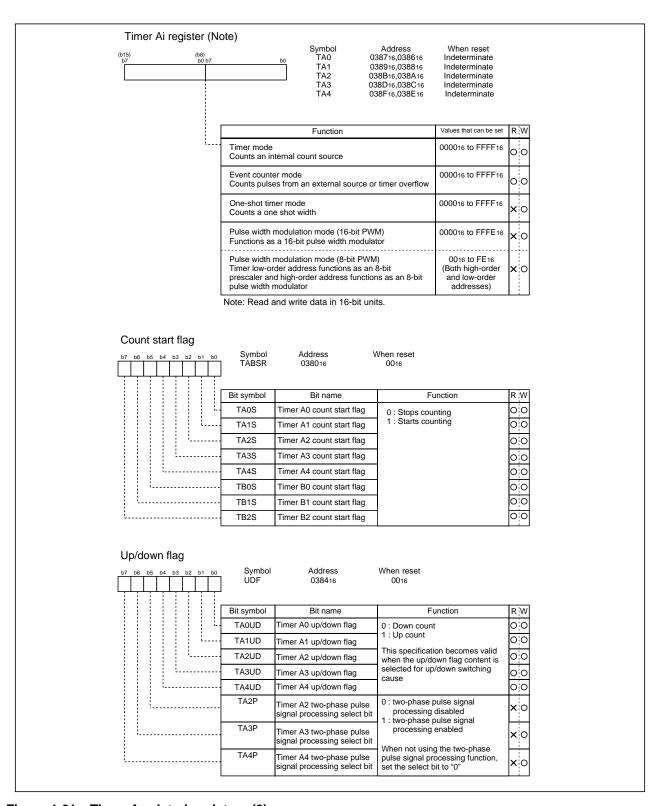

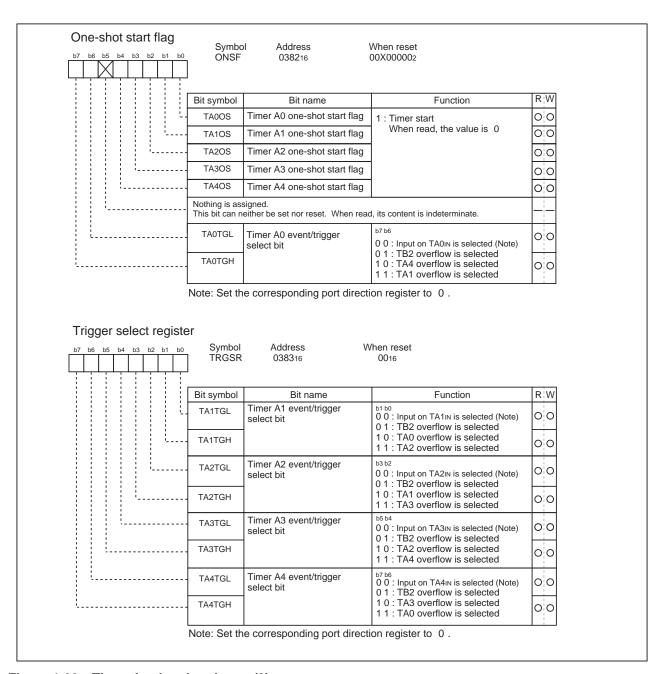

| Timer A                                          | 1-69    |

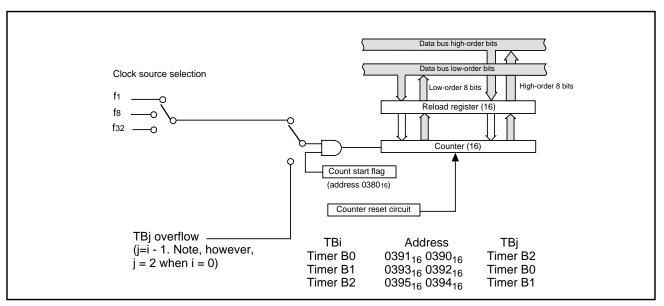

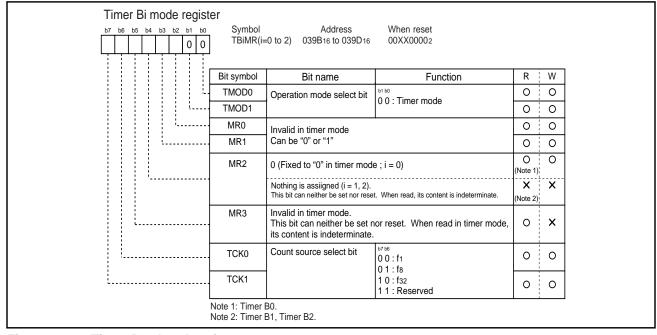

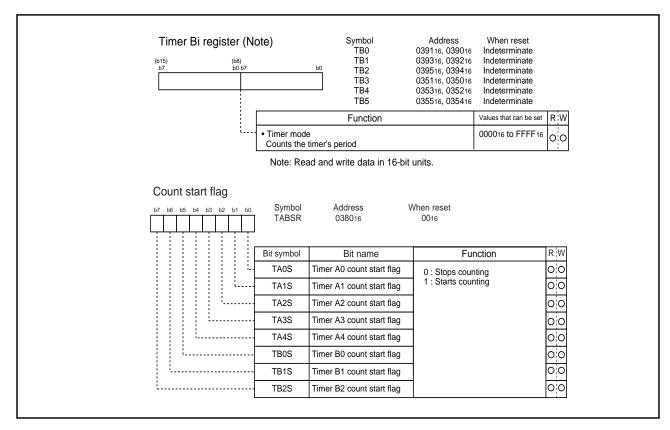

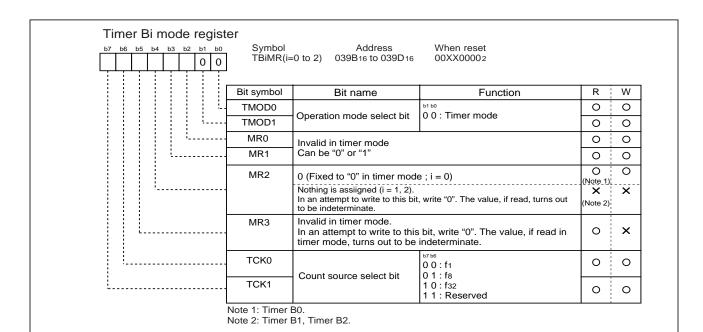

| Timer B                                          |         |

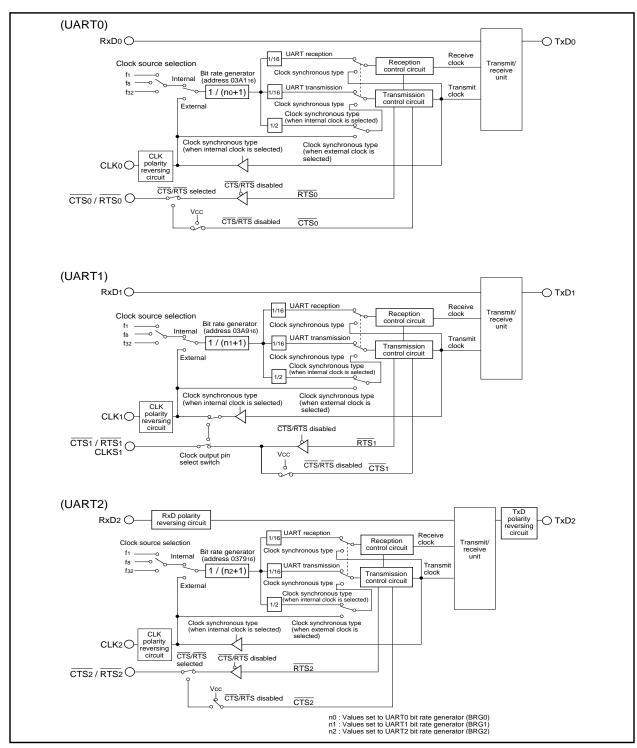

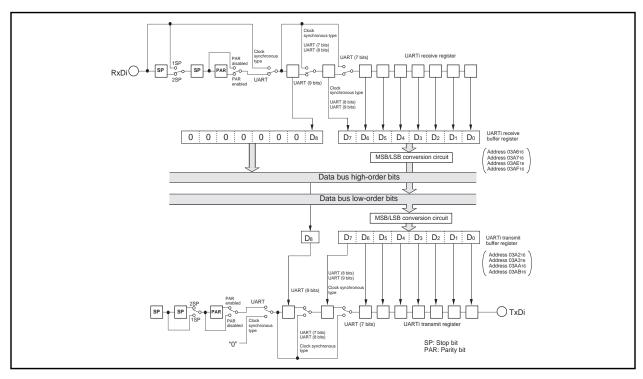

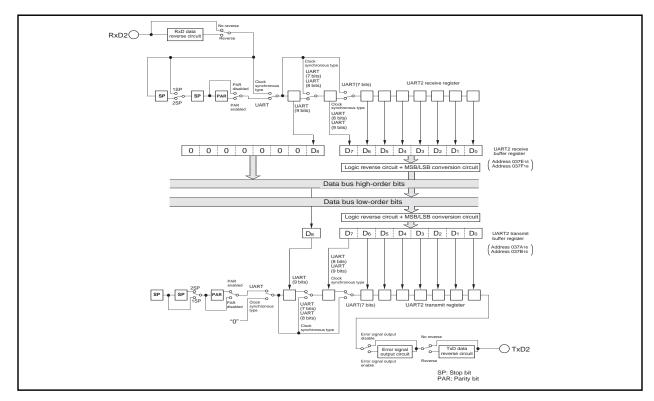

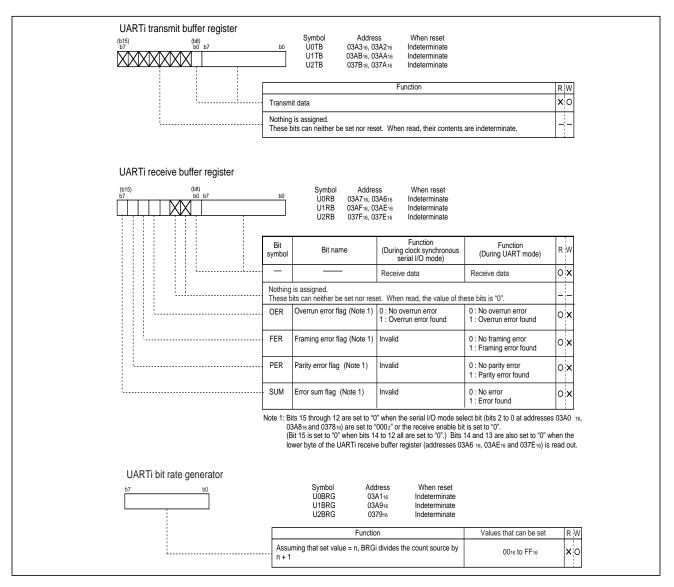

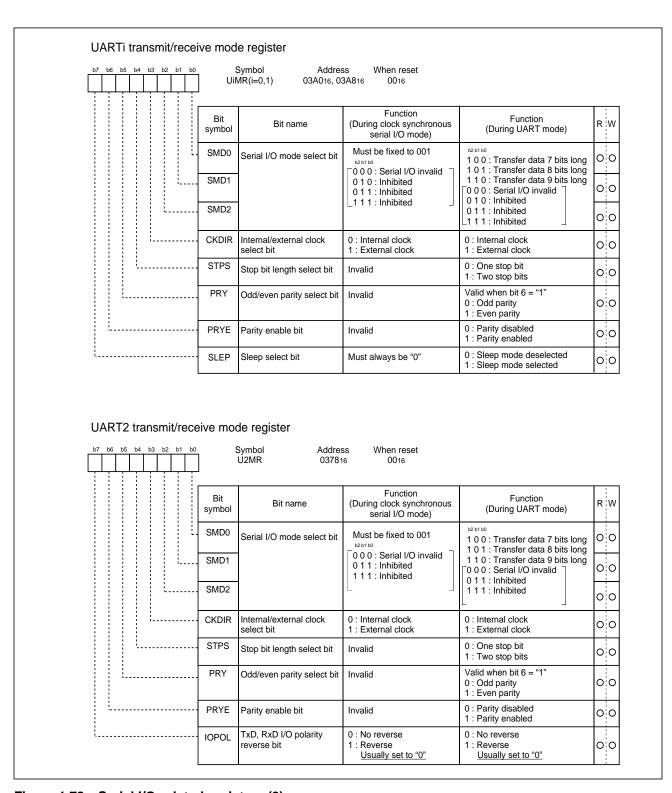

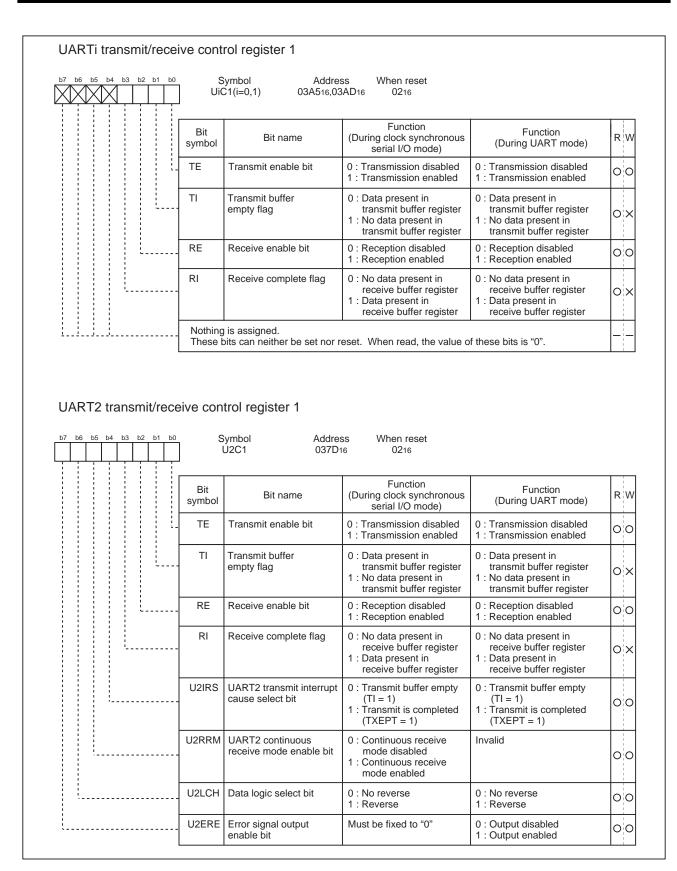

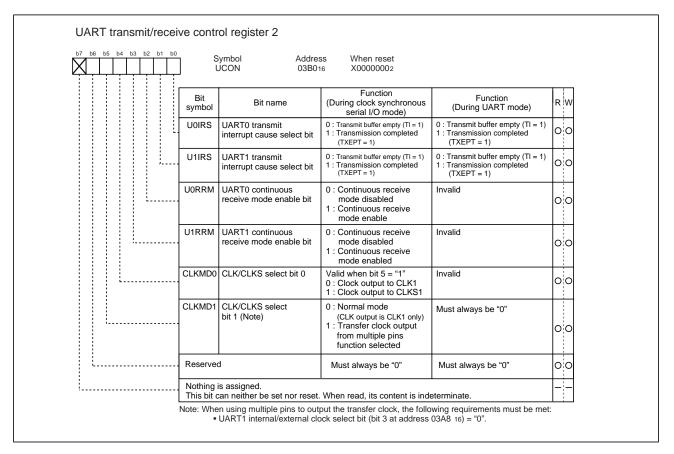

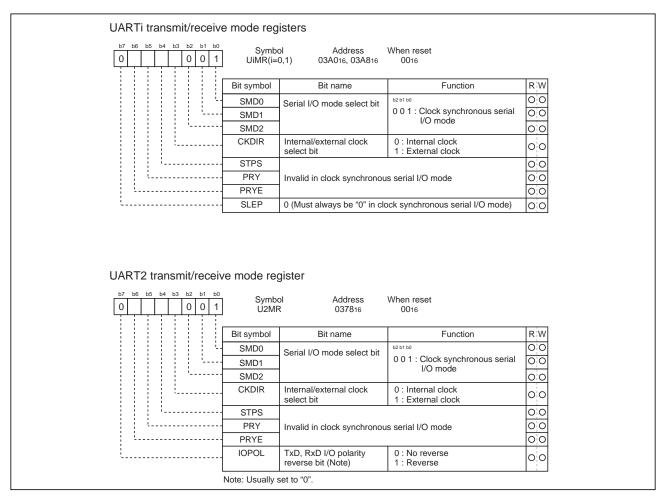

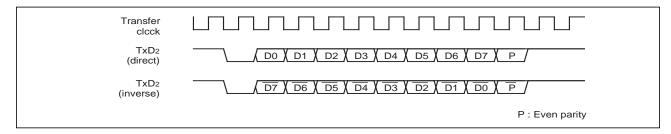

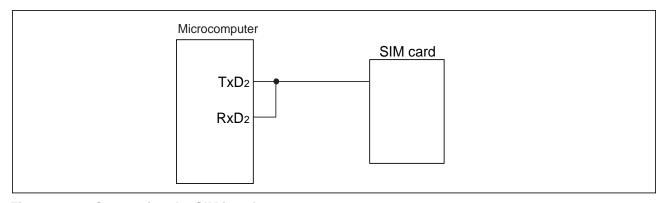

| UART0 through UART2                              | 1-83    |

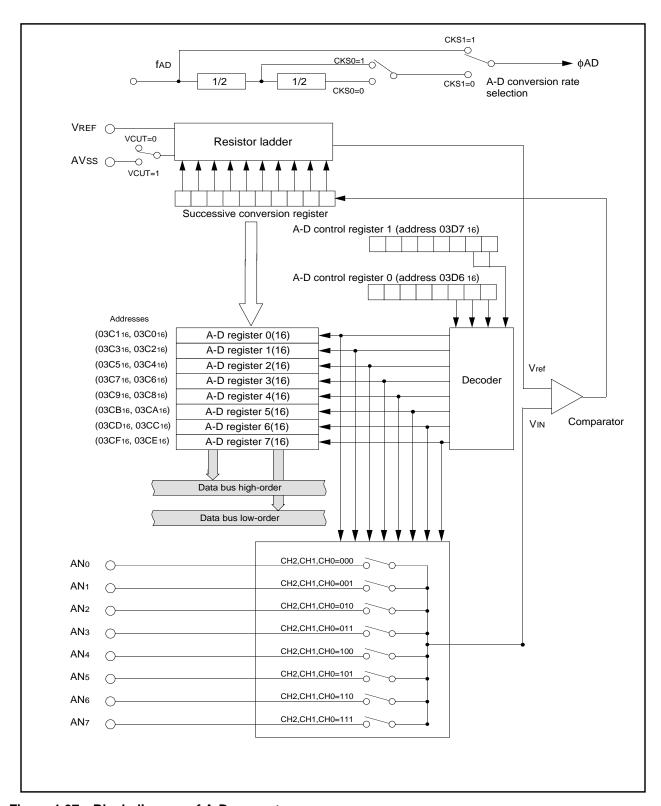

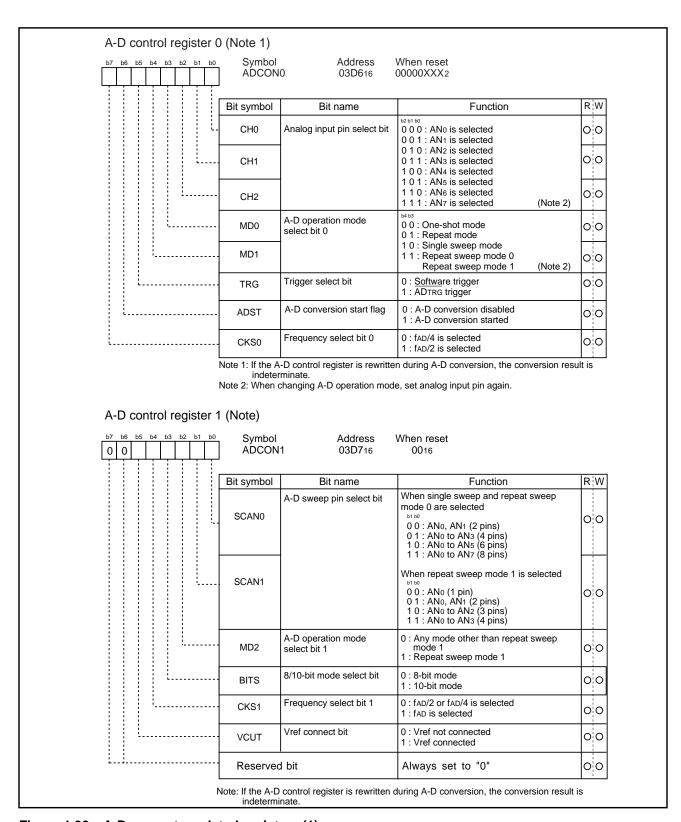

| A-D Converter                                    |         |

| CRC Calculation Circuit                          |         |

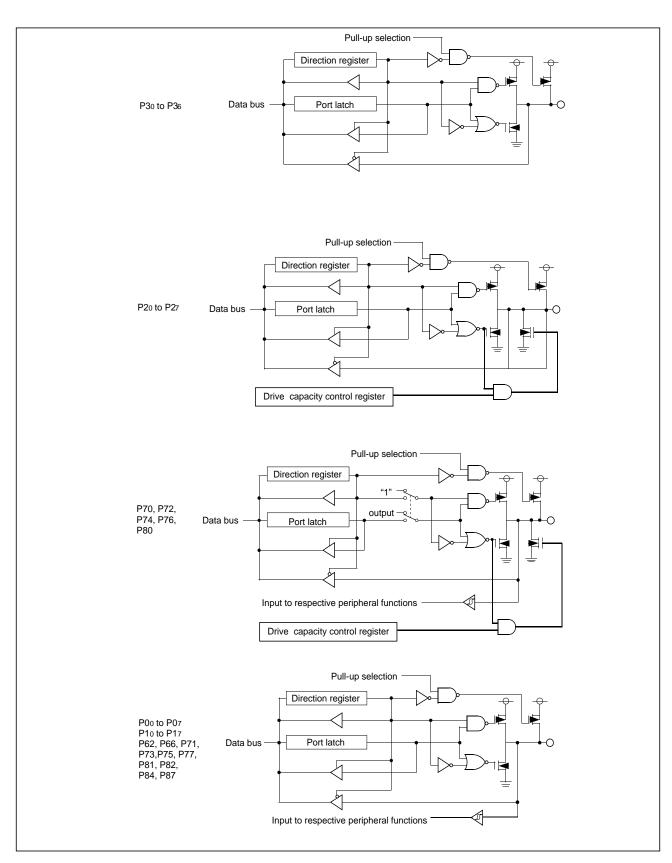

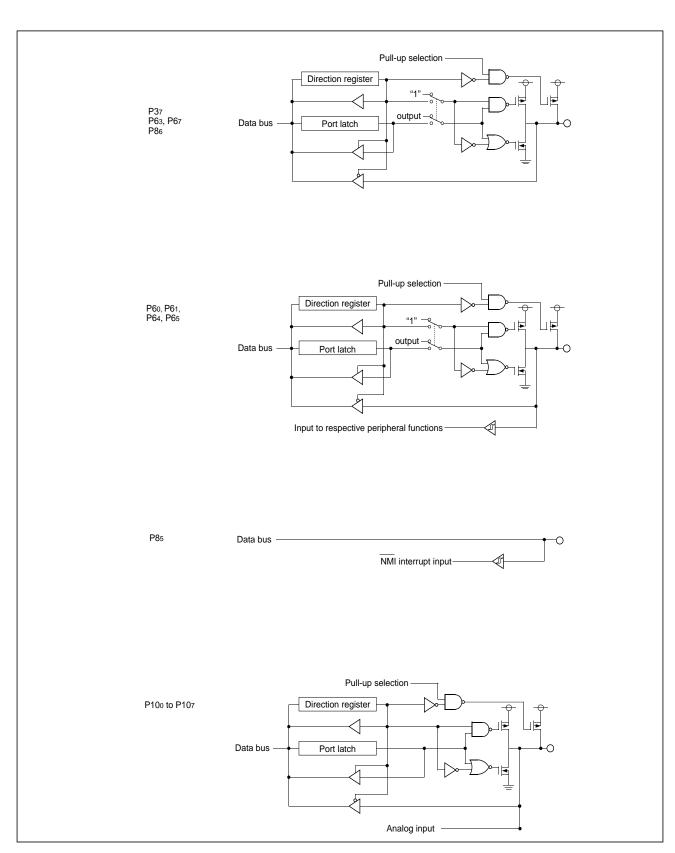

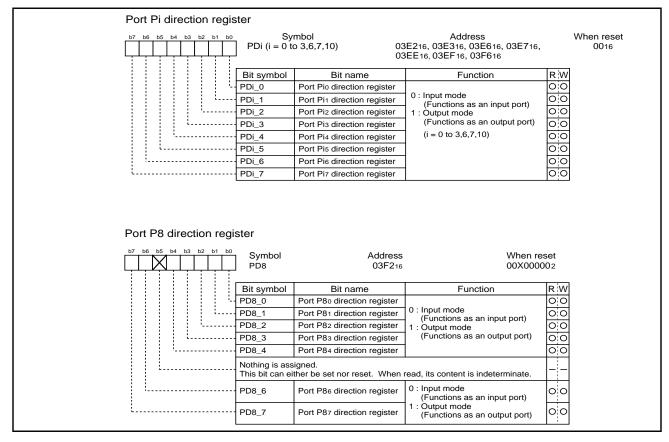

| Programmable I/O Ports                           |         |

| Usage                                            | . 1-124 |

| Usage Precautions                                | 1-124   |

| Specifications                                   | . 1-128 |

| Electrical                                       | 1-128   |

| Timing                                           | 1-130   |

| Timing Diagrams- Peripheral/interrupt            |         |

| Applications                                     |         |

| Frequency Synthesizer Interface                  |         |

| and DC-DC Converter                              |         |

| Attach/Detach Function                           |         |

| Low Pass Filter Network                          |         |

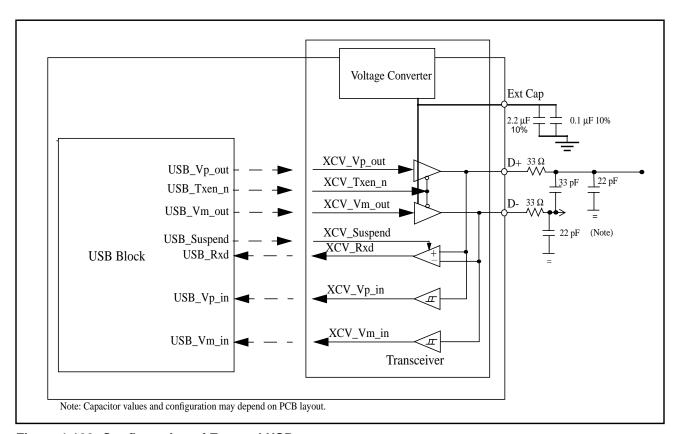

| USB Transceiver                                  |         |

| Programming Notes                                | 1-141   |

**Features**

# 1.0 Description

The M30240 group is a 16-bit microcomputer based on the M16C family core technology. They are single-chip USB peripheral microcontrollers based on the Universal Serial Bus (USB) Version 1.1 specification. They are packaged in an 80-pin, molded plastic QFP. These single-chip microcontrollers operate using sophisticated instructions featuring a high level of instruction efficiency, making them capable of executing instructions at high speed. They also feature a built-in multiplier and DMAC, making them ideal for controlling office communications, industrial equipment, and other high-speed processing applications.

#### 1.1 Features

|   |                                                   | 16-bit (including a hardware multiplier)                                    |

|---|---------------------------------------------------|-----------------------------------------------------------------------------|

|   | Number of instructions                            |                                                                             |

|   | Shortest instruction execution time USB Features: |                                                                             |

| ٠ | USB realures                                      | FIFO Sizes (endpoints 0-4):32,128, 32, 32                                   |

|   |                                                   | Conforms to USB V1.1 Specification                                          |

| • | USB Transceiver                                   | Conforms to USB V1.1 Specification-Internal Vref                            |

|   | Frequency Synthesizer                             |                                                                             |

|   | Memory capacity (mask device):                    |                                                                             |

| • | Memory capacity (OTP device):                     | PROM (128K) / RAM (5K)                                                      |

| • | Supply Voltage                                    | 4.1 to 5.25V f(X <sub>IN</sub> )=12MHz)                                     |

| • | Interrupts                                        | 21 internal and 4 external interrupt sources,                               |

|   |                                                   | 4 software interrupt sources; 7 levels (including key input interrupt X 16) |

| • | Multifunction timer                               | 5 X 16-bit, w/integrated 20mA (peak) PWM outputs                            |

| • | General purpose timer                             | 3 X 16-bit, internal interrupt only                                         |

| • | UART                                              | ·                                                                           |

|   |                                                   | Configurable for synchronous or asynchronous mode                           |

|   | DMAC                                              | · · · · · · · · · · · · · · · · · · ·                                       |

|   | A-D Converter                                     |                                                                             |

|   |                                                   | 1 circuit (industry standard polynomial)                                    |

|   | Watchdog timer                                    | ·                                                                           |

|   | Programmable I/O                                  |                                                                             |

|   | High current and LED Drivers                      | -                                                                           |

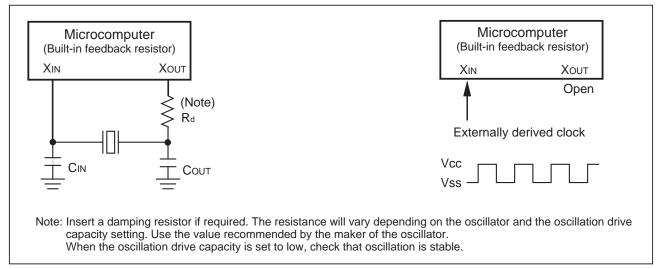

|   |                                                   | 1 built-in circuit including feedback resistor                              |

| • | Package:                                          | 80P6N (0.8 mm pitch)                                                        |

|   |                                                   |                                                                             |

# 1.2 Applications

USB peripherals, such as telephones, audio systems, scanners, and digital cameras.

Pin Configuration

# 1.3 Pin Configuration

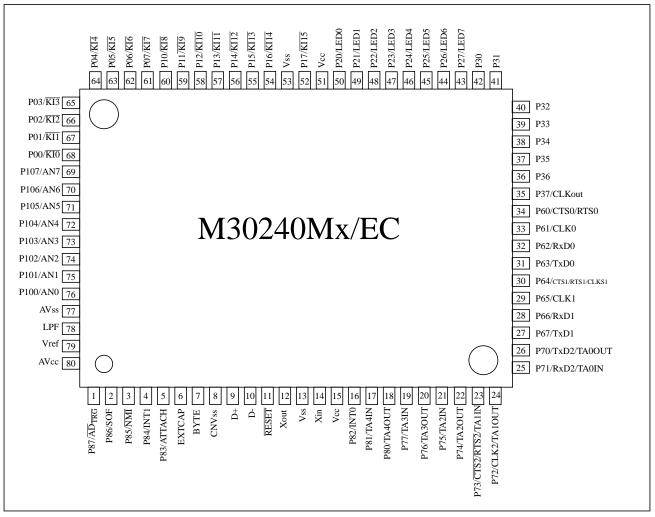

Figure 1.1 shows the pin configuration (top view).

Figure 1.1: Pin Configuration (top view)

**Block Diagram**

# 1.4 Block Diagram

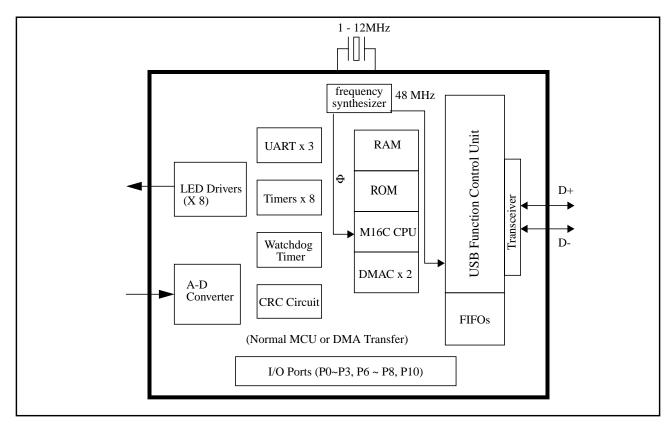

Figure 1.2 is a block diagram of the M30240 group.

Figure 1.2: Block diagram of M30240 group

Performance outline

# 1.5 Performance outline

Table 1.1 is a performance outline of the M30240 group.

#### **Table 1.1:** Performance outline of M30240 group

| Item                         |                                       | Performance                                                                                                                                                                                                                                                                                                    |  |

|------------------------------|---------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Number of basic instructions |                                       | 91 instructions                                                                                                                                                                                                                                                                                                |  |

| Shortest instruction execu   | ution time                            | 83ns (f(XIN) =12MHz)                                                                                                                                                                                                                                                                                           |  |

| Manager                      | ROM                                   | (0. 5) 0. 5014 (1. 5.11)                                                                                                                                                                                                                                                                                       |  |

| Memory capacity              | RAM                                   | (See Figure 3: ROM capacity field)                                                                                                                                                                                                                                                                             |  |

| I/O port                     | P0 to P3, P6,P7, P8 (except P85), P10 | 8 bits x 7, 7 bits x 1                                                                                                                                                                                                                                                                                         |  |

| Input port                   | P85                                   | 1 bit x 1                                                                                                                                                                                                                                                                                                      |  |

| Multifunction Timer          | TA0, TA1, TA2, TA3, TA4               | 16 bits x 5                                                                                                                                                                                                                                                                                                    |  |

| General purpose Timer        | TB0, TB1, TB2                         | 16 bits x 3                                                                                                                                                                                                                                                                                                    |  |

| Serial I/O                   | UART0, UART1, UART2                   | (UART or clock synchronous) x 3                                                                                                                                                                                                                                                                                |  |

| A-D converter                |                                       | 10 bits x 8 channels                                                                                                                                                                                                                                                                                           |  |

| DMAC                         |                                       | 2 channels (trigger:18 sources)                                                                                                                                                                                                                                                                                |  |

| CRC calculation circuit      |                                       | CRC-CCITT                                                                                                                                                                                                                                                                                                      |  |

| Watchdog timer               |                                       | 15 bits x 1 (with prescaler)                                                                                                                                                                                                                                                                                   |  |

| Interrupt                    |                                       | 21 internal and 4 external sources, 4 software sources, 7 levels                                                                                                                                                                                                                                               |  |

| Clock-generating circuit     |                                       | Built-in clock generation circuit (built-in feedback resistor, and external ceramic or quartz oscillator)                                                                                                                                                                                                      |  |

| Supply voltage (typical)     |                                       | 4.1 to 5.25V, (f(XIN)=12MHz, without software wait)                                                                                                                                                                                                                                                            |  |

| Power consumption (typic     | al)                                   | 250 mwatt, Vcc=5.0V, 12MHz                                                                                                                                                                                                                                                                                     |  |

|                              | I/O withstand voltage                 | 5V                                                                                                                                                                                                                                                                                                             |  |

| I/O characteristics          | Average output current                | 5 mA available on ports P0, P1, P3,P6, P7 <sub>1</sub> , P7 <sub>3</sub> , P7 <sub>5</sub> , P7 <sub>7</sub> , P8 <sub>1</sub> ~P8 <sub>4</sub> , P8 <sub>6</sub> , P8 <sub>7</sub> , P10 10 mA available on ports P2, P7 <sub>0</sub> , P7 <sub>2</sub> , P7 <sub>4</sub> , P7 <sub>6</sub> , P8 <sub>0</sub> |  |

| Operating temperature        |                                       | 0 to 70°C                                                                                                                                                                                                                                                                                                      |  |

| Device configuration         |                                       | CMOS high performance silicon gate                                                                                                                                                                                                                                                                             |  |

| Package                      |                                       | 80-pin plastic molded QFP                                                                                                                                                                                                                                                                                      |  |

Performance outline

Mitsubishi plans to release the following products in the M30240 group:

- (1) Support for mask ROM version and one-time PROM version

- (2) ROM capacity

- (3) Package

- 80P6N: Plastic molded QFP (mask ROM version and one-time PROM version)

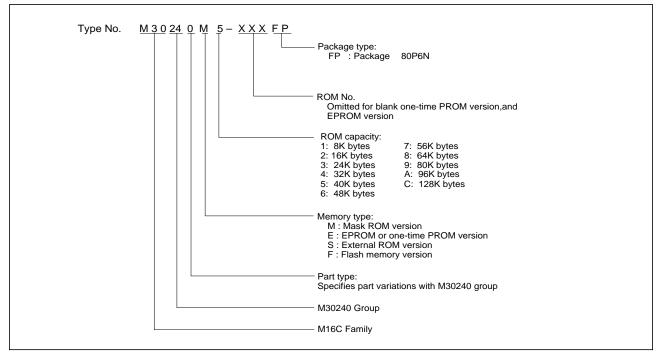

Figure 1.3 shows the type number, memory size and package for the M30240 group.

Figure 1.3: Type number, memory size, and package

Table 1.2 shows the Package Number, type, ROM and RAM Capacity for M30240 Group.

**Table 1.2:** M30240 Group

| Туре       | ROM Capacity | RAM Capacity | Package Type | Remarks               |

|------------|--------------|--------------|--------------|-----------------------|

| M30240M5   | 40K bytes    | 3K bytes     | 80P6N        | Mask ROM Version      |

| M30240M6   | 48K bytes    | 3K bytes     | 80P6N        | Mask ROM Version      |

| M30240ECFP | 128K bytes   | 5K bytes     | 80P6N        | One-time PROM version |

Pin Description

# 1.6 Pin Description

#### **Table 1.3: Figure Pin Description**

| Pin#  | Name                                             | I/O | Description                                                                                                                                                                                                                                                                                                                                    |

|-------|--------------------------------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | P8 <sub>7</sub>                                  | I/O | CMOS I/O port. This pin also functions as an external trigger for A-D conversion.                                                                                                                                                                                                                                                              |

| 2     | P8 <sub>6</sub>                                  | I/O | CMOS I/O port. This pin also functions as the start of frame (SOF) pulse for the USB module.                                                                                                                                                                                                                                                   |

| 3     | P8 <sub>5</sub> /(NMI)                           | I   | CMOS input port. This pin also functions as a non-maskable external interrupt.                                                                                                                                                                                                                                                                 |

| 4,5   | P8 <sub>4</sub> ~ P8 <sub>3</sub>                | I/O | CMOS I/O port. These pins also functions as external interrupt 1 and are used to enable the stealth detach function for the USB transceiver.                                                                                                                                                                                                   |

| 6     | EXTCAP                                           | _   | An external capacitor (Ext. Cap) pin. When the USB transceiver voltage converter is used, a 2.2 $\mu$ F and a 0.1 $\mu$ F capacitor should connect between this pin and V <sub>ss</sub> to ensure proper operation of the USB line driver. This option is enabled by setting bit 4 of the USB control register (000C <sub>16</sub> ) to a "1". |

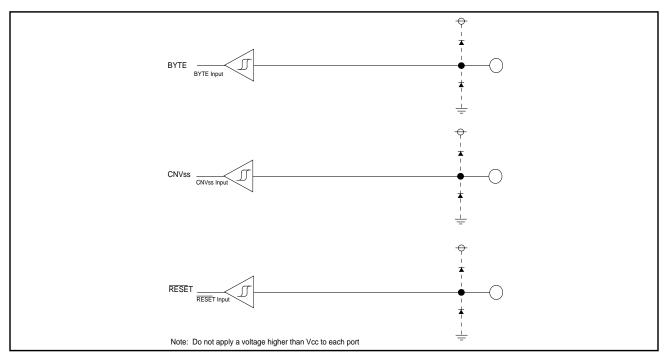

| 7     | BYTE                                             | I   | Connect this pin to Vss                                                                                                                                                                                                                                                                                                                        |

| 8     | CNV <sub>ss</sub>                                | I   | Connect this pin to Vss                                                                                                                                                                                                                                                                                                                        |

| 9     | USB D+                                           | I/O | USB D+ voltage line interface, a series resistor of 33 $\Omega$ is connected to this pin.                                                                                                                                                                                                                                                      |

| 10    | USB D-                                           | I/O | USB D- voltage line interface, a series resistor of 33 $\Omega$ is connected to this pin.                                                                                                                                                                                                                                                      |

| 11    | RESET                                            | ı   | A "L" on this input resets the microcomputer.                                                                                                                                                                                                                                                                                                  |

| 12    | Xout                                             | 0   | See Xin                                                                                                                                                                                                                                                                                                                                        |

| 13    | V <sub>ss</sub>                                  | ı   | Ground: V <sub>ss</sub> = 0V                                                                                                                                                                                                                                                                                                                   |

| 14    | Xin                                              | I   | Input and output signals to and from the internal clock generation circuit.  Connect a ceramic resonator or quartz crystal between Xin and Xout pins to set the oscillation frequency. If an external clock is used, connect the clock source to the Xin pin and leave the Xout pin open.                                                      |

| 15    | V <sub>cc</sub>                                  | ı   | Power: V <sub>cc</sub> = 4.1~ 5.25V                                                                                                                                                                                                                                                                                                            |

| 16    | P8 <sub>2</sub>                                  | I/O | CMOS I/O port. This pin also functions as external interrupt 0.                                                                                                                                                                                                                                                                                |

| 17-18 | P8 <sub>1</sub> ~ P8 <sub>0</sub>                | I/O | CMOS I/O port. Pins in this port also function as TimerA4 input and output as selected by software.                                                                                                                                                                                                                                            |

| 19-22 | P7 <sub>7</sub> ~ P7 <sub>4</sub>                | I/O | CMOS I/O port. Pins in this port also function as timer pins. P7 <sub>7</sub> and P7 <sub>6</sub> can function as TimerA3 input and output as selected by software. P7 <sub>5</sub> and P7 <sub>4</sub> can function as TimerA2 input and output as selected by software.                                                                      |

| 23-26 | P7 <sub>3</sub> ~ P7 <sub>0</sub>                | I/O | CMOS I/O port. Pins in this port also function as UART2 CTS, RTS, CLK, RXD, and TXD as selected by software. P7 <sub>3</sub> and P7 <sub>2</sub> can function as TimerA1 input and output as selected by software. P7 <sub>1</sub> and P7 <sub>0</sub> can function as TimerA0 input and output as selected by software.                       |

| 27-30 | P6 <sub>7</sub> ~ P6 <sub>4</sub>                | I/O | CMOS I/O port. Pins in this port also function as UART1 CTS, RTS, CLK, Serial Clock, RXD, and TXD as selected by software. TXD(OE~) and RTS(SUSPEND) in addition to D+ and D- can be used to run the device in USB bypass mode.                                                                                                                |

| 31-34 | P6 <sub>3</sub> ~ P6 <sub>0</sub>                | I/O | CMOS I/O port. Pins in this port also function as UART0 CTS, RTS, CLK, RXD, and TXD as selected by software.                                                                                                                                                                                                                                   |

| 35-42 | P3 <sub>7</sub> ~ P3 <sub>0</sub>                | I/O | CMOS I/O port.                                                                                                                                                                                                                                                                                                                                 |

| 43-50 | P2 <sub>7</sub> /LED7<br>~ P2 <sub>0</sub> /LED0 | I/O | CMOS I/O port. These pins are capable of driving up to 20mA (peak) for LEDs.                                                                                                                                                                                                                                                                   |

Pin Description

#### **Figure Pin Description Table 1.3:**

| Pin#  | Name                                                                                             | I/O | Description                                                                                                                        |

|-------|--------------------------------------------------------------------------------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------|

| 51    | V <sub>cc</sub>                                                                                  | I   | Power: V <sub>cc</sub> = 4.1~ 5.25V                                                                                                |

| 52    | P1 <sub>7</sub> /KI <sub>15</sub>                                                                | I/O | CMOS I/O port. This port can also function as the key-on wakeup interrupt KI15.                                                    |

| 53    | V <sub>ss</sub>                                                                                  | I   | Ground: V <sub>ss</sub> = 0V                                                                                                       |

| 54-60 | P1 <sub>6</sub> /KI <sub>14</sub><br>~ P1 <sub>0</sub> /KI <sub>8</sub>                          | I/O | CMOS I/O port. This port can also function as the key-on wakeup interrupts ( $\overline{\text{KI8}}$ ~ $\overline{\text{KI14}}$ ). |

| 61-68 | P0 <sub>7</sub> / <del>K</del> I <sub>7</sub><br>~ P0 <sub>0</sub> / <del>K</del> I <sub>0</sub> | I/O | CMOS I/O port. This port can also function as the key-on wakeup interrupts ( $\overline{\text{KI0}}$ ~ $\overline{\text{KI7}}$ ).  |

| 69-76 | P10 <sub>7</sub> ~ P10 <sub>0</sub>                                                              | I/O | CMOS I/O port. These pins also function as Analog inputs 7-0 for A-D conversion                                                    |

| 77    | AV <sub>ss</sub>                                                                                 | I   | This pin is a power supply input for the AD converter. (Connect to Vss)                                                            |

| 78    | LPF                                                                                              | 0   | Loop filter for the frequency synthesizer.                                                                                         |

| 79    | V <sub>REF</sub>                                                                                 | I   | This pin is the reference voltage input for the A-D converter.                                                                     |

| 80    | AV <sub>cc</sub>                                                                                 | I   | This pin is a power supply input for the AD converter. (Connect to Vcc)                                                            |

Overview

#### 1.7 Overview

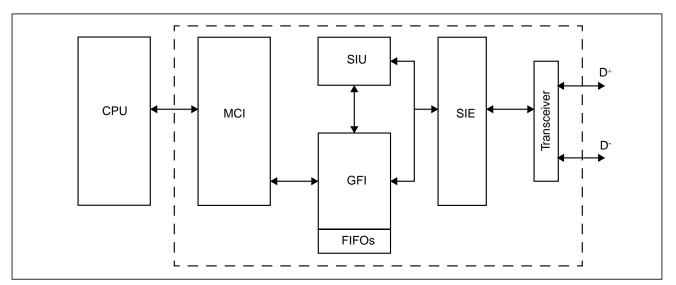

The M30240 group is a single chip PC peripheral microcontroller based on the Universal Serial Bus (USB) Version 1.1 specification. This device provides interface between a USB-equipped host computer and PC peripherals such as telephones, audio systems, and digital cameras. The M30240 block diagram is shown in Figure 1.4.

The USB function control unit of the M30240 group can support all four data transfer types listed in the USB specification: Isochronous, Interrupt, Bulk, and Control. Each transfer type is used for controlling a different set of PC peripherals. <u>Isochronous transfers</u> provide guaranteed bus access, a constant data rate, and error tolerance for devices such as computer-telephone integration (CTI) and audio systems. <u>Interrupt transfers</u> are designed to support human input devices (HID) that communicate small amounts of data infrequently. <u>Bulk transfers</u> are necessary for devices such as digital cameras and scanners that communicate large amounts of data to the PC as bus bandwidth becomes free. Finally, <u>control transfers</u> are supported and are useful for bursty, host-initiated type communication where bus management is the primary concern.

Figure 1.4: M30240 block diagram

Central Processing Unit (CPU)

# 2.0 Operation of Functional Blocks

The M30240 group accommodates certain units in a single chip. These units include ROM and RAM to store instructions and data, and the central processing unit (CPU) to execute arithmetic/logic operations. Also included are peripheral units such as USB, timers, serial I/O, DMAC, CRC calculation circuit, A-D converter, and I/O ports.

The following explains each unit.

# 2.1 Central Processing Unit (CPU)

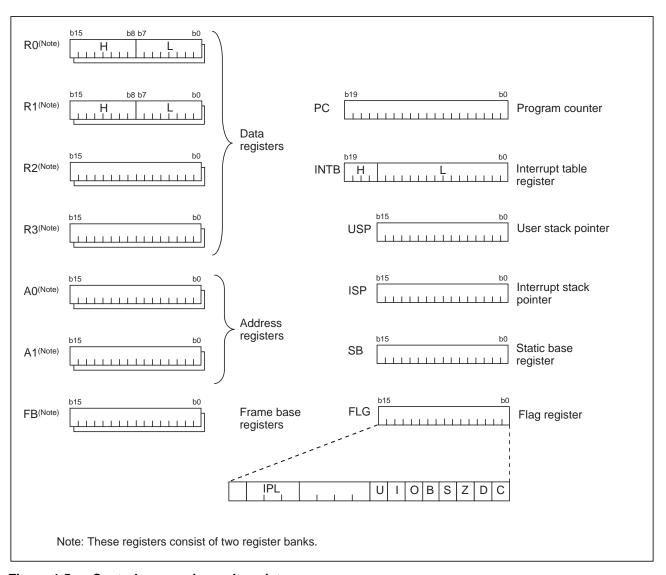

The CPU has a total of 13 registers shown in Figure 1.5. Seven of these registers (R0, R1, R2, R3, A0, A1, and FB) come in two sets; therefore, these have two register banks.

Figure 1.5: Central processing unit register

# 2.1.1 Data registers (R0, R0H, R0L, R1, R1H, R1L, R2, and R3)

Data registers (R0, R1, R2, and R3) are configured with 16 bits, and are used primarily for transfer and arithmetic/logic operations.

Central Processing Unit (CPU)

Registers R0 and R1 each can be used as separate 8-bit data registers, high-order bits as (R0H/R1H), and low-order bits as (R0L/R1L). In some instructions, registers R2 and R0, as well as R3 and R1, can be used as 32-bit data registers (R2R0/R3R1).

#### 2.1.2 Address registers (A0 and A1)

Address registers (A0 and A1) are configured with 16 bits, and have functions equivalent to those of data registers. These registers can also be used for address register indirect addressing and address register relative addressing.

In some instructions, registers A1 and A0 can be combined for use as a 32-bit address register (A1A0).

#### 2.1.3 Frame base register (FB)

Frame base register (FB) is configured with 16 bits, and is used for FB relative addressing.

#### 2.1.4 Program counter (PC)

Program counter (PC) is configured with 20 bits, indicating the address of an instruction to be executed.

#### 2.1.5 Interrupt table register (INTB)

Interrupt table register (INTB) is configured with 20 bits, indicating the start address of an interrupt vector table. INTB can be used as separate registers of four high-order bits and 16 low-order bits.

#### 2.1.6 Stack pointer (USP/ISP)

Stack pointer comes in two types: user stack pointer (USP) and interrupt stack pointer (ISP), each configured with 16 bits.

Your desired type of stack pointer (USP or ISP) can be selected by a stack pointer select flag (U flag). This flag is located at the position of bit 7 in the flag register (FLG).

#### 2.1.7 Static base register (SB)

Static base register (SB) is configured with 16 bits, and is used for SB relative addressing.

#### 2.1.8 Flag register (FLG)

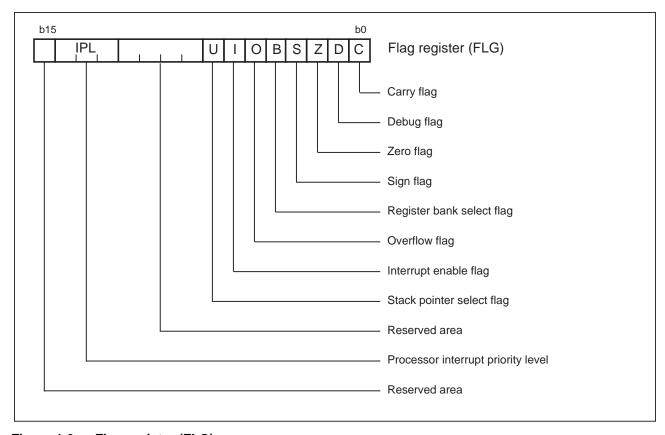

Flag register (FLG) is configured with 11 bits, each bit is used as a flag. Figure 1.6 shows the flag register (FLG). The following explains the function of each flag:

#### 2.1.8.1 Bit 0: Carry flag (C flag)

This flag retains a carry, borrow, or shift-out bit that has occurred in the arithmetic/logic unit.

#### 2.1.8.2 Bit 1: Debug flag (D flag)

This flag enables a single-step interrupt.

When this flag is "1", a single-step interrupt is generated after instruction execution. This flag is cleared to "0" when the interrupt is acknowledged.

#### 2.1.8.3 Bit 2: Zero flag (Z flag)

This flag is set to "1" when an arithmetic operation resulted in 0; otherwise, cleared to "0".

### 2.1.8.4 Bit 3: Sign flag (S flag)

This flag is set to "1" when an arithmetic operation resulted in a negative value; otherwise, cleared to "0".

#### 2.1.8.5 Bit 4: Register bank select flag (B flag)

This flag chooses a register bank. Register bank 0 is selected when this flag is "0"; register bank 1 is selected when this flag is "1".

#### 2.1.8.6 Bit 5: Overflow flag (O flag)

This flag is set to "1" when an arithmetic operation resulted in overflow; otherwise, cleared to "0".

Central Processing Unit (CPU)

#### 2.1.8.7 Bit 6: Interrupt enable flag (I flag)

This flag enables a maskable interrupt.

An interrupt is disabled when this flag is "0", and is enabled when this flag is "1". This flag is cleared to "0" when the interrupt is acknowledged.

# 2.1.8.8 Bit 7: Stack pointer select flag (U flag)

Interrupt stack pointer (ISP) is selected when this flag is "0"; user stack pointer (USP) is selected when this flag is "1".

This flag is cleared to "0" when a hardware interrupt is acknowledged or an INT instruction of software interrupts 0 to 31 is executed.

#### 2.1.8.9 Bits 8 to 11: Reserved area

#### 2.1.8.10 Bits 12 to 14: Processor interrupt priority level (IPL)

Processor interrupt priority level (IPL) is configured with three bits, for specification of up to eight processor interrupt priority levels from level 0 to level 7.

If a requested interrupt has priority greater than the processor interrupt priority level (IPL), the interrupt is enabled.

#### 2.1.8.11 Bit 15: Reserved area

The C, Z, S, and O flags are changed when instructions are executed. See the M16C software manual for details.

Figure 1.6: Flag register (FLG)

**Processor Mode**

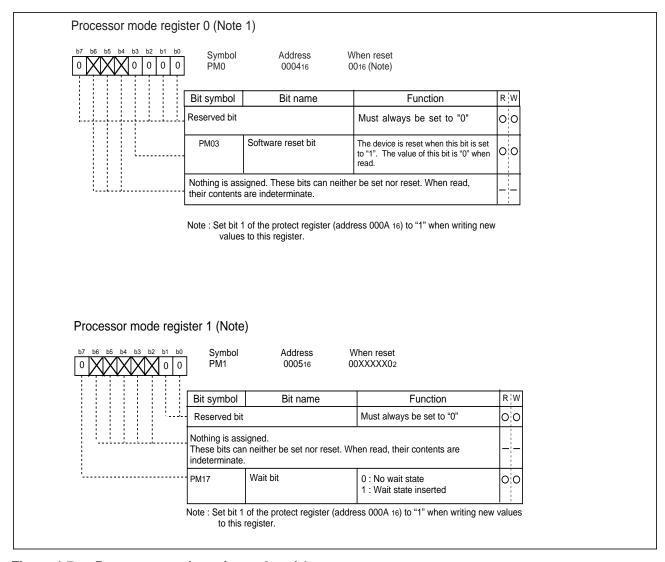

#### 2.2 Processor Mode

Figure 1.7 shows the processor mode registers 0 and 1.

Figure 1.7: Processor mode registers 0 and 1

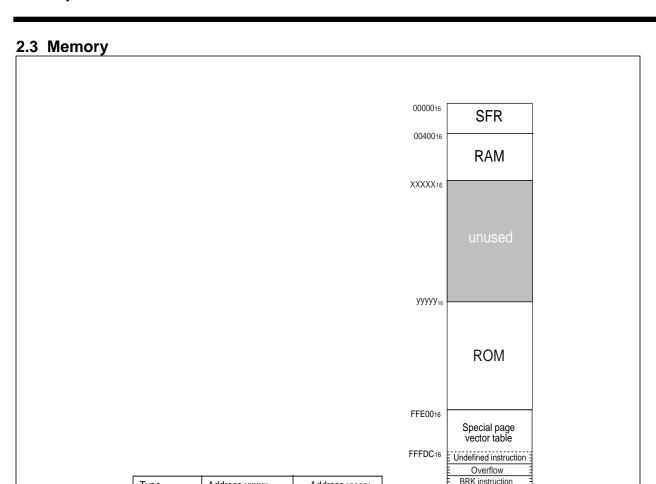

Memory

Figure 1.8: Memory Map

Type

M30240M5

M30240M6

M30240ECFP

Address xxxxx 16

0100016

0100016

018001

Figure 1.8 is a memory map of the M30240 group. The address space extends the 1M bytes from address  $00000_{16}$  to FFFFF<sub>16</sub>. Addresses above  $yyyyy_{16}$  are ROM. For example, in the M30240ECFP, there is 128K bytes of internal ROM from  $E0000_{16}$  to FFFFF<sub>16</sub>. The special page vector table is mapped from FFE00<sub>16</sub> to FFFDB<sub>16</sub>. If the starting addresses of subroutines or the destination addresses of jumps are stored here, subroutine call instructions and jump instructions can be used as two-byte instructions, reducing the number of program steps.

Address yyyyy 16

F6000<sub>16</sub>

F4000<sub>16</sub>

E0000<sub>1</sub>

Address match

Single step

Watchdog timer DBC

NMI

Reset

FFFFF16

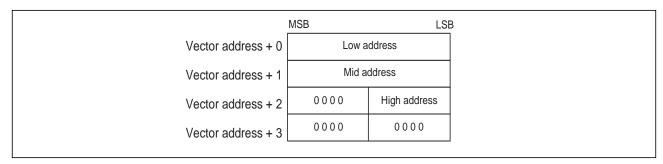

The vector table for fixed interrupts such as the reset and  $\overline{\text{NMI}}$  are mapped from FFFDC<sub>16</sub> to FFFFF<sub>16</sub>. The starting addresses of the interrupt routines are stored here. The address of the vector table for software interrupts can be set as desired using the internal register (INTB). See Section 2.12 on interrupts for further details.

Addresses below  $xxxxx_{16}$  are RAM. For example, in M30240ECFP, 5K bytes of internal RAM are mapped to the space from  $00400_{16}$  to  $017FF_{16}$ . In addition to storing data, the RAM also stores the stack used when calling subroutines and when interrupts are generated. The SFR area is mapped to  $00000_{16}$  to  $003FF_{16}$ . This area accommodates control registers for peripheral devices such as I/O ports, A-D converter, serial I/O, and timers. Section 2.4 describes the SFR area for peripheral unit control registers. Any part of the SFR area that is unoccupied is reserved and cannot be used for other purposes.

# 2.4 SFR MAP

The table below shows the peripheral control registers, their addresses, names, acronyms, and values after reset.

| Address                                  | Register name                           | Acronym | Value after reset                        |

|------------------------------------------|-----------------------------------------|---------|------------------------------------------|

| 0000 <sub>16</sub>                       |                                         |         |                                          |

| 0001 <sub>16</sub><br>0002 <sub>16</sub> |                                         | -       |                                          |

| 000316                                   |                                         | -       |                                          |

| 0004 <sub>16</sub>                       | Processor mode register 0               | PM0     | 0016                                     |

| 0005 <sub>16</sub>                       | Processor mode register 1               | PM1     | 0 0                                      |

| 0006 <sub>16</sub><br>0007 <sub>16</sub> | System clock control register 0         | CM0     | 48 <sub>16</sub>                         |

| 000716                                   | System clock control register 1         | CM1     | 20 <sub>16</sub>                         |

| 000916                                   | Address match interrupt enable register | AIER    | 0 0                                      |

| 000A <sub>16</sub>                       | Protect register                        | PRCR    | 0 0 0                                    |

| 000B <sub>16</sub>                       | LIOD and the land and a land            | LIODO   | 00                                       |

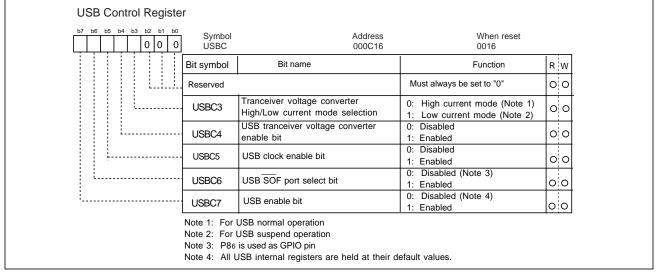

| 000C <sub>16</sub>                       | USB control register                    | USBC    | 0016                                     |

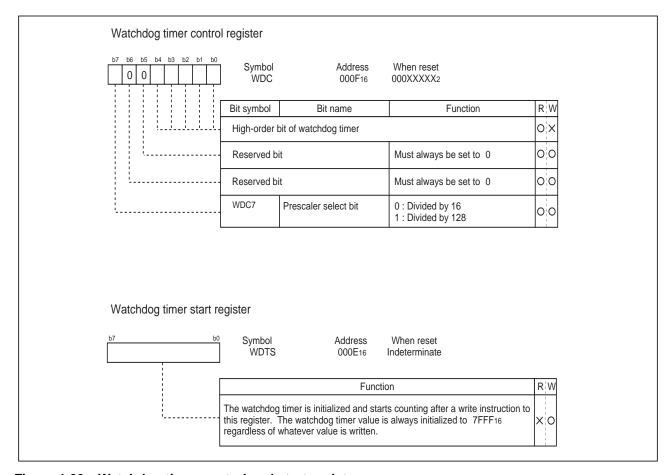

| 000E <sub>16</sub>                       | Watchdog timer start register           | WDTS    |                                          |

| 000F <sub>16</sub>                       | Watchdog timer control register         | WDC     | 0 0 0 ? ? ? ? ?                          |

| 0010 <sub>16</sub>                       |                                         | D D.    | 0016                                     |

| 0011 <sub>16</sub><br>0012 <sub>16</sub> | Address match interrupt register 0      | RMAD0   | 0016                                     |

| 001216                                   |                                         | 1       | 0101010                                  |

| 0014 <sub>16</sub>                       |                                         | 1       | 0016                                     |

| 0015 <sub>16</sub>                       | Address match interrupt register 1      | RMAD1   | 0016                                     |

| 0016 <sub>16</sub>                       |                                         | 1       | 0 0 0 0                                  |

| 0017 <sub>16</sub><br>0018 <sub>16</sub> |                                         | -       |                                          |

| 001016                                   |                                         | 1       |                                          |

| 001A <sub>16</sub>                       |                                         |         |                                          |

| 001B <sub>16</sub>                       |                                         |         |                                          |

| 001C <sub>16</sub>                       |                                         | -       |                                          |

| 001D <sub>16</sub><br>001E <sub>16</sub> | Reserved                                | -       |                                          |

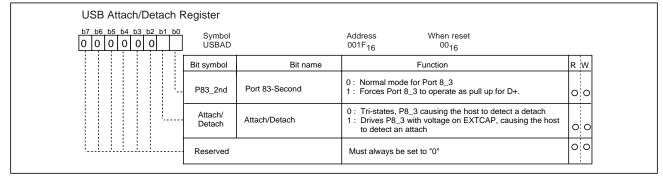

| 001F <sub>16</sub>                       | USB attach / detach register            | USBAD   | 0016                                     |

|                                          |                                         | USBAD   | 0016                                     |

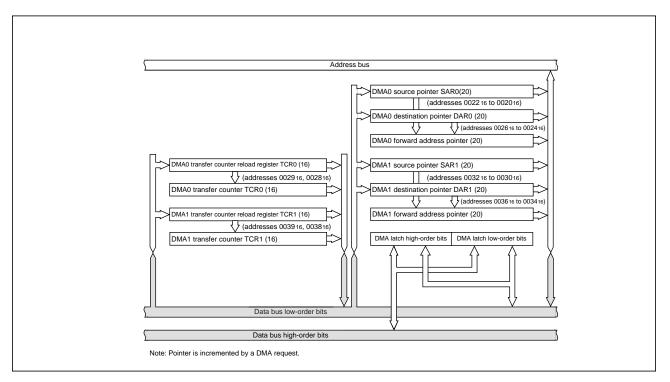

| 0020 <sub>16</sub><br>0021 <sub>16</sub> | DMA0 source pointer                     | SAR0    |                                          |

| 002216                                   | DWAO Source pointer                     | OAITO   |                                          |

| 0023 <sub>16</sub>                       |                                         |         |                                          |

| 0024 <sub>16</sub>                       |                                         |         |                                          |

| 0025 <sub>16</sub><br>0026 <sub>16</sub> | DMA0 destination pointer                | DAR0    |                                          |

| 002016                                   |                                         | 1       |                                          |

| 002816                                   | DMA0 transfer counter                   | TCR0    |                                          |

| 0029 <sub>16</sub>                       | DIMAO (Tansier Counter                  | TORU    |                                          |

| 002A <sub>16</sub><br>002B <sub>16</sub> |                                         | -       |                                          |

| 002B <sub>16</sub>                       | DMA0 control register                   | DMOCON  | 00000?00                                 |

| 002D <sub>16</sub>                       |                                         | 1       | -   -   -   -                            |

| 002E <sub>16</sub>                       |                                         |         |                                          |

| 002F <sub>16</sub>                       |                                         | 4       |                                          |

| 0030 <sub>16</sub><br>0031 <sub>16</sub> | DMA1 source pointer                     | SAR1    |                                          |

| 003116                                   | 2 Godioo pointoi                        | 3,      |                                          |

| 0033 <sub>16</sub>                       |                                         |         |                                          |

| 0034 <sub>16</sub>                       |                                         |         |                                          |

| 0035 <sub>16</sub><br>0036 <sub>16</sub> | DMA1 destination pointer                | DAR1    |                                          |

| 0036 <sub>16</sub>                       |                                         | 1       |                                          |

| 0038 <sub>16</sub>                       | DMA1 transfer counter                   | TCP4    |                                          |

| 0039 <sub>16</sub>                       | DIVIA I ITALISIEI COULIEF               | TCR1    |                                          |

| 003A <sub>16</sub>                       |                                         | 1       |                                          |

| 003B <sub>16</sub><br>003C <sub>16</sub> | DMA1 control register                   | DM1CON  | 00000?00                                 |

| 003D <sub>16</sub>                       | 2 Control register                      |         | -1-1-1-1-1-1-1-1-1-1-1-1-1-1-1-1-1-1-1-1 |

| 003E <sub>16</sub>                       |                                         |         |                                          |

| 003F <sub>16</sub>                       |                                         |         |                                          |

|                                          |                                         |         |                                          |

| Address                                  | Register name                                                                      | Acronym         | Value after reset |          |

|------------------------------------------|------------------------------------------------------------------------------------|-----------------|-------------------|----------|

| 0040 <sub>16</sub>                       |                                                                                    |                 |                   | П        |

| 0041 <sub>16</sub>                       |                                                                                    |                 |                   |          |

| 0042 <sub>16</sub>                       |                                                                                    | _               |                   |          |

| 0043 <sub>16</sub>                       |                                                                                    |                 |                   | _        |

| 0044 <sub>16</sub><br>0045 <sub>16</sub> | Suspend interrupt control register                                                 | SUSPIC          | ? 0 0 0           | $\dashv$ |

| 001516                                   | Resume interrupt control register                                                  | RSMIC           | ? 0 0 0           | $\dashv$ |

| 0047 <sub>16</sub>                       | USB SOF interrupt control register                                                 | SOFIC           | 007000            | 7        |

| 004816                                   |                                                                                    |                 |                   | $\neg$   |

| 004916                                   |                                                                                    |                 |                   |          |

| $004A_{16}$                              | Bus collision detection interrupt control register                                 | BCNIC           | ? 0 0 0           |          |

| $004B_{16}$                              | DMA0 interrupt control register                                                    | DM0IC           | ? 0 0 0           |          |

| 004C <sub>16</sub>                       |                                                                                    | DM1IC           | ? 0 0 0           |          |

| 004D <sub>16</sub>                       | Key input interrupt control register                                               | KUPIC           | ? 0 0 0           | 4        |

| 004E <sub>16</sub>                       | A-D conversion interrupt control register                                          | ADIC<br>S2TIC   | ? 0 0 0           | -        |

| 004F <sub>16</sub><br>0050 <sub>16</sub> | UART2 transmit interrupt control register UART2 receive interrupt control register | S2RIC           | ? 0 0 0           | $\dashv$ |

| 005116                                   | UART0 transmit interrupt control register                                          | SOTIC           | 7 0 0 0           | -        |

| 005216                                   |                                                                                    | SORIC           | ? 0 0 0           | _        |

| 005316                                   |                                                                                    | S1TIC           | ? 0 0 0           |          |

| 0054 <sub>16</sub>                       | UART1 receive interrupt control register                                           | S1RIC           | ? 0 0 0           |          |

| 0055 <sub>16</sub>                       | TIMER A0 interrupt control register                                                | TA0IC           | ? 0 0 0           |          |

| 0056 <sub>16</sub>                       | TIMER A1 interrupt control register                                                | TA1IC           | ? 0 0 0           |          |

| 0057 <sub>16</sub>                       | TIMER A2 interrupt control register                                                | TA2IC           | ? 0 0 0           | 4        |

| 0058 <sub>16</sub>                       | TIMER A3 interrupt control register                                                | TA3IC<br>TA4IC  | ? 0 0 0           | $\dashv$ |

| 0059 <sub>16</sub><br>005A <sub>16</sub> | TIMER A4 interrupt control register TIMER B0 interrupt control register            | TB0IC           | ? 0 0 0           | $\dashv$ |

| 005H <sub>16</sub>                       | TIMER B1 interrupt control register                                                | TB1IC           | ? 0 0 0           | -        |

|                                          | Reset interrupt control register                                                   | RSTIC           | ? 0 0 0           | $\dashv$ |

|                                          | INT0 interrupt control register                                                    | INTOIC          | 0 0 ? 0 0 0       | $\neg$   |

| 005E <sub>16</sub>                       | INT1 interrupt control register                                                    | INT1IC          | 0 0 ? 0 0 0       | П        |

| 005F <sub>16</sub>                       | USB function interrupt control register                                            | USBFIC          | ? 0 0 0           |          |

|                                          | LIOD address as sisten                                                             | 1               |                   | _        |

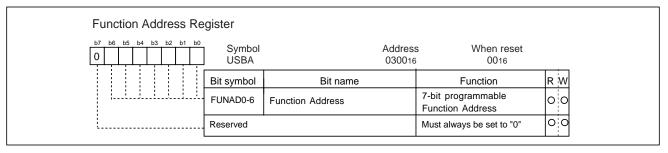

| 0300 <sub>16</sub>                       | USB address register                                                               | USBA            | 0016              | $\dashv$ |

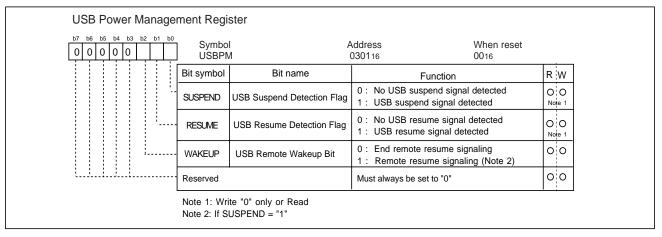

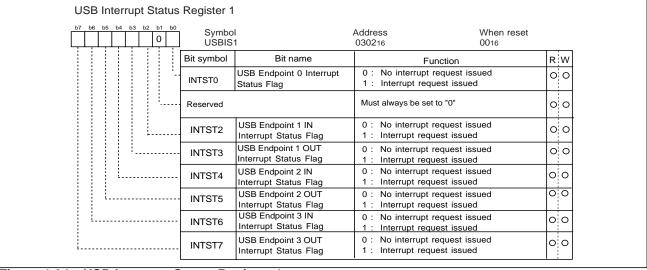

| 030116                                   | USB power management register USB interrupt status register 1                      | USBPM<br>USBIS1 | 00 <sub>16</sub>  | -        |

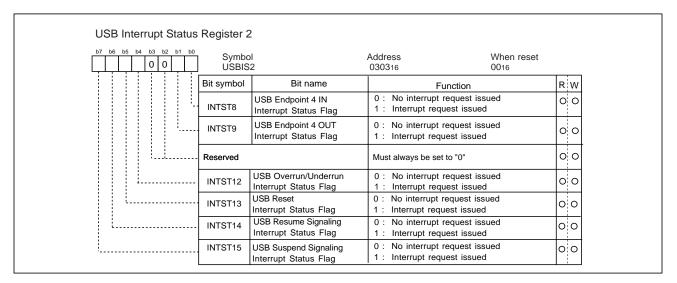

| 030216                                   | USB interrupt status register 2                                                    | USBIS2          | 0016              | -        |

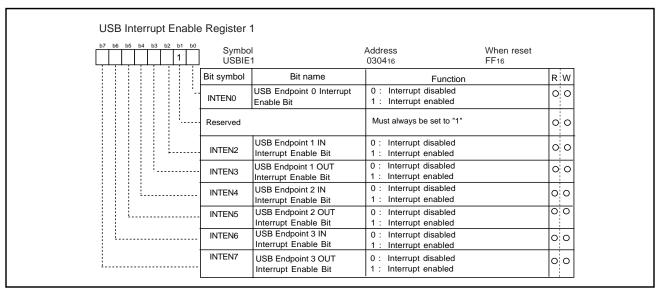

| 0304 <sub>16</sub>                       | USB interrupt enable register 1                                                    | USBIE1          | FF <sub>16</sub>  | $\dashv$ |

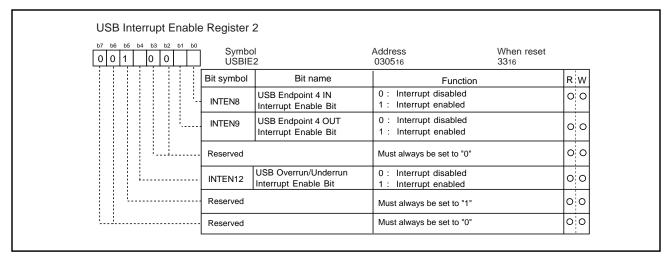

| 0305 <sub>16</sub>                       | USB interrupt enable register 2                                                    | USBIE2          | 33 <sub>16</sub>  | -        |

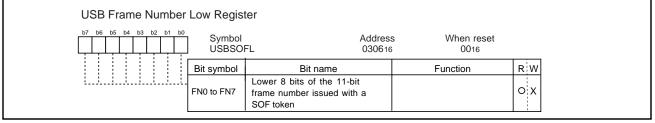

| 030616                                   | USB frame number register low                                                      | USBSOFL         | 0016              | П        |

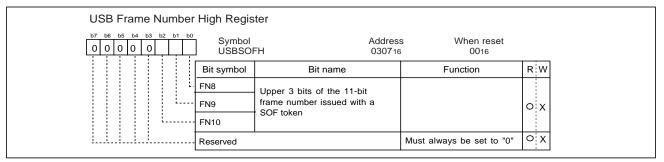

| 0307 <sub>16</sub>                       | USB frame number register high                                                     | USBSOFH         | 0016              | $\neg$   |

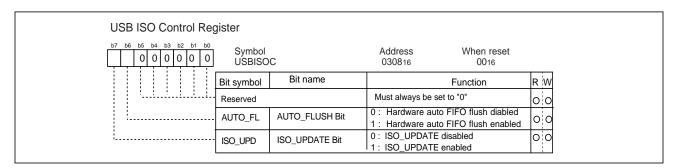

| 0308 <sub>16</sub>                       | USB ISO control register                                                           | USBISOC         | 0016              | П        |

| 0309 <sub>16</sub>                       | USB DMA0 source register                                                           | USBSAR0         | 0016              |          |

| 030A <sub>16</sub>                       | USB DMA1 source register                                                           | USBSAR1         | 0016              |          |

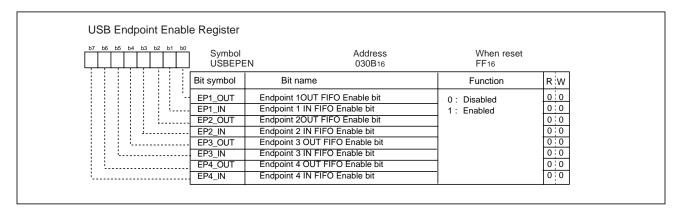

| 030B <sub>16</sub>                       | USB endpoint enable                                                                | USBEPEN         | FF <sub>16</sub>  | _        |

| 030C <sub>16</sub><br>030D <sub>16</sub> |                                                                                    | 4               |                   |          |

| 030D <sub>16</sub><br>030E <sub>16</sub> |                                                                                    | 1               |                   |          |

| 030E <sub>16</sub>                       |                                                                                    | †               |                   |          |

|                                          | USB reserved                                                                       |                 |                   |          |

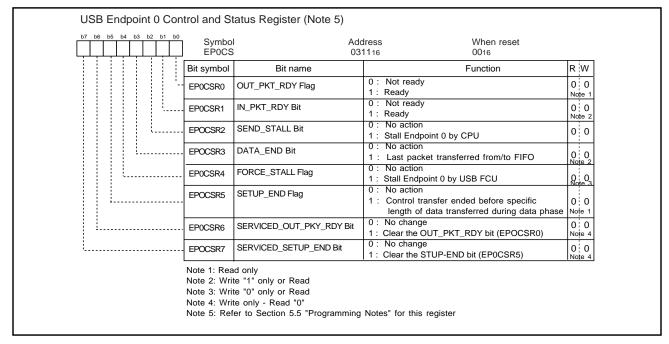

|                                          | USB EP 0 control/status register                                                   | EP0CS           | 0016              | $\neg$   |

| 0312 <sub>16</sub>                       | USB reserved                                                                       |                 |                   |          |

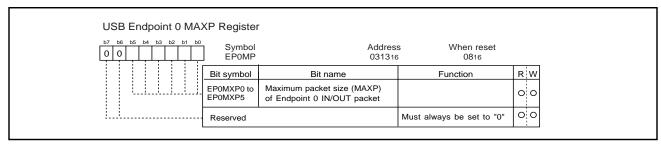

|                                          | USB EP 0 max packet size register                                                  | EP0MP           | 08 <sub>16</sub>  |          |

|                                          | USB reserved                                                                       |                 |                   | 4        |

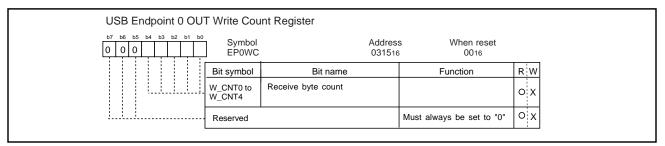

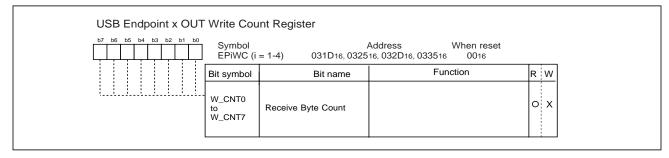

|                                          | USB EP 0 OUT write count                                                           | EP0WC           | 0016              | -        |

| 0316 <sub>16</sub>                       | USB reserved USB reserved                                                          | 1               |                   |          |

|                                          | USB reserved                                                                       | -               |                   |          |

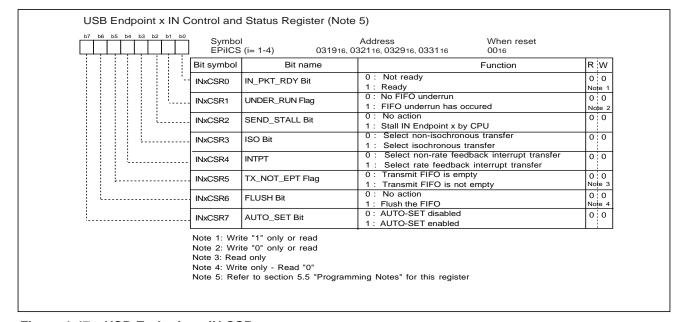

|                                          | USB EP 1 IN control/status register                                                | EP1ICS          | 0016              | -        |

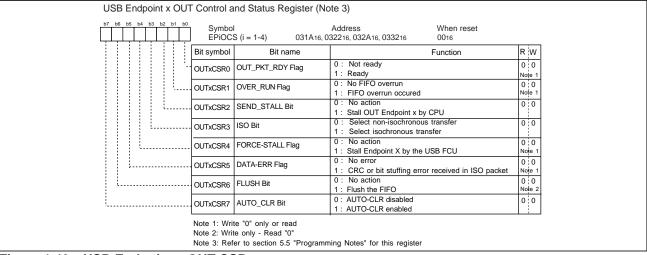

|                                          | USB EP 1 OUT control/status register                                               | EP10CS          | 0016              | $\dashv$ |

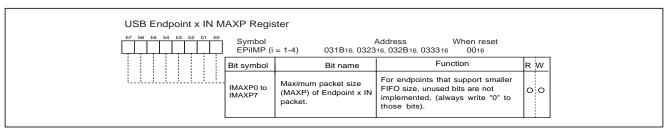

|                                          | USB EP 1 IN max packet size register                                               | EP1IMP          | 0016              | $\dashv$ |

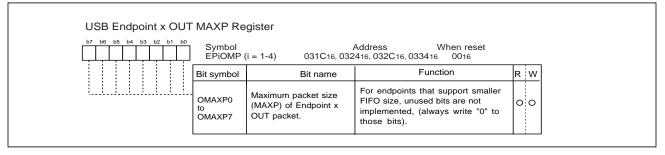

|                                          | USB EP 1 OUT max packet size register                                              | EP10MP          | 0016              | T        |

|                                          | USB EP 1 OUT write count                                                           | EP1WC           | 0016              | T        |

|                                          | USB reserved                                                                       |                 |                   |          |

| 031F <sub>16</sub>                       | USB reserved                                                                       |                 |                   | $\Box$   |

|                                          |                                                                                    |                 |                   |          |

| Address                                  | Register name                         | Acronym    | Value after reset |  |

|------------------------------------------|---------------------------------------|------------|-------------------|--|

|                                          | USB reserved                          | ]          | Value alter recet |  |

| 032116                                   | USB EP 2 IN control/status register   | EP2ICS     | 0016              |  |

| 032216                                   | USB EP 2 OUT control/status register  | EP2OCS     | 0016              |  |

| 032316                                   | USB EP 2 IN max packet size register  | EP2IMP     | 0016              |  |

| 0324 <sub>16</sub>                       | USB EP 2 OUT max packet size register | EP2OMP     | 0016              |  |

| 0325 <sub>16</sub>                       | USB EP 2 OUT write count              | EP2WC      | 0016              |  |

| 0326 <sub>16</sub>                       | USB reserved                          |            |                   |  |

| 0327 <sub>16</sub>                       | USB reserved                          |            |                   |  |

| 0328 <sub>16</sub>                       | USB reserved                          |            |                   |  |

| 0329 <sub>16</sub>                       | USB EP 3 IN control/status register   | EP3ICS     | 0016              |  |

| 032A <sub>16</sub>                       | USB EP 3 OUT control/status register  | EP3OCS     | 0016              |  |

| 032B <sub>16</sub>                       |                                       | EP3IMP     | 00 <sub>16</sub>  |  |

| 032C <sub>16</sub>                       | USB EP 3 OUT max packet size register | EP3OMP     | 0016              |  |

| 032D <sub>16</sub>                       |                                       | EP3WC      | 0016              |  |

| 032E <sub>16</sub>                       |                                       | _          | 0016              |  |

| 032F <sub>16</sub>                       |                                       |            |                   |  |

| 0330 <sub>16</sub>                       |                                       |            |                   |  |

| 0331 <sub>16</sub>                       | USB EP 4 IN control/status register   | EP4ICS     | 0016              |  |

| 0332 <sub>16</sub>                       | -                                     | EP4OCS     | 0016              |  |

| 0333 <sub>16</sub>                       | <u> </u>                              | EP4IMP     | 0016              |  |

| 0334 <sub>16</sub>                       |                                       | EP40MP     | 0016              |  |

| 0335 <sub>16</sub>                       |                                       | EP4WC      | 0016              |  |

| 0336 <sub>16</sub>                       |                                       | _          |                   |  |

| 0337 <sub>16</sub>                       | USB reserved                          |            |                   |  |

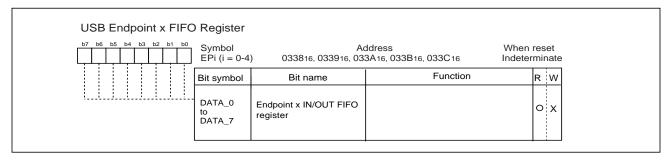

| 0338 <sub>16</sub>                       | USB EP 0 FIFO                         | EP0        |                   |  |

| 0339 <sub>16</sub>                       |                                       | EP1<br>EP2 |                   |  |

| 033A <sub>16</sub><br>033B <sub>16</sub> |                                       | EP3        |                   |  |

| 033B <sub>16</sub>                       |                                       | EP4        |                   |  |

| 033C <sub>16</sub>                       |                                       |            |                   |  |

| 033E <sub>16</sub>                       |                                       | 1          |                   |  |

| 033E <sub>16</sub>                       | reserved                              | 1          |                   |  |

| 0340 <sub>16</sub>                       | 10001700                              | 1          |                   |  |

| 0341 <sub>16</sub>                       |                                       | 1          |                   |  |

| 034216                                   |                                       | -          |                   |  |

| 034316                                   |                                       |            |                   |  |

| 034416                                   |                                       |            |                   |  |

| 0345 <sub>16</sub>                       |                                       |            |                   |  |

| 0346 <sub>16</sub>                       |                                       |            |                   |  |

| 0347 <sub>16</sub>                       |                                       |            |                   |  |

| 0348 <sub>16</sub>                       |                                       |            |                   |  |

| 0349 <sub>16</sub>                       |                                       |            |                   |  |

| 034A <sub>16</sub>                       |                                       |            |                   |  |

| 034B <sub>16</sub>                       |                                       |            |                   |  |

| 034C <sub>16</sub>                       |                                       | 4          |                   |  |

| 034D <sub>16</sub>                       |                                       | 1          |                   |  |

| 034E <sub>16</sub>                       |                                       | 4          |                   |  |

| 034F <sub>16</sub>                       |                                       | _          |                   |  |

| 0350 <sub>16</sub>                       |                                       | 1          |                   |  |

| 0351 <sub>16</sub>                       |                                       | 4          |                   |  |

| 0352 <sub>16</sub><br>0353 <sub>16</sub> |                                       | 4          |                   |  |

| 035316                                   |                                       | -          |                   |  |

| 035516                                   |                                       | -          |                   |  |

| 0355 <sub>16</sub>                       |                                       | †          |                   |  |

| 035716                                   |                                       | 1          |                   |  |

| 0358 <sub>16</sub>                       |                                       | 1          |                   |  |

| 0359 <sub>16</sub>                       |                                       | 1          |                   |  |

| 035A <sub>16</sub>                       |                                       | 1          |                   |  |

| 035B <sub>16</sub>                       |                                       | 1          |                   |  |

| 035C <sub>16</sub>                       |                                       | 1          |                   |  |

| 035D <sub>16</sub>                       |                                       | 1          |                   |  |

| 035E <sub>16</sub>                       |                                       |            |                   |  |

| 035F <sub>16</sub>                       |                                       |            |                   |  |

|                                          |                                       | _          |                   |  |

| Address            | Register name                               | Acronym | Value after reset |  |

|--------------------|---------------------------------------------|---------|-------------------|--|

| 0370 <sub>16</sub> |                                             | ]       |                   |  |

| 0371 <sub>16</sub> |                                             |         |                   |  |

| 0372 <sub>16</sub> |                                             |         |                   |  |

| 0373 <sub>16</sub> |                                             |         |                   |  |

| 0374 <sub>16</sub> |                                             |         |                   |  |

| 0375 <sub>16</sub> |                                             |         |                   |  |

| 0376 <sub>16</sub> |                                             |         |                   |  |

| 0377 <sub>16</sub> | Reserved                                    |         |                   |  |

| 0378 <sub>16</sub> | UART2 transmit / receive mode register      | U2MR    | 0016              |  |

| 0379 <sub>16</sub> | UART2 bit rate generator                    | U2BRG   |                   |  |

| 037A <sub>16</sub> | UART2 transmit buffer register              | U2TB    |                   |  |

| 037B <sub>16</sub> |                                             |         | 00                |  |

| 037C <sub>16</sub> | UART2 transmit /receive control register 0  | U2C0    | 08 <sub>16</sub>  |  |

| 037D <sub>16</sub> | UART2 transmit / receive control register 1 | U2C1    | 02 <sub>16</sub>  |  |

| 037E <sub>16</sub> | UART2 receive buffer register               | U2RB    |                   |  |

| 037F <sub>16</sub> | _                                           |         | 00                |  |

| 0380 <sub>16</sub> | Count start flag                            | TABSR   | 0016              |  |

| 0381 <sub>16</sub> | Reserved                                    | ONOF    |                   |  |

| 0382 <sub>16</sub> | One-shot start flag                         | ONSF    | 0 0 0 0 0 0 0     |  |

| 0383 <sub>16</sub> | Trigger select register                     | TRGSR   | 0016              |  |

| 0384 <sub>16</sub> | Up-down flag                                | UDF     | 0016              |  |

| 0385 <sub>16</sub> |                                             |         |                   |  |

| 0386 <sub>16</sub> | Timer A0                                    | TA0     |                   |  |

| 0387 <sub>16</sub> |                                             |         |                   |  |

| 0388 <sub>16</sub> | Timer A1                                    | TA1     |                   |  |

| 0389 <sub>16</sub> | -                                           |         |                   |  |

| 038A <sub>16</sub> | Timer A2                                    | TA2     |                   |  |

| 038B <sub>16</sub> | -                                           |         |                   |  |

| 038C <sub>16</sub> | Timer A3                                    | TA3     |                   |  |

| 038D <sub>16</sub> |                                             |         |                   |  |

| 038E <sub>16</sub> | Timer A4                                    | TA4     |                   |  |

| 038F <sub>16</sub> | -                                           |         |                   |  |

| 0390 <sub>16</sub> | Timer B0                                    | тво     |                   |  |

| 0391 <sub>16</sub> |                                             |         |                   |  |

| 0392 <sub>16</sub> | Timer B1                                    | TB1     |                   |  |

| 0393 <sub>16</sub> |                                             |         |                   |  |

| 0394 <sub>16</sub> | Timer B2                                    | TB2     |                   |  |

| 0395 <sub>16</sub> |                                             |         |                   |  |

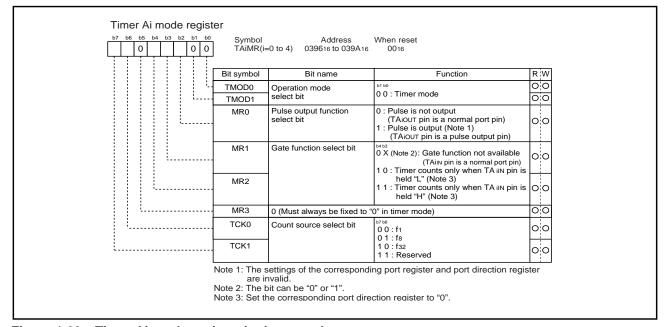

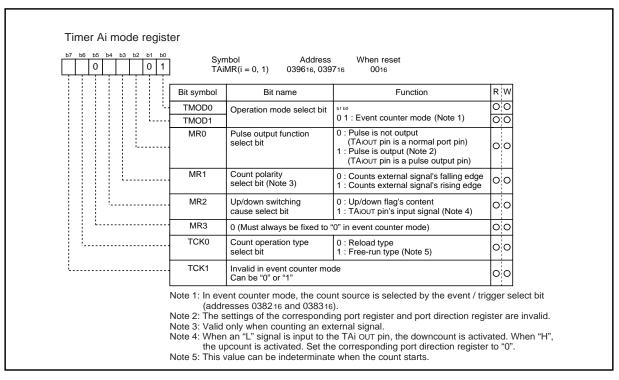

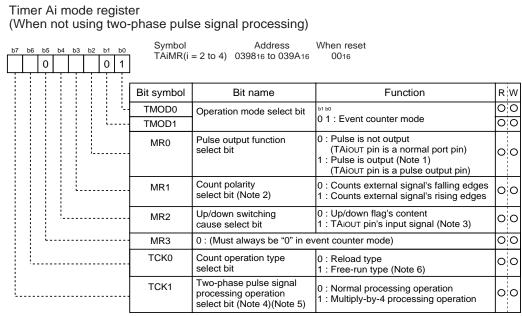

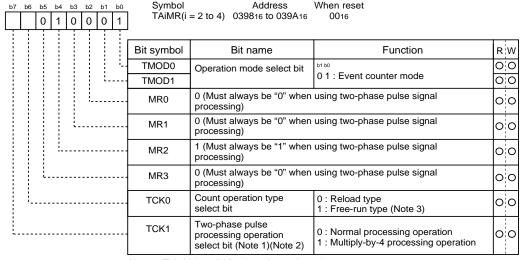

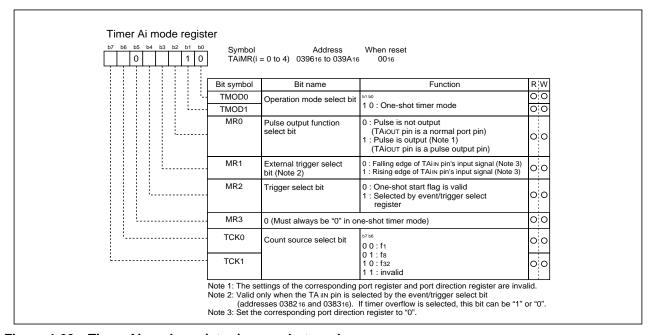

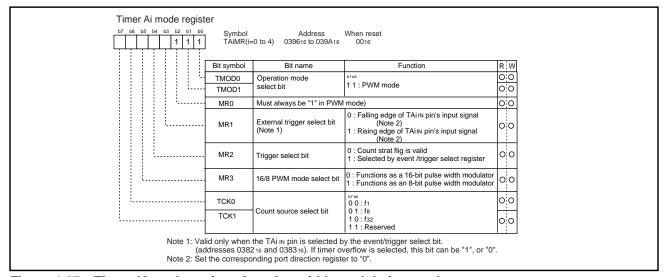

| 0396 <sub>16</sub> | Timer A0 mode register                      | TAOMR   | 0016              |  |

| 0397 <sub>16</sub> | Timer A1 mode register                      | TA1MR   | 0016              |  |

| 0398 <sub>16</sub> | Timer A2 mode register                      | TA2MR   | 0016              |  |

| 0399 <sub>16</sub> | Timer A3 mode register                      | TA3MR   | 0016              |  |

| 039A <sub>16</sub> | Timer A4 mode register                      | TA4MR   | 0016              |  |

| 039B <sub>16</sub> | Timer B0 mode register                      | TB0MR   | 0 0 ? 0 0 0 0     |  |

| 039C <sub>16</sub> | Timer B1 mode register                      | TB1MR   | 0 0 ? 0 0 0 0     |  |

| 039D <sub>16</sub> | Timer B2 mode register                      | TB2MR   | 0 0 ? 0 0 0 0     |  |

| 039E <sub>16</sub> |                                             |         |                   |  |

| 039F <sub>16</sub> |                                             | l       |                   |  |

| 03A0 <sub>16</sub> | UART0 transmit / receive mode register      | U0MR    | 0016              |  |

| 03A1 <sub>16</sub> | UART0 bit rate generator                    | U0BRG   |                   |  |

| 03A2 <sub>16</sub> | UART0 transmit buffer register              | U0TB    |                   |  |

| 03A3 <sub>16</sub> |                                             |         | 00                |  |

| 03A4 <sub>16</sub> | UART0 transmit / receive control register 0 | U0C0    | 08 <sub>16</sub>  |  |

| 03A5 <sub>16</sub> | UART0 transmit / receive control register 1 | U0C1    | 02 <sub>16</sub>  |  |

| 03A6 <sub>16</sub> | UART0 receive buffer register               | U0RB    |                   |  |

| 03A7 <sub>16</sub> |                                             |         |                   |  |

| 03A8 <sub>16</sub> | UART1 transmit / receive mode register      | U1MR    | 0016              |  |

| 03A9 <sub>16</sub> | UART1 bit rate generator                    | U1BRG   |                   |  |

| 03AA <sub>16</sub> | UART1 transmit buffer register              | U1TB    |                   |  |

| 03AB <sub>16</sub> |                                             |         |                   |  |

| 03AC <sub>16</sub> | UART1 transmit / receive control register 0 | U1C0    | 08 <sub>16</sub>  |  |

| 03AD <sub>16</sub> | UART1 transmit / receive control register 1 | U1C1    | 02 <sub>16</sub>  |  |

| 03AE <sub>16</sub> | UART1 receive buffer register               | U1RB    |                   |  |

| 03AF <sub>16</sub> |                                             | ]       |                   |  |

|                    |                                             |         |                   |  |

| Address                                  | Register name                              | Acronym   | Value after reset |  |

|------------------------------------------|--------------------------------------------|-----------|-------------------|--|

| 03B0 <sub>16</sub>                       | UART transmit / receive control register 2 | UCON      | 00000000          |  |

| 03B1 <sub>16</sub><br>03B2 <sub>16</sub> |                                            | +         |                   |  |

| 03B3 <sub>16</sub>                       |                                            | †         |                   |  |

| 03B4 <sub>16</sub>                       |                                            |           |                   |  |

| 03B5 <sub>16</sub>                       |                                            | 1         |                   |  |

| 03B6 <sub>16</sub>                       |                                            | 4         |                   |  |

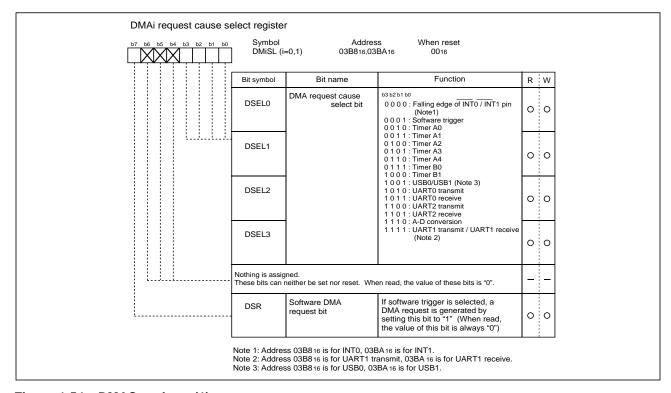

| 03B7 <sub>16</sub><br>03B8 <sub>16</sub> | DMA0 cause select register                 | DMOSL     | 00 <sub>16</sub>  |  |

| 03B9 <sub>16</sub>                       | 2to cauco co.cot regioto.                  |           | 2.10              |  |

| 03BA <sub>16</sub>                       | DMA1 cause select register                 | DM1SL     | 0016              |  |

| 03BB <sub>16</sub>                       |                                            |           |                   |  |

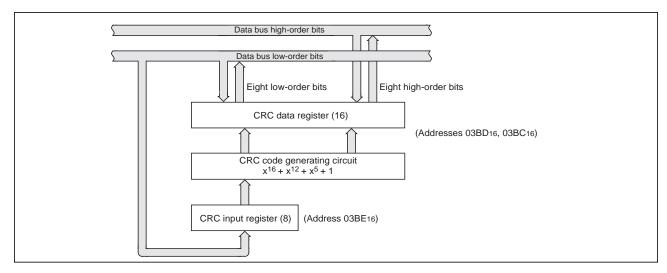

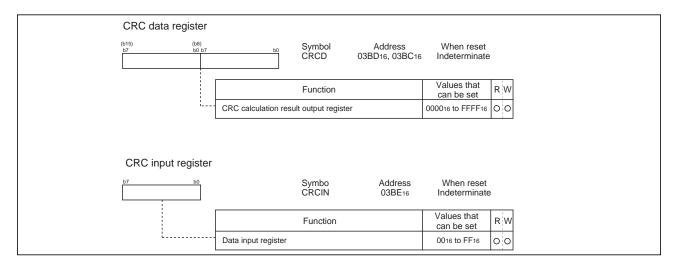

| 03BC <sub>16</sub><br>03BD <sub>16</sub> | CRC data register                          | CRCD      |                   |  |

| 03BE <sub>16</sub>                       | CRC input register                         | CRCIN     |                   |  |

| 03BF <sub>16</sub>                       |                                            |           |                   |  |

| 03C0 <sub>16</sub>                       | A-D register 0                             | AD0       |                   |  |

| 03C1 <sub>16</sub>                       | 7. 2                                       | 1         |                   |  |

| 03C2 <sub>16</sub><br>03C3 <sub>16</sub> | A-D register 1                             | AD1       |                   |  |

| 03C4 <sub>16</sub>                       | A.B. and interest                          | 1,50      |                   |  |

| 03C5 <sub>16</sub>                       | A-D register 2                             | AD2       |                   |  |

| 03C6 <sub>16</sub>                       | A-D register 3                             | AD3       |                   |  |

| 03C7 <sub>16</sub><br>03C8 <sub>16</sub> |                                            | -         |                   |  |

| 03C0 <sub>16</sub>                       | A-D register 4                             | AD4       |                   |  |

| 03CA <sub>16</sub>                       | A D register 5                             | 1,55      |                   |  |

| 03CB <sub>16</sub>                       | A-D register 5                             | AD5       |                   |  |

| 03CC <sub>16</sub>                       | A-D register 6                             | AD6       |                   |  |

| 03CD <sub>16</sub><br>03CE <sub>16</sub> |                                            | -         |                   |  |

| 03CF <sub>16</sub>                       | A-D register 7                             | AD7       |                   |  |

| 03D0 <sub>16</sub>                       |                                            |           |                   |  |

| 03D1 <sub>16</sub>                       |                                            |           |                   |  |

| 03D2 <sub>16</sub>                       |                                            | -         |                   |  |

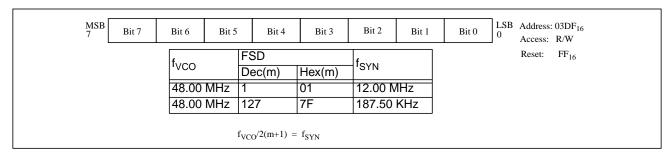

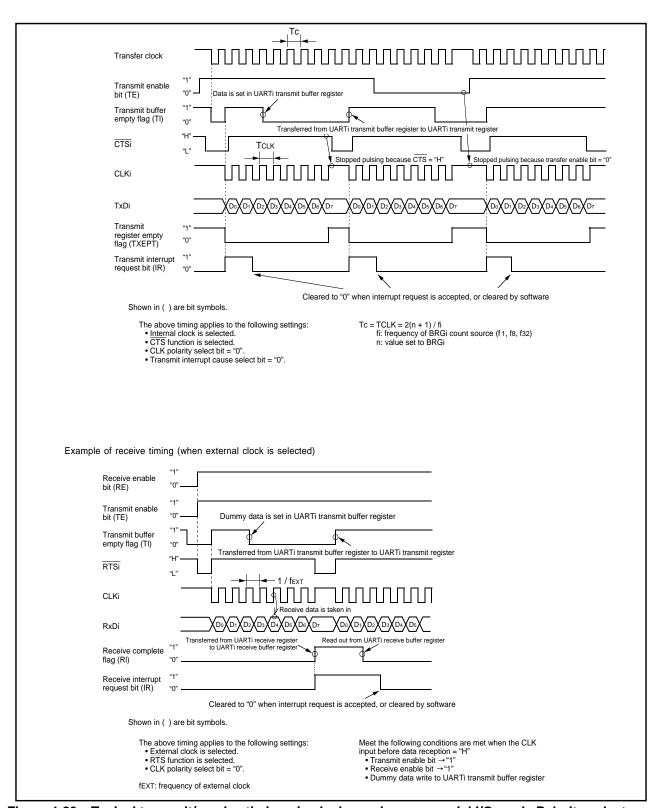

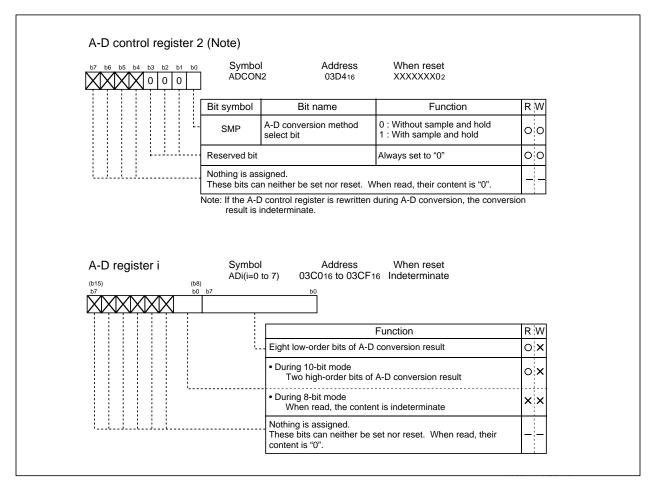

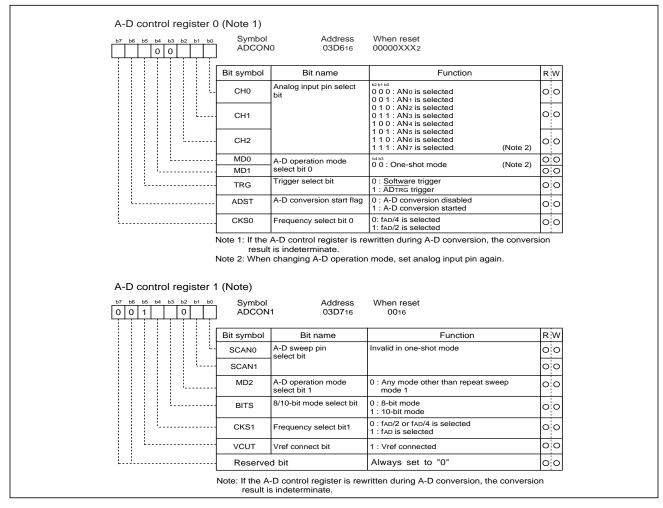

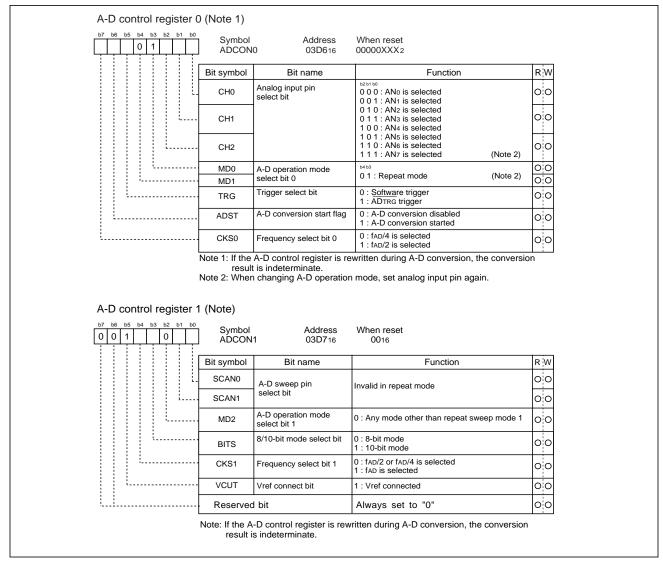

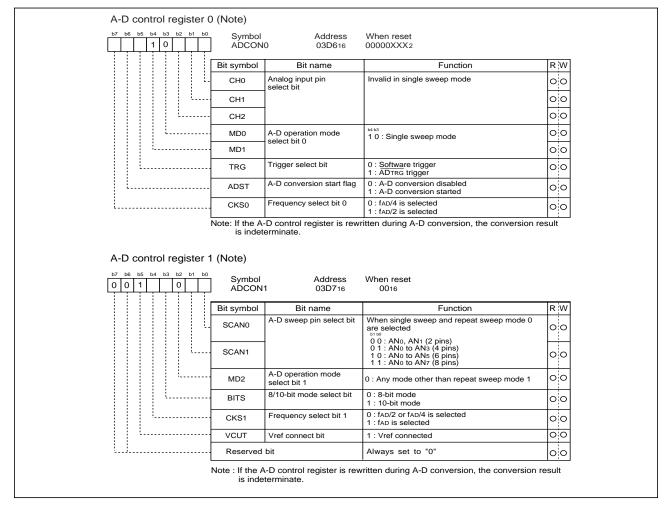

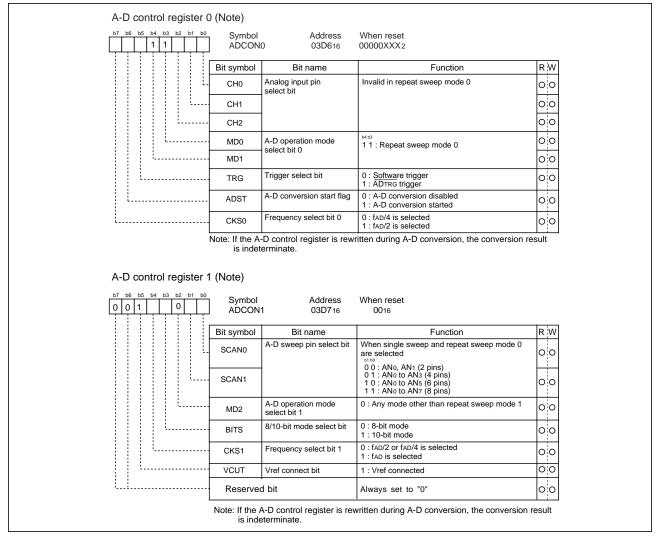

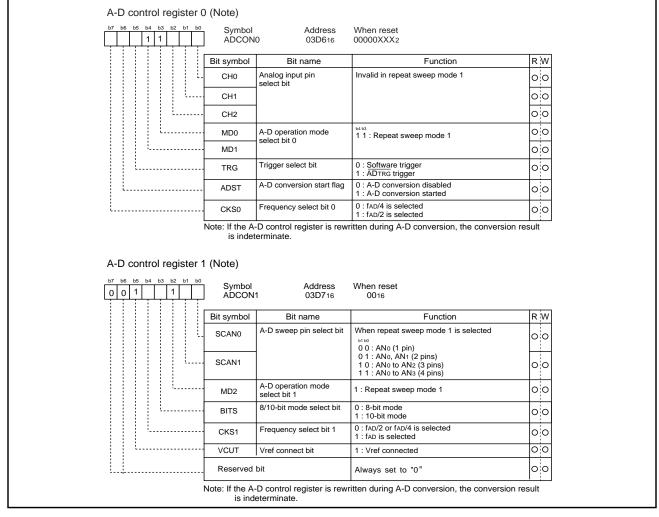

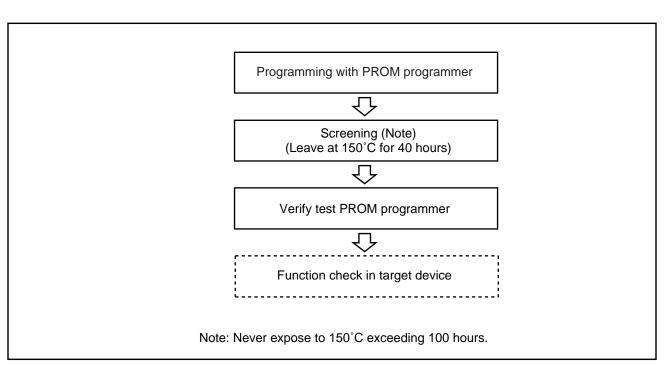

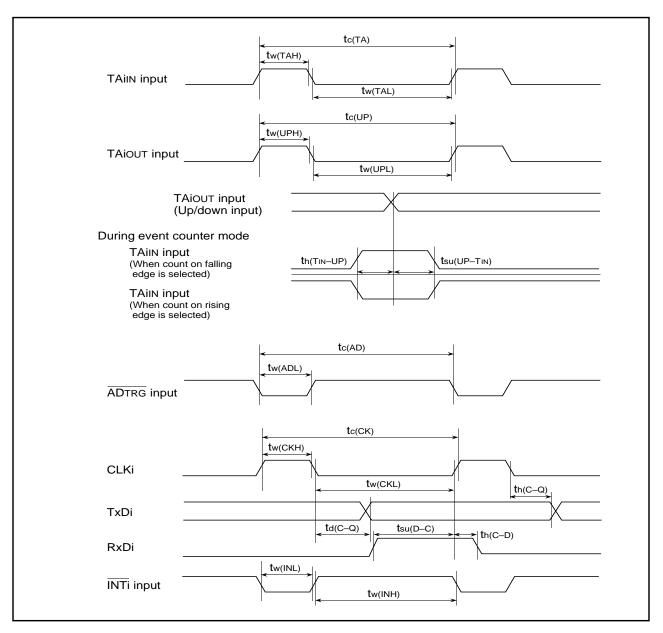

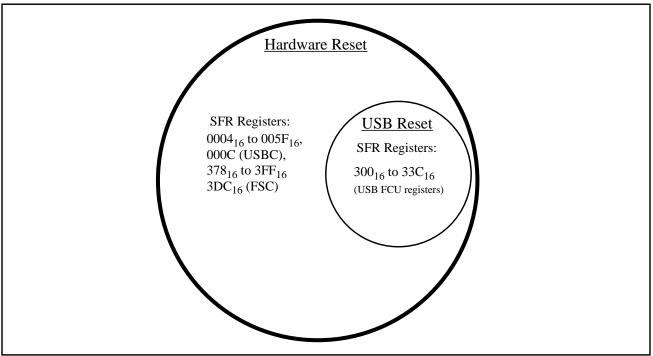

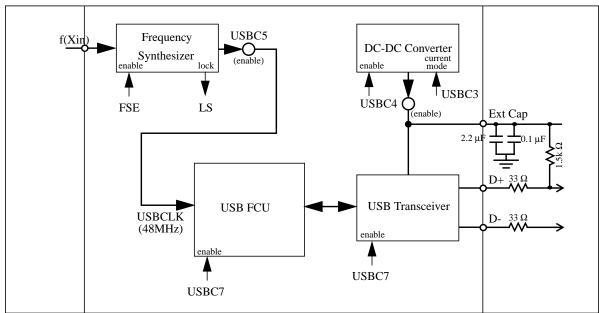

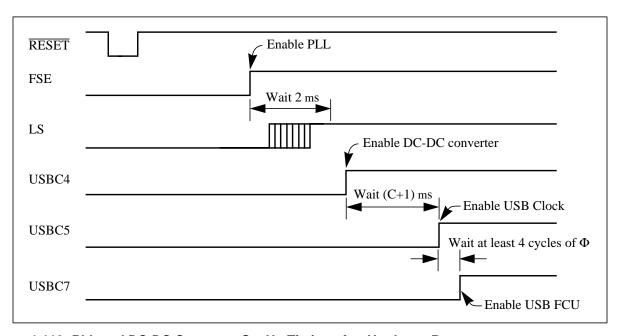

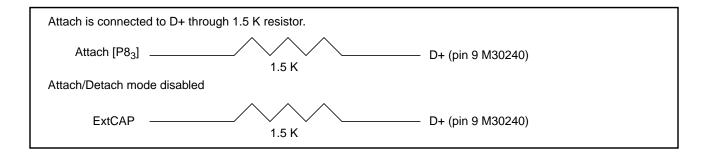

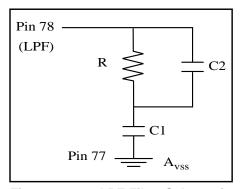

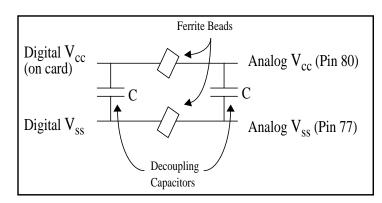

| 03D3 <sub>16</sub><br>03D4 <sub>16</sub> | A-D control register 2                     | ADCON2    | 0                 |  |