# Regarding the change of names mentioned in the document, such as Mitsubishi Electric and Mitsubishi XX, to Renesas Technology Corp.

The semiconductor operations of Hitachi and Mitsubishi Electric were transferred to Renesas Technology Corporation on April 1st 2003. These operations include microcomputer, logic, analog and discrete devices, and memory chips other than DRAMs (flash memory, SRAMs etc.) Accordingly, although Mitsubishi Electric, Mitsubishi Electric Corporation, Mitsubishi Semiconductors, and other Mitsubishi brand names are mentioned in the document, these names have in fact all been changed to Renesas Technology Corp. Thank you for your understanding. Except for our corporate trademark, logo and corporate statement, no changes whatsoever have been made to the contents of the document, and these changes do not constitute any alteration to the contents of the document itself.

Note : Mitsubishi Electric will continue the business operations of high frequency & optical devices and power devices.

Renesas Technology Corp. Customer Support Dept. April 1, 2003

## Description

The M30220 group of single-chip microcomputers are built using the high-performance silicon gate CMOS process using a M16C/60 Series CPU core. The M30220 group has LCD controller/driver. M30220 group is packaged in a 144-pin plastic molded QFP. These single-chip microcomputers operate using sophisticated instructions featuring a high level of instruction efficiency. With 1M bytes of address space, they are capable of executing instructions at high speed.

## Features

| Basic machine instructions          | •                                                                       |

|-------------------------------------|-------------------------------------------------------------------------|

| Memory capacity                     | See figure memory expansion                                             |

| Shortest instruction execution time | 100ns (f(XIN)=10MHz)                                                    |

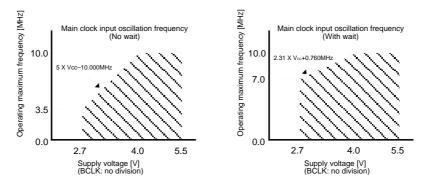

| Supply voltage                      | 4.0V to 5.5V (f(XIN)=10MHz)                                             |

|                                     | 2.7V to 5.5V (f(XIN)=7MHz with software one-wait)                       |

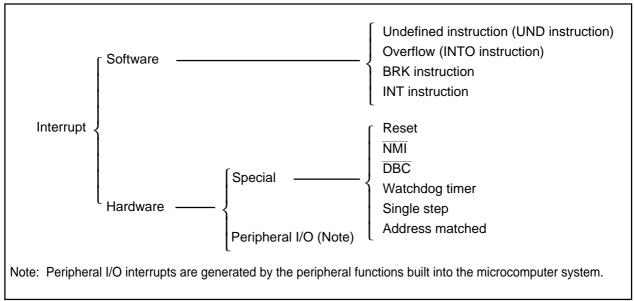

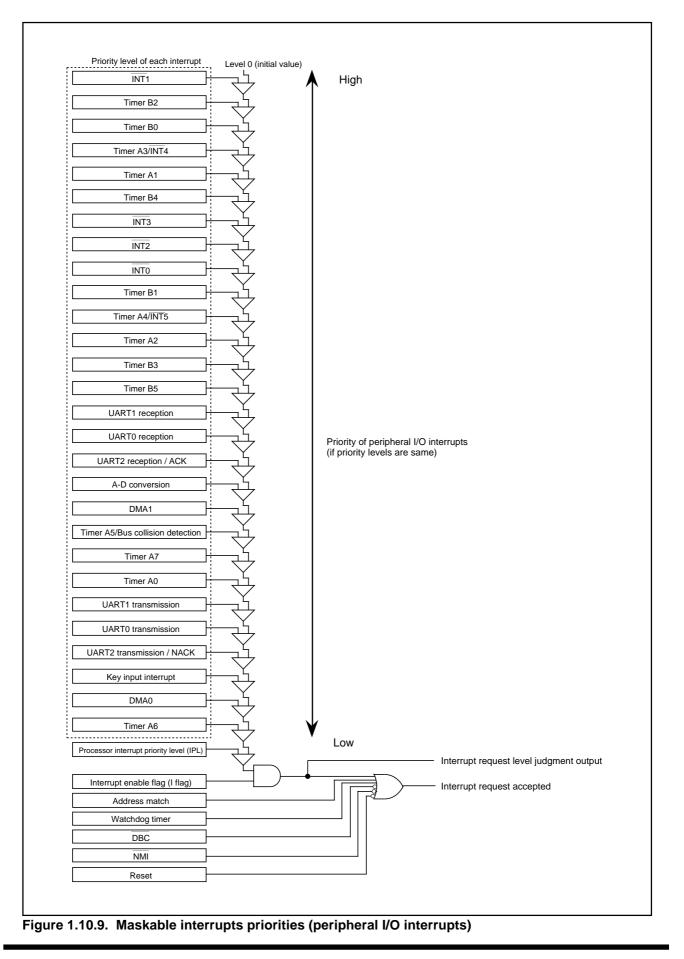

| Interrupts                          | 26 internal and 8 external interrupt sources, 4 software, 7 levels      |

|                                     | (including key input interrupt)                                         |

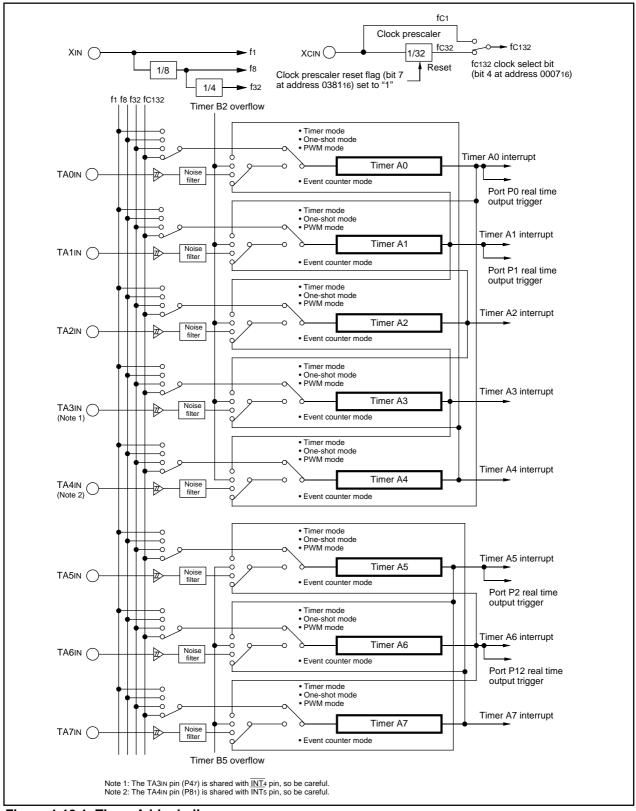

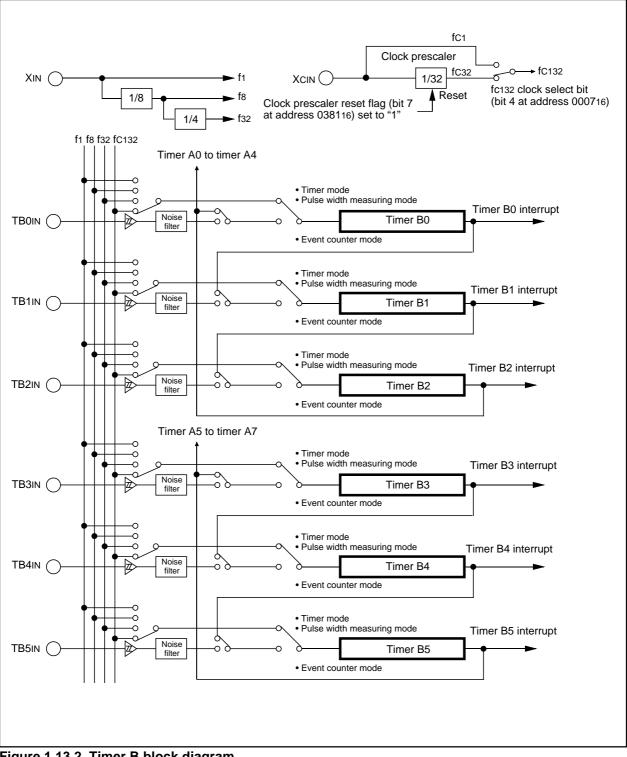

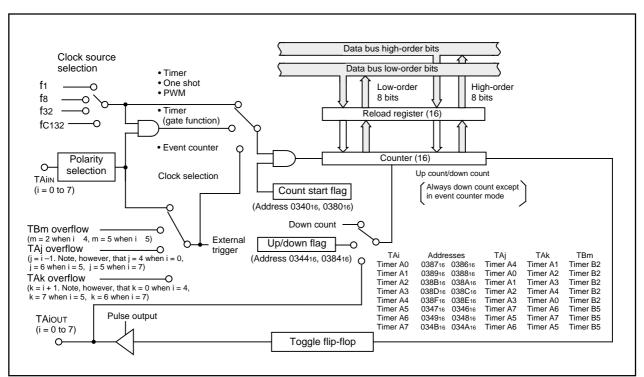

| Multifunction 16-bit timer          | Timer A (output) x 8, timer B (input) x 6                               |

| Real time port outputs              |                                                                         |

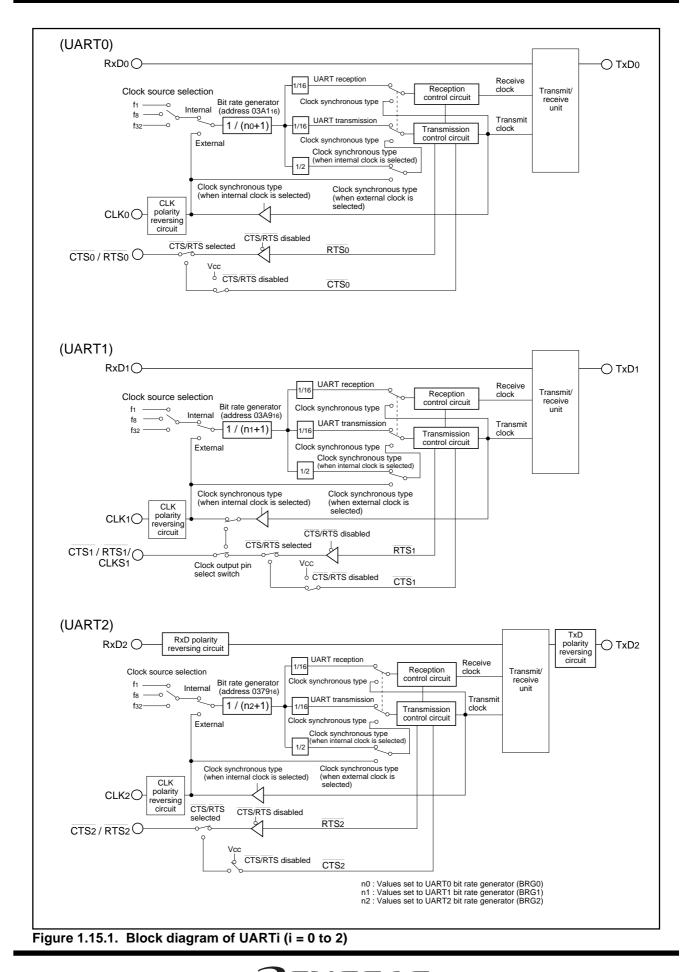

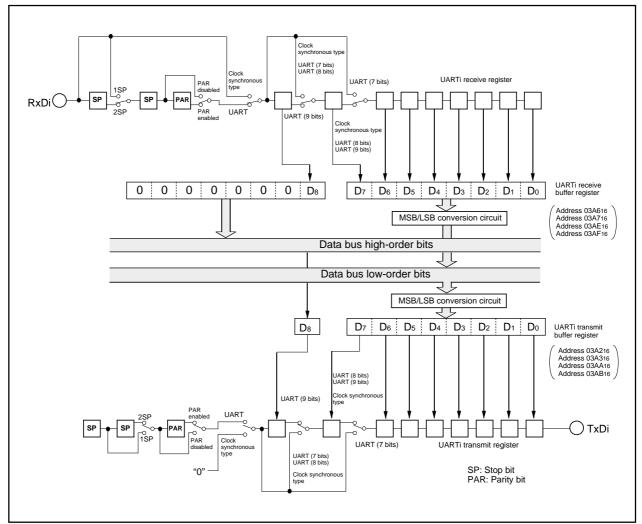

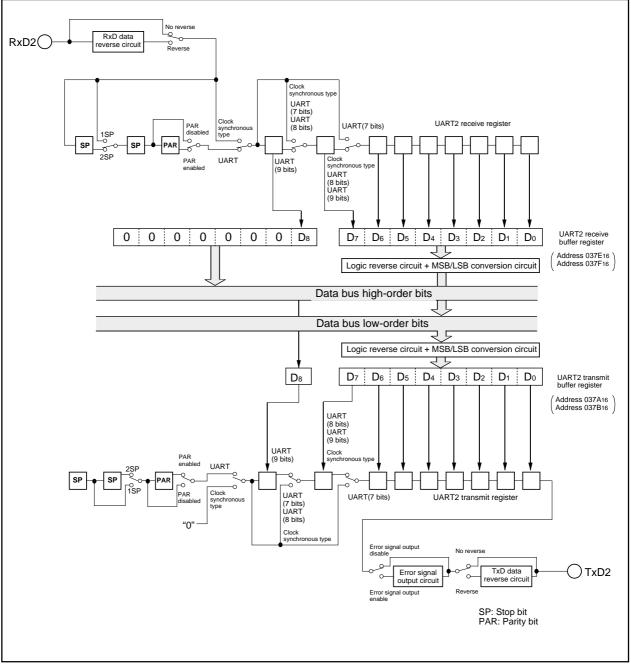

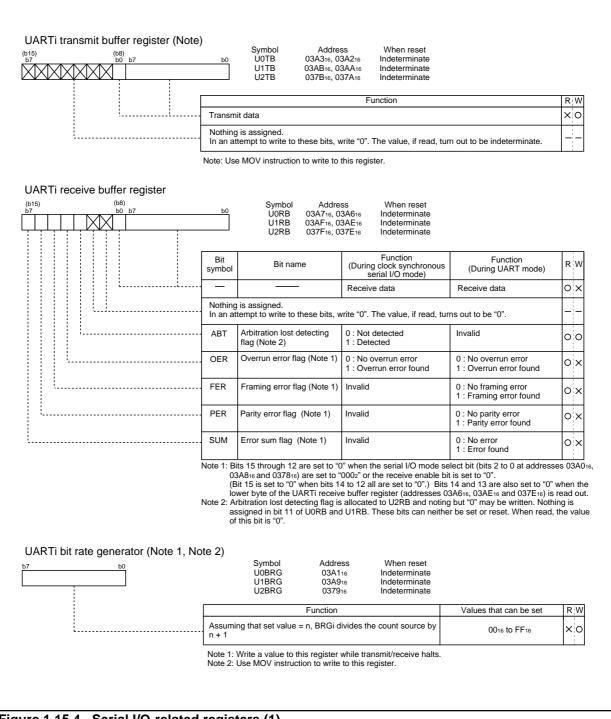

| • Serial I/O                        | 3 channel for UART or clock synchronous                                 |

| • DMAC                              | 2 channels (trigger: 26 sources)                                        |

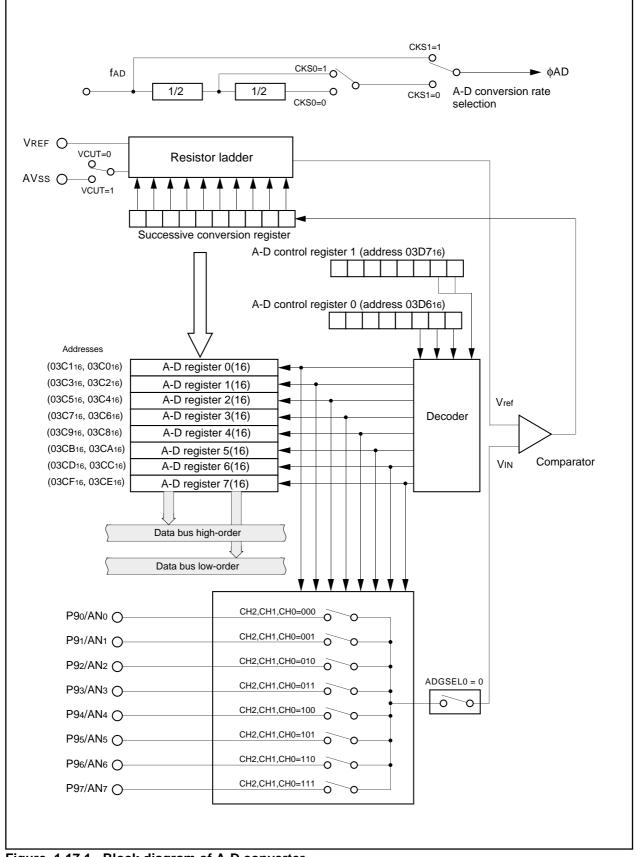

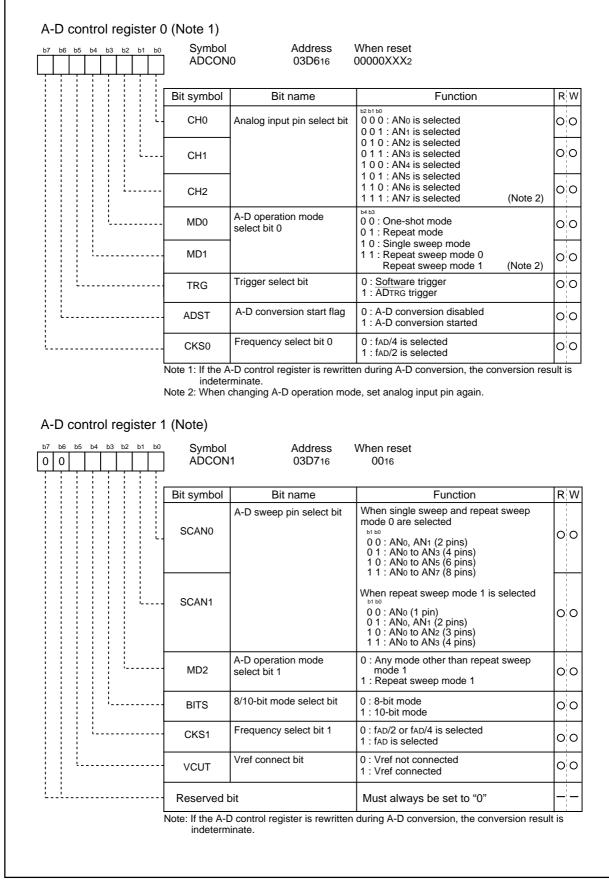

| • A-D converter                     | 10 bits X 8 channels                                                    |

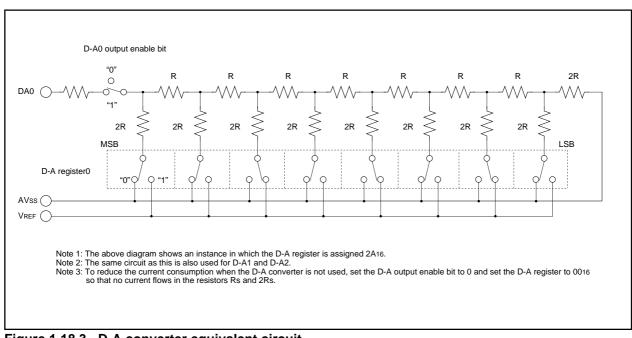

| • D-A converter                     | 8 bits X 3 channels                                                     |

| Watchdog timer                      | 1 line                                                                  |

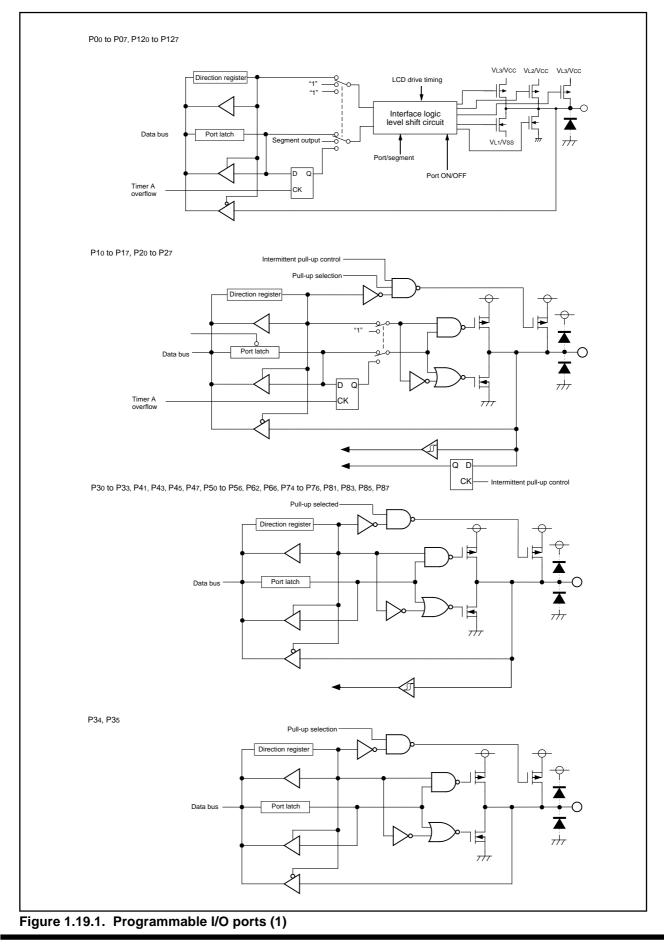

| Programmable I/O                    | 104 lines (32 lines are shared with LCD outputs)                        |

| Output port                         | 16 lines (shared with LCD outputs)                                      |

| Input port                          | 1 line (P77, shared with NMI pin)                                       |

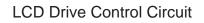

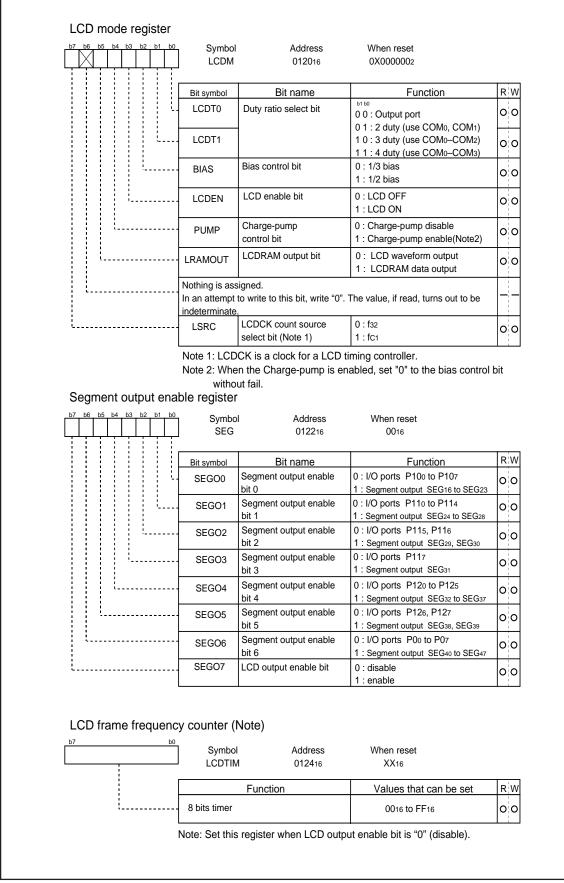

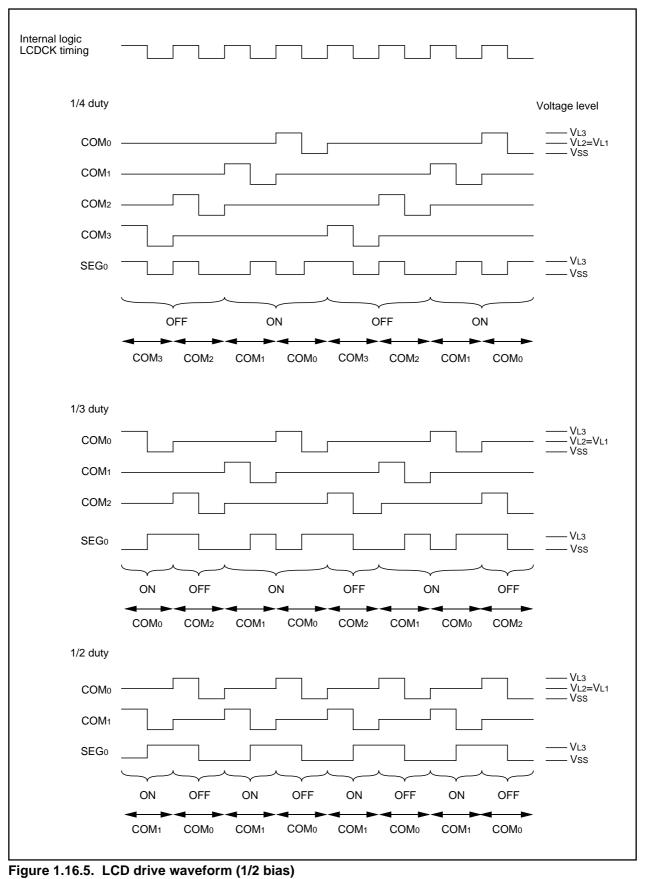

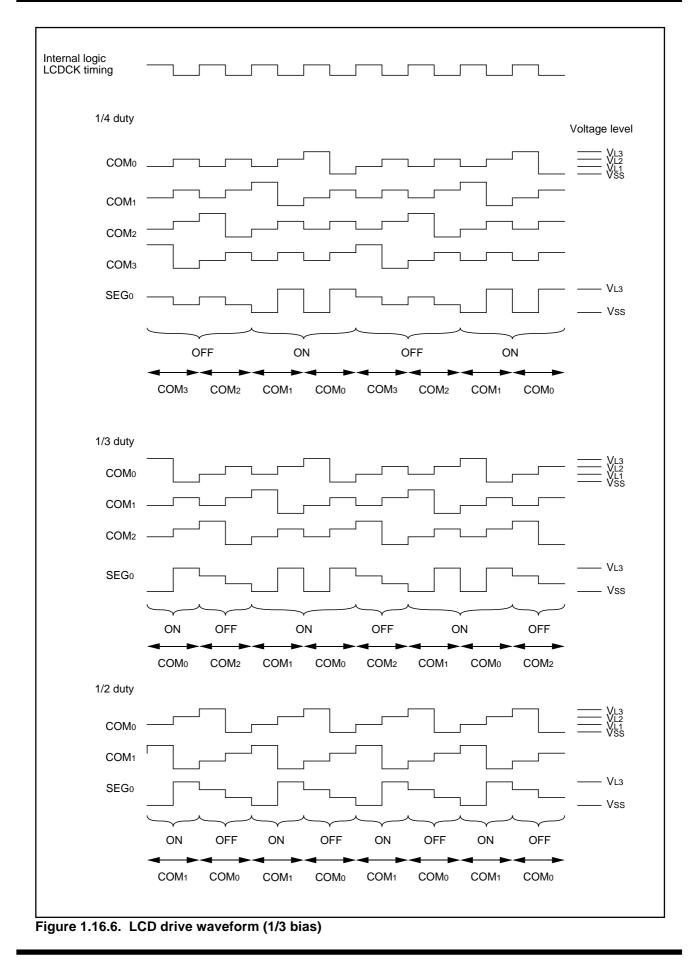

| LCD drive control circuit           | 1/2, 1/3 bias                                                           |

|                                     | 2, 3 and 4 time sharing                                                 |

|                                     | 4 common outputs                                                        |

|                                     | 48 segment outputs                                                      |

|                                     | built-in Charge-pump                                                    |

| Key input interrupt                 | 20 lines                                                                |

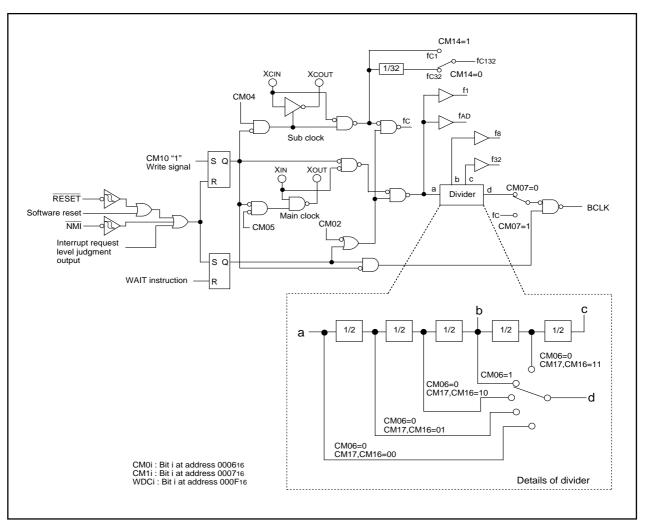

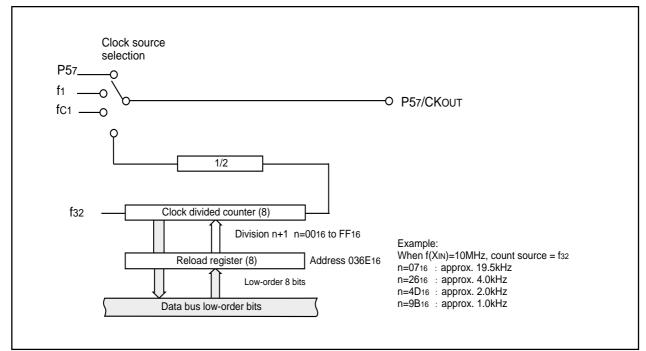

| Clock generating circuit            | 2 built-in clock generation circuits                                    |

|                                     | (built-in feedback resistor, and external ceramic or quartz oscillator) |

|                                     |                                                                         |

## Applications

Camera, Home appliances, Portable equipment, Drop meter, Audio, Office equipment, etc.

## -----Table of Contents-----

| Central Processing Unit (CPU) | 9  |

|-------------------------------|----|

| Reset                         |    |

| Clock Generating Circuit      |    |

| Protection                    |    |

| Interrupt                     |    |

| Watchdog Timer                |    |

| DMAC                          | 55 |

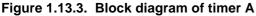

| Timer                         | 65 |

| Real time Port            | 85  |

|---------------------------|-----|

| Serial I/O                | 87  |

| LCD Drive Control Circuit | 123 |

| A-D Converter             | 130 |

| D-A Converter             | 140 |

| Programmable I/O Port     | 142 |

| Electric Characteristics  | 155 |

| Flash Memory Version      | 171 |

## **Pin Configuration**

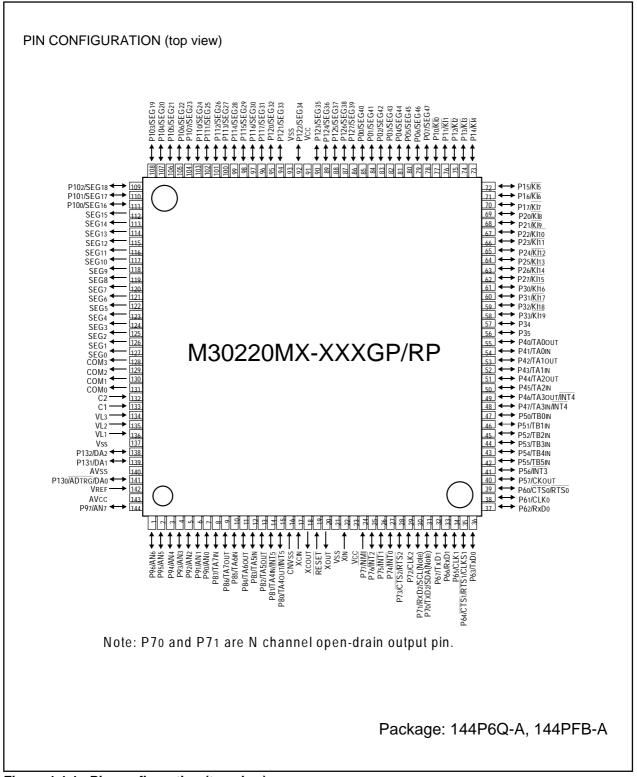

Figure 1.1.1 shows the pin configurations (top view).

Figure 1.1.1. Pin configuration (top view)

#### **Block Diagram**

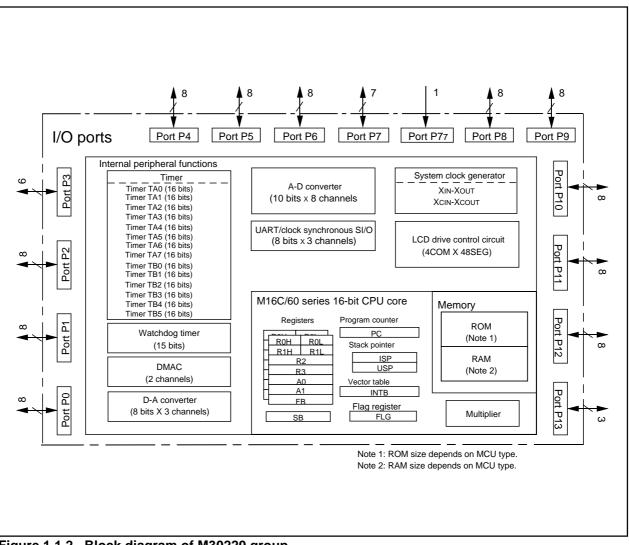

Figure 1.1.2 is a block diagram of the M30220 group.

Figure 1.1.2. Block diagram of M30220 group

## **Performance Outline**

Table 1.1.1 is performance outline of M30220 group.

Table 1.1.1. Performance outline of M30220 group

| Item                         |                                 |                | Performance                                            |  |

|------------------------------|---------------------------------|----------------|--------------------------------------------------------|--|

| Number of basic instructions |                                 | 6              | 91 instructions                                        |  |

| Shortest instr               | uction execution                | on time        | 100ns (f(XIN)=10MHz                                    |  |

| Memory                       | ROM                             |                | 96 Kbytes                                              |  |

| capacity                     | RAM                             |                | 6 Kbytes                                               |  |

| I/O port                     | P0 to P13 (e)                   | xcept P77)     | 8 bits x 11, 3 bits x 1, 6 bits x 1, 7 bits x 1        |  |

| Input port                   | P77                             |                | 1 bit x 1                                              |  |

| Output port                  | SEG0 to SEC                     | G15            | 2 bits x 8                                             |  |

| Multifunction                | TA0 to TA7                      |                | 16 bits x 8                                            |  |

| timer                        | TB0 to TB5                      |                | 16 bits x 6                                            |  |

| Real time por                | t outputs                       |                | 8 bits x 4 lines                                       |  |

| Serial I/O                   | UART0 to UA                     | ART2           | (UART or clock synchronous) x 3                        |  |

| A-D converte                 | r                               |                | 10 bits x 8 channels                                   |  |

| D-A converte                 | r                               |                | 8 bits x 3 channels                                    |  |

| DMAC                         |                                 |                | 2 channel(trigger:26 sources)                          |  |

| LCD                          | COM0 to COM3                    |                | 4 lines                                                |  |

|                              | SEG0 to SEG47                   |                | 48 lines (32 lines are shared with I/O ports)          |  |

| Watchdog tim                 | ner                             |                | 15 bits x 1 (with prescaler)                           |  |

| Interrupt                    |                                 |                | 26 internal and 8 external sources, 4 software sources |  |

| Clock genera                 | ting circuit                    |                | 2 built-in clock generation circuits                   |  |

|                              |                                 |                | (built-in feedback resistor, and external ceramic or   |  |

|                              |                                 |                | quartz oscillator)                                     |  |

| Supply voltag                | je                              |                | 4.0V to 5.5V (f(XIN)=10MHz)                            |  |

|                              |                                 |                | 2.7V to 5.5V (f(XIN)=7MHz with software one-wait)      |  |

| Power consumption            |                                 |                | 18mW (Vcc=3V, f(XIN)=7MHz with software one-wait)      |  |

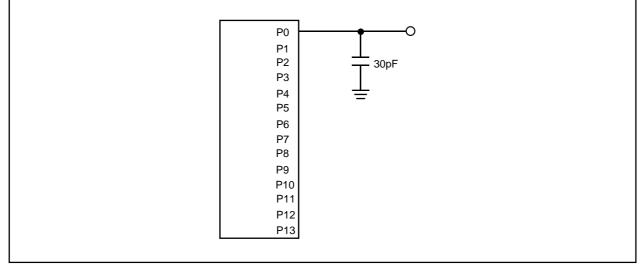

| I/O char-                    | O withstand voltage (P0 to P13) |                | 5 V                                                    |  |

| acteristics (                | Dutput current                  | P1 to P9,P13   | 5 mA                                                   |  |

|                              |                                 | P0, P10 to P12 | 0.1mA("H" output), 2.5mA("L" output)                   |  |

| Device configuration         |                                 |                | CMOS high-performance silicon gate                     |  |

| Package                      |                                 |                | 144-pin plastic mold QFP                               |  |

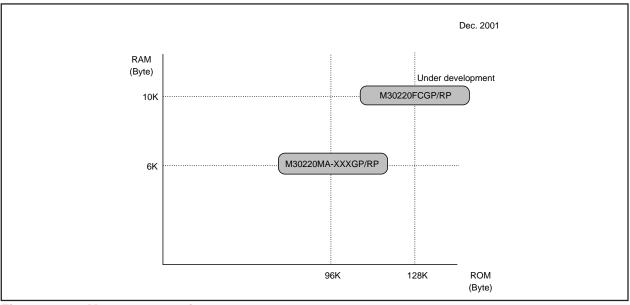

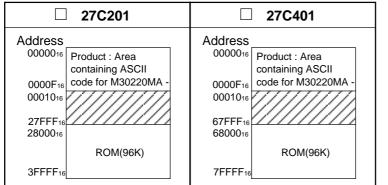

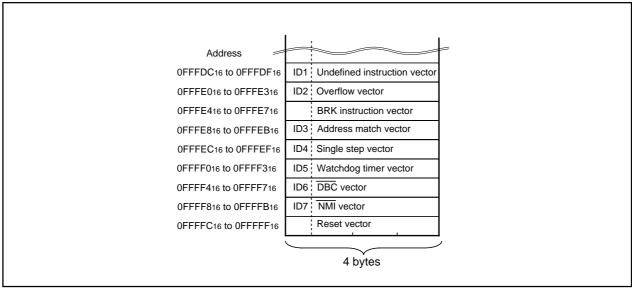

Mitsubishi plans to release the following products in the M30220 group:

(1) Support for mask ROM version, flash memory version

- (2) ROM capacity

- (3) Package

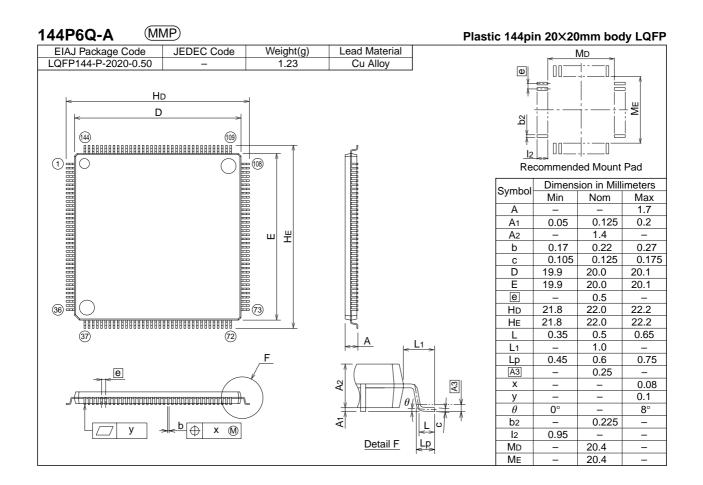

144P6Q-A : Plastic molded QFP (mask ROM and flash memory versions)

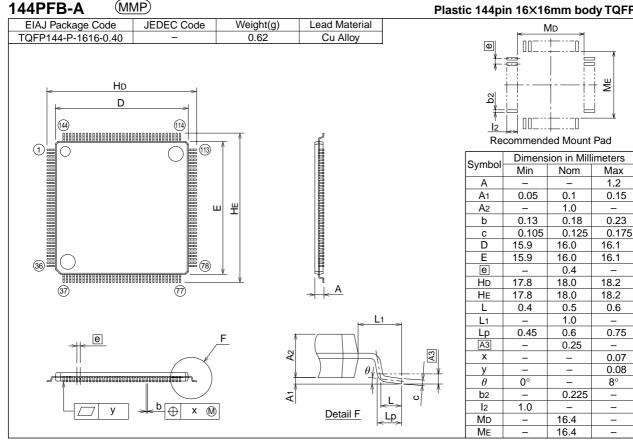

144PFB-A : Plastic molded QFP(mask ROM and flash memory versions)

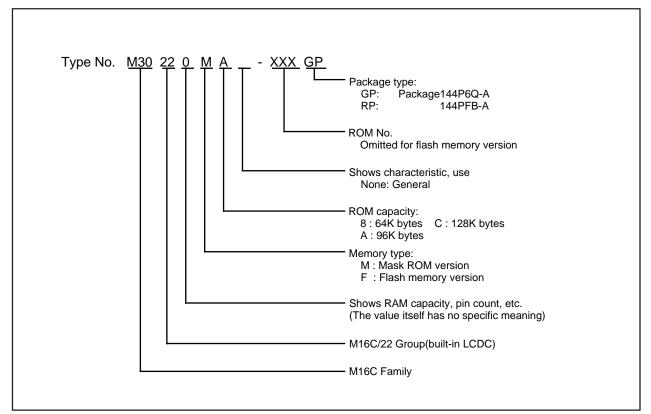

Figure 1.1.3 shows the ROM expansion and figure 1.1.4 shows the Type No., memory size, and package.

Figure 1.1.4. Type No., memory size, and package

## **Pin Description**

## **Pin Description**

| Pin name      | Signal name                 | I/O    | Function                                                                                                                                                                                                                                                                                                                                                          |

|---------------|-----------------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

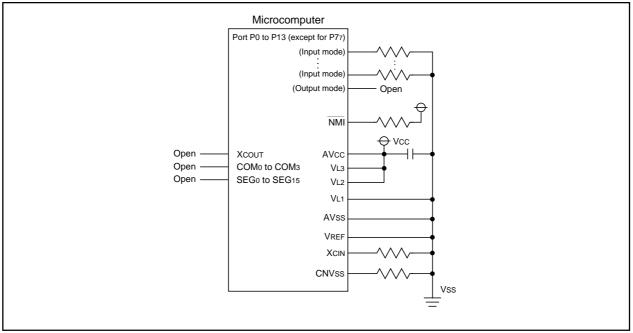

| Vcc, Vss      | Power supply input          |        | Supply 2.7 to 5.5 V to the Vcc pin. Supply 0 V to the Vss pin.                                                                                                                                                                                                                                                                                                    |

| CNVss         | CNVss                       | I      | Connect it to the Vss pin via resistor.                                                                                                                                                                                                                                                                                                                           |

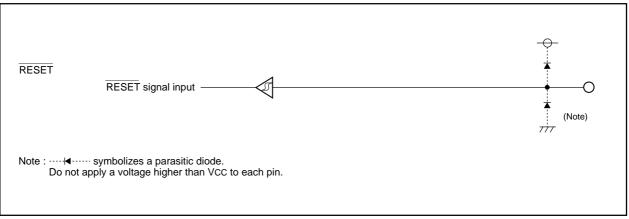

| RESET         | Reset input                 | I      | A "L" on this input resets the microcomputer.                                                                                                                                                                                                                                                                                                                     |

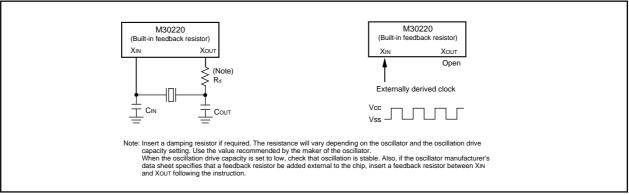

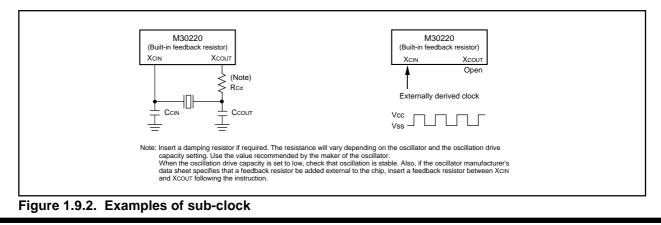

| Xin<br>Xout   | Clock input<br>Clock output | і<br>О | These pins are provided for the main clock generating circuit.<br>Connect a ceramic resonator or crystal between the XIN and the<br>XOUT pins. To use an externally derived clock, input it to the XIN<br>pin and leave the XOUT pin open.                                                                                                                        |

| Хсім<br>Хсоит | Clock input<br>Clock output | і<br>О | These pins are provided for the sub clock generating circuit.<br>Connect a ceramic resonator or crystal between the XCIN and the<br>XCOUT pins. To use an externally derived clock, input it to the<br>XCIN pin and leave the XCOUT pin open.                                                                                                                     |

| AVcc          | Analog power supply input   |        | This pin is a power supply input for the A-D converter. Connect it to Vcc.                                                                                                                                                                                                                                                                                        |

| AVss          | Analog power supply input   |        | This pin is a power supply input for the A-D converter. Connect it to Vss.                                                                                                                                                                                                                                                                                        |

| Vref          | Reference<br>voltage input  | I      | This pin is a reference voltage input for the A-D converter.                                                                                                                                                                                                                                                                                                      |

| P00 to P07    | I/O port P0                 | I/O    | This is an 8-bit CMOS I/O port. It has an input/output port direction register that allows the user to set each pin for input or output individually. When set for input, the user can specify in units of four bits via software whether or not they are tied to a pull-up resistor. Pins in this port also use as LCD segment output and real time port output. |

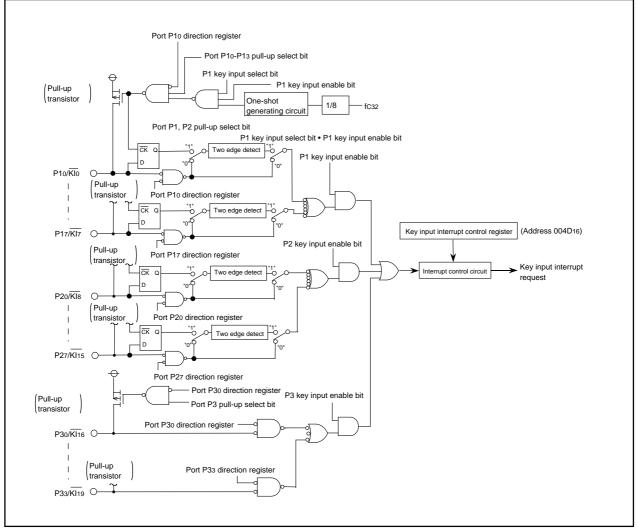

| P10 to P17    | I/O port P1                 | I/O    | This is an 8-bit I/O port equivalent to P0. Pins in this port also function as input pins for the key input interrupt function and real time port output.                                                                                                                                                                                                         |

| P20 to P27    | I/O port P2                 | I/O    | This is an 8-bit I/O port equivalent to P0. Pins in this port also function as input pins for the key input interrupt function and real time port output.                                                                                                                                                                                                         |

| P30 to P35    | I/O port P3                 | I/O    | This is a 6-bit I/O port equivalent to P0. P30 to P33 also function as input pins for the key input interrupt function.                                                                                                                                                                                                                                           |

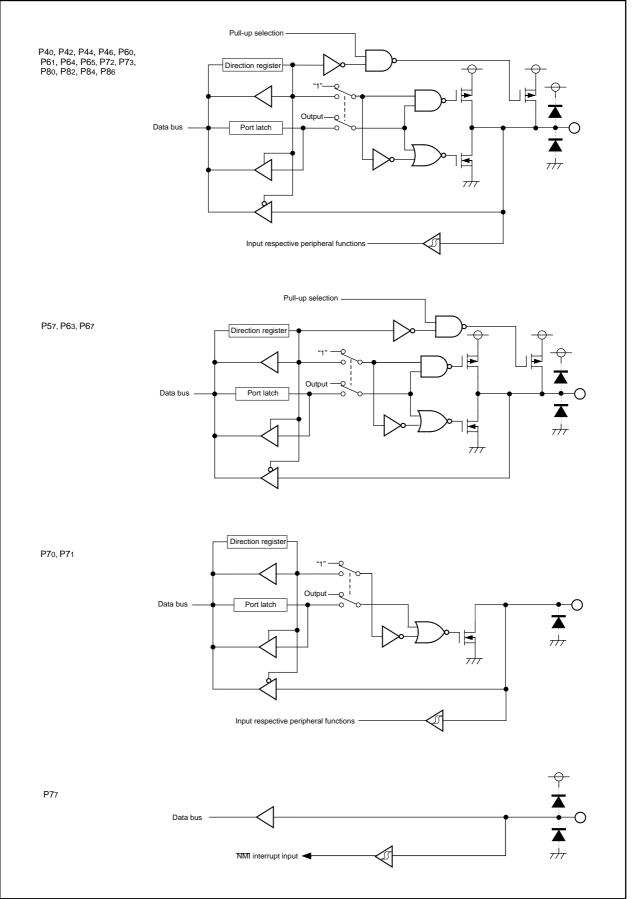

| P40 to P47    | I/O port P4                 | I/O    | This is a 8-bit I/O port equivalent to $\underline{P0}$ . Pins in this port also function as timer A0 to A3 I/O pins, INT4 input pin as selected by software.                                                                                                                                                                                                     |

| P50 to P57    | I/O port P5                 | I/O    | This is a 8-bit I/O port equivalent to P0. Pins in this port also function as timer B0 to B5 and INT3 input pins, CKOUT output pin as selected by software.                                                                                                                                                                                                       |

| P60 to P67    | I/O port P6                 | I/O    | This is an 8-bit I/O port equivalent to P0. Pins in this port also function as UART0 and UART1 I/O pins as selected by software.                                                                                                                                                                                                                                  |

## **Pin Description**

## **Pin Description**

| Pin name                                | Signal name                          | I/O      | Function                                                                                                                                                                                                                                                 |

|-----------------------------------------|--------------------------------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P70 to P76<br>P77                       | I/O port P7                          | I/O<br>I | P70 to P76 are I/O ports equivalent to P0 (P70 and P71 are N channel open-drain output).<br>Pins in this port also function as UART2 I/O pin, INT0 to INT2 input pins as selected by software.<br>P77 is an input-only port that also functions for NMI. |

| P80 to P87                              | I/O port P8                          | I/O      | This is a 8-bit I/O port equivalent to P0. Pins in this port also function as timer A4 to A7 I/O pins, INT5 input pin as selected by software.                                                                                                           |

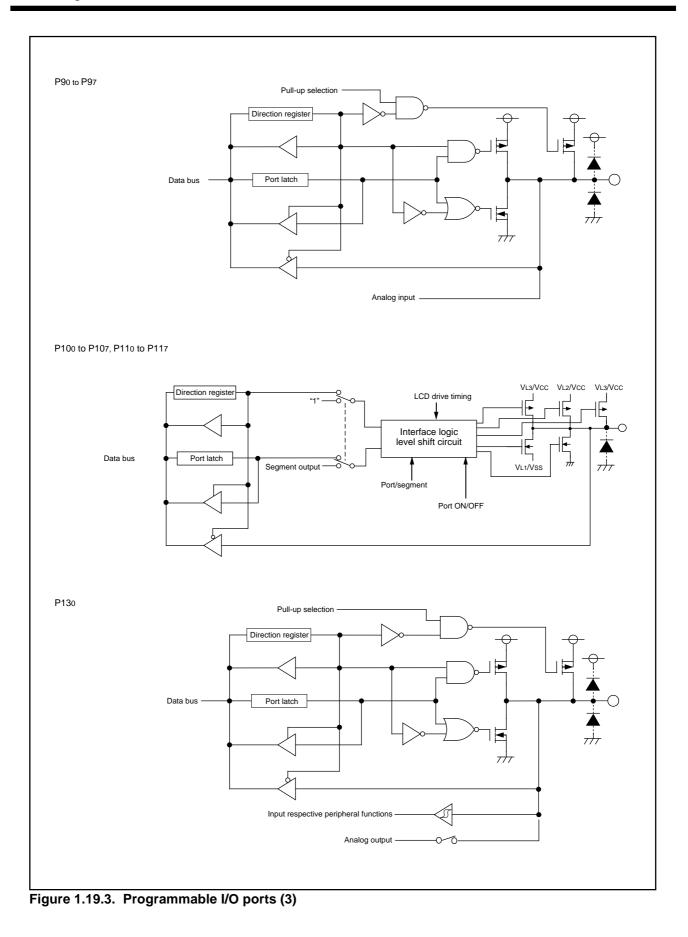

| P90 to P97                              | I/O port P9                          | I/O      | This is an 8-bit I/O port equivalent to P0. Pins in this port also function as A-D converter analog input pins as selected by software.                                                                                                                  |

| P100 to P107                            | I/O port P10                         | I/O      | This is an 8-bit I/O port equivalent to P0. Pins in this port also function as SEG output for LCD as selected by software.                                                                                                                               |

| P110 to P117                            | I/O port P11                         | I/O      | This is an 8-bit I/O port equivalent to P0. Pins in this port also function as SEG output for LCD as selected by software.                                                                                                                               |

| P120 to P127                            | I/O port P12                         | I/O      | This is an 8-bit I/O port equivalent to P0. Pins in this port also function as SEG output for LCD and real time port output.                                                                                                                             |

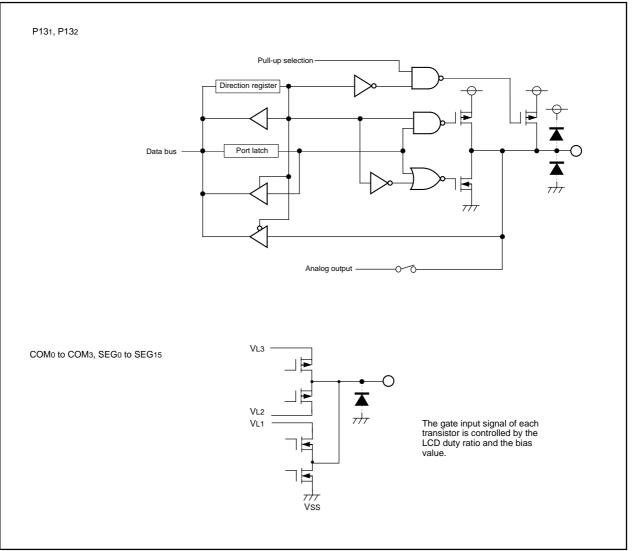

| P130 to P132                            | I/O port P13                         | I/O      | This is an 3-bit I/O port equivalent to P0. Pins in this port also function as D-A converter analog output pins or start trigger for A-D input pins.                                                                                                     |

| SEG0 to<br>SEG15                        | Segment<br>output                    | 0        | Pins in this port function as SEG output for LCD drive circuit.                                                                                                                                                                                          |

| COM <sub>0</sub> to<br>COM <sub>3</sub> | Common<br>output                     | 0        | Pins in this port function as common output for LCD drive circuit.                                                                                                                                                                                       |

| VL1 to VL3                              | Power supply input for LCD           |          | Power supply input for LCD drive circuit.                                                                                                                                                                                                                |

| C1, C2                                  | Step-up<br>condenser<br>connect port |          | Pins in this port function as external pin for LCD step-up condenser. Connect a condenser between C1 and C2.                                                                                                                                             |

## **Operation of Functional Blocks**

The M30220 group accommodates certain units in a single chip. These units include ROM and RAM to store instructions and data and the central processing unit (CPU) to execute arithmetic/logic operations. Also included are peripheral units such as timers, real time port, serial I/O, LCD drive control circuit, D-A converter, A-D converter, DMAC and I/O ports.

The following explains each unit.

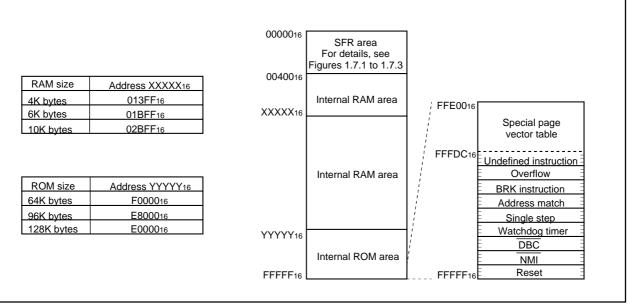

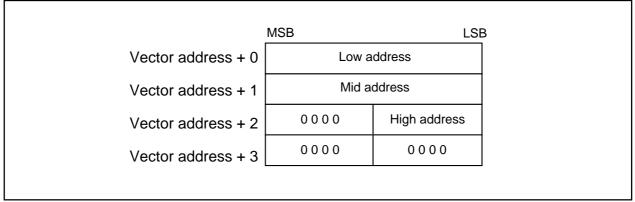

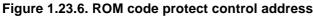

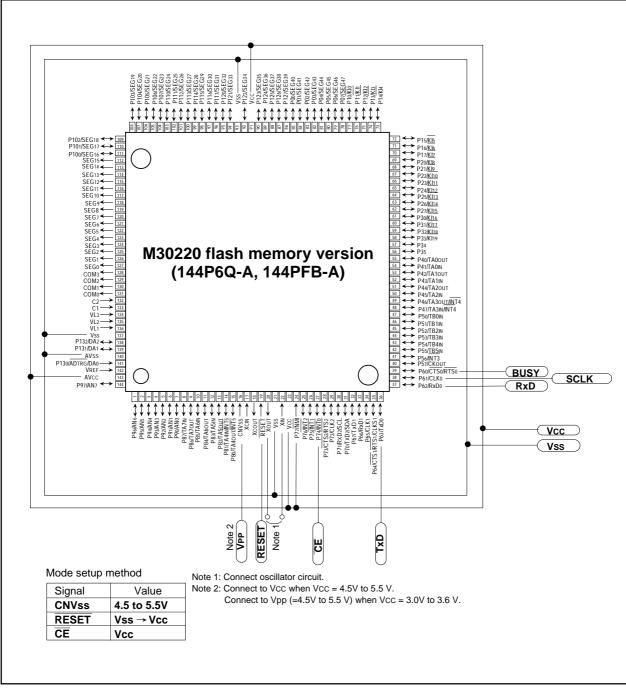

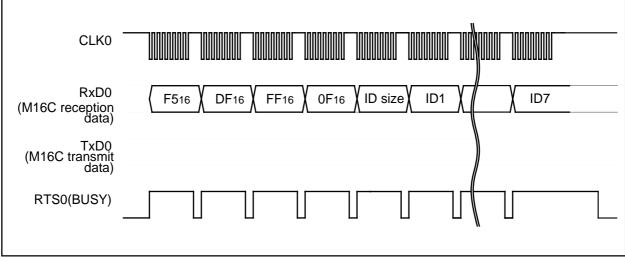

#### Memory

Figure 1.4.1 is a memory map of the M30220 group. The address space extends the 1M bytes from address 0000016 to FFFFF16. From FFFFF16 down is ROM. For example, in the M30220MA-XXXGP, there is 96K bytes of internal ROM from E800016 to FFFFF16. The vector table for fixed interrupts such as the reset and  $\overline{\text{NMI}}$  are mapped to FFFDC16 to FFFFF16. The starting address of the interrupt routine is stored here. The address of the vector table for timer interrupts, etc., can be set as desired using the internal register (INTB). See the section on interrupts for details.

From 0040016 up is RAM. For example, in the M30220MA-XXXGP, 6K bytes of internal RAM is mapped to the space from 0040016 to 01BFF16. In addition to storing data, the RAM also stores the stack used when calling subroutines and when interrupts are generated.

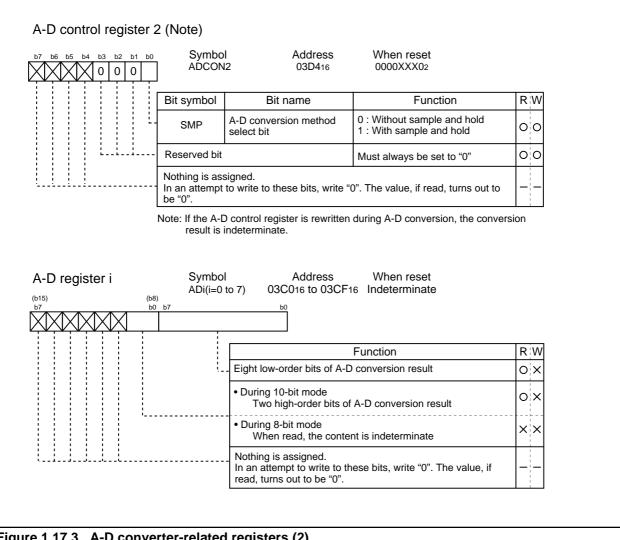

The SFR area is mapped to 0000016 to 003FF16. This area accommodates the control registers for peripheral devices such as I/O ports, A-D converter, serial I/O, timers, and LCD, etc. Figures 1.7.1 to 1.7.3 are location of peripheral unit control registers. Any part of the SFR area that is not occupied is reserved and cannot be used for other purposes.

The special page vector table is mapped to FFE0016 to FFFDB16. If the starting addresses of subroutines or the destination addresses of jumps are stored here, subroutine call instructions and jump instructions can be used as 2-byte instructions, reducing the number of program steps.

Figure 1.4.1. Memory map

## CPU

## Central Processing Unit (CPU)

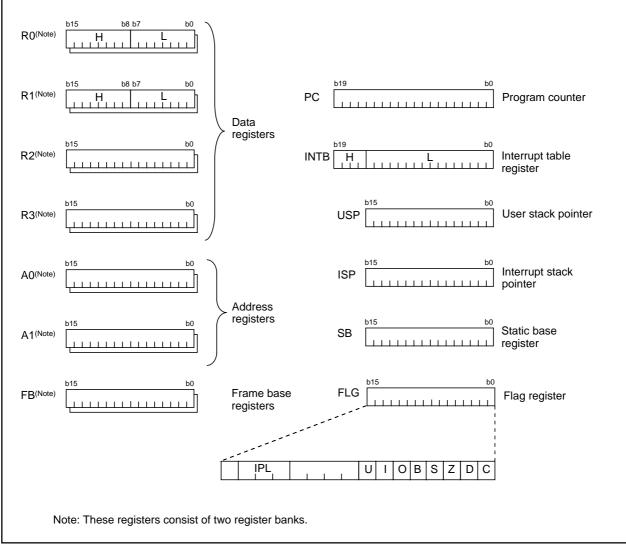

The CPU has a total of 13 registers shown in Figure 1.5.1. Seven of these registers (R0, R1, R2, R3, A0, A1, and FB) come in two sets; therefore, these have two register banks.

Figure 1.5.1. Central processing unit register

## (1) Data registers (R0, R0H, R0L, R1, R1H, R1L, R2, and R3)

Data registers (R0, R1, R2, and R3) are configured with 16 bits, and are used primarily for transfer and arithmetic/logic operations.

Registers R0 and R1 each can be used as separate 8-bit data registers, high-order bits as (R0H/R1H), and low-order bits as (R0L/R1L). In some instructions, registers R2 and R0, as well as R3 and R1 can use as 32-bit data registers (R2R0/R3R1).

## (2) Address registers (A0 and A1)

Address registers (A0 and A1) are configured with 16 bits, and have functions equivalent to those of data registers. These registers can also be used for address register indirect addressing and address register relative addressing.

In some instructions, registers A1 and A0 can be combined for use as a 32-bit address register (A1A0).

## (3) Frame base register (FB)

Frame base register (FB) is configured with 16 bits, and is used for FB relative addressing.

## (4) Program counter (PC)

Program counter (PC) is configured with 20 bits, indicating the address of an instruction to be executed.

## (5) Interrupt table register (INTB)

Interrupt table register (INTB) is configured with 20 bits, indicating the start address of an interrupt vector table.

## (6) Stack pointer (USP/ISP)

Stack pointer comes in two types: user stack pointer (USP) and interrupt stack pointer (ISP), each configured with 16 bits.

Your desired type of stack pointer (USP or ISP) can be selected by a stack pointer select flag (U flag). This flag is located at the position of bit 7 in the flag register (FLG).

## (7) Static base register (SB)

Static base register (SB) is configured with 16 bits, and is used for SB relative addressing.

## (8) Flag register (FLG)

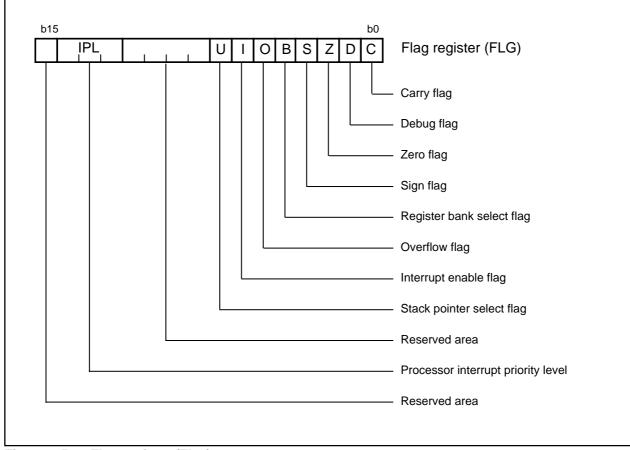

Flag register (FLG) is configured with 11 bits, each bit is used as a flag. Figure 1.5.2 shows the flag register (FLG). The following explains the function of each flag:

#### • Bit 0: Carry flag (C flag)

This flag retains a carry, borrow, or shift-out bit that has occurred in the arithmetic/logic unit.

#### • Bit 1: Debug flag (D flag)

This flag enables a single-step interrupt.

When this flag is "1", a single-step interrupt is generated after instruction execution. This flag is cleared to "0" when the interrupt is acknowledged.

• Bit 2: Zero flag (Z flag)

This flag is set to "1" when an arithmetic operation resulted in 0; otherwise, cleared to "0".

• Bit 3: Sign flag (S flag)

This flag is set to "1" when an arithmetic operation resulted in a negative value; otherwise, cleared to "0".

## • Bit 4: Register bank select flag (B flag)

This flag chooses a register bank. Register bank 0 is selected when this flag is "0"; register bank 1 is selected when this flag is "1".

• Bit 5: Overflow flag (O flag)

This flag is set to "1" when an arithmetic operation resulted in overflow; otherwise, cleared to "0".

• Bit 6: Interrupt enable flag (I flag)

This flag enables a maskable interrupt.

An interrupt is disabled when this flag is "0", and is enabled when this flag is "1". This flag is cleared to "0" when the interrupt is acknowledged.

#### • Bit 7: Stack pointer select flag (U flag)

Interrupt stack pointer (ISP) is selected when this flag is "0"; user stack pointer (USP) is selected when this flag is "1".

This flag is cleared to "0" when a hardware interrupt is acknowledged or an INT instruction of software interrupt Nos. 0 to 31 is executed.

#### • Bits 8 to 11: Reserved area

• Bits 12 to 14: Processor interrupt priority level (IPL)

Processor interrupt priority level (IPL) is configured with three bits, for specification of up to eight processor interrupt priority levels from level 0 to level 7.

If a requested interrupt has priority greater than the processor interrupt priority level (IPL), the interrupt is enabled.

#### • Bit 15: Reserved area

The C, Z, S, and O flags are changed when instructions are executed. See the software manual for details.

Figure 1.5.2. Flag register (FLG)

## Reset

There are two kinds of resets; hardware and software. In both cases, operation is the same after the reset. (See "Software Reset" for details of software resets.) This section explains on hardware resets.

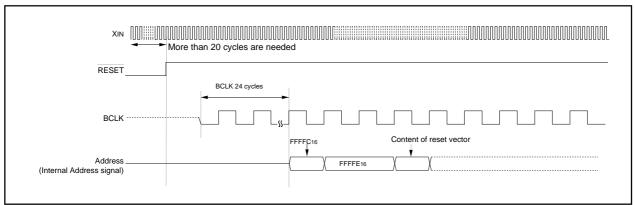

When the supply voltage is in the range where operation is guaranteed, a reset is effected by holding the reset pin level "L" (0.2Vcc max.) for at least 20 cycles. When the reset pin level is then returned to the "H" level while main clock is stable, the reset status is cancelled and program execution resumes from the address in the reset vector table.

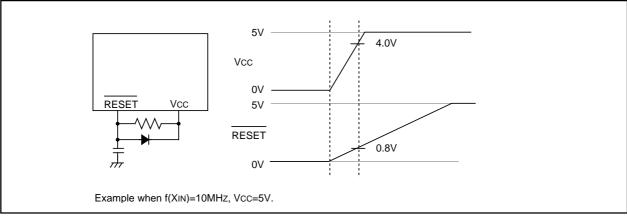

Figure 1.6.1 shows the example reset circuit. Figure 1.6.2 shows the reset sequence.

Figure 1.6.1. Example reset circuit

Figure 1.6.2. Reset sequence

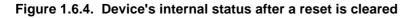

Table 1.6.1 shows the statuses of the other pins while the RESET pin level is "L". Figures 1.6.3 and 1.6.4 show the internal status of the microcomputer immediately after the reset is cancelled.

| Table 1.6.1. | Pin status when $\overline{\text{RESET}}$ pin level is "L" |  |

|--------------|------------------------------------------------------------|--|

|              |                                                            |  |

| Pin name                             | Status                              |

|--------------------------------------|-------------------------------------|

| P0, P10 to P12                       | Input port(with a pull up resistor) |

| P1 to P9, P13                        | Input port (floating)               |

| SEG0 to SEG15                        | "H" level is output                 |

| COM <sub>0</sub> to COM <sub>3</sub> | "H" level is output                 |

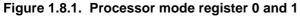

| (1)Processor mode register 0                                                                                                   | (000416)*** |                                          | (27)UART1 transmit interrupt control register  | (005316)••• | ? 0 0 0                                       |

|--------------------------------------------------------------------------------------------------------------------------------|-------------|------------------------------------------|------------------------------------------------|-------------|-----------------------------------------------|

| (2)Processor mode register 1                                                                                                   | (000516)*** |                                          | (28)UART1 receive interrupt control register   | (005416)••• |                                               |

| (3)System clock control register 0                                                                                             | (000616)*** | 0100100                                  | (29)Timer A0 interrupt control register        | (005516)••• | ? 0 0 0                                       |

| (4)System clock control register 1                                                                                             | (000716)*** | 0010000                                  | (30)Timer A1 interrupt control register        | (005616)*** |                                               |

| (5)Address match interrupt enable register                                                                                     | (000916)••• |                                          | (31)Timer A2 interrupt control register        | (005716)••• | ? 0 0 0                                       |

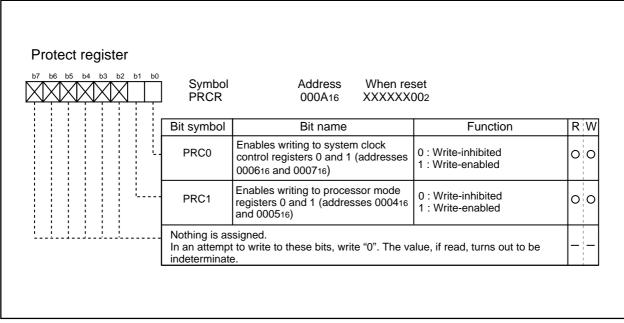

| (6)Protect register                                                                                                            | (000A16)••• |                                          | (32)Timer A3 / INT4 interrupt control register | (005816)••• |                                               |

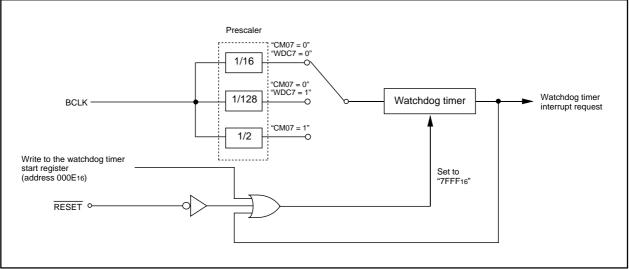

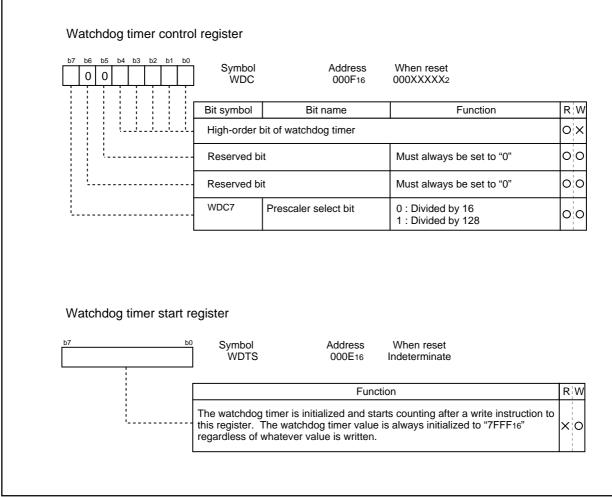

| (7)Watchdog timer control register                                                                                             | (000F16)••• | 000??????                                | (33)Timer A4 / INT5 interrupt control register | (005916)••• | 0 0 ? 0 0 0                                   |

| (8)Address match interrupt register 0                                                                                          | (001016)*** | 0016                                     | (34)Timer B0 interrupt control register        | (005A16)••• | ? 0 0 0                                       |

|                                                                                                                                | (001116)*** | 0016                                     | (35)Timer B1 interrupt control register        | (005B16)*** | ? 0 0 0                                       |

|                                                                                                                                | (001216)*** |                                          | (36)Timer B2 interrupt control register        | (005C16)*** | ? 0 0 0                                       |

| (9)Address match interrupt register 1                                                                                          | (001416)••• | 0016                                     | (37) INT0 interrupt control register           | (005D16)*** | 0 0 ? 0 0 0                                   |

|                                                                                                                                | (001516)*** | 0016                                     | (38) INT1 interrupt control register           | (005E16)*** |                                               |

|                                                                                                                                | (001616)*** |                                          | (39) INT2 interrupt control register           | (005F16)••• |                                               |

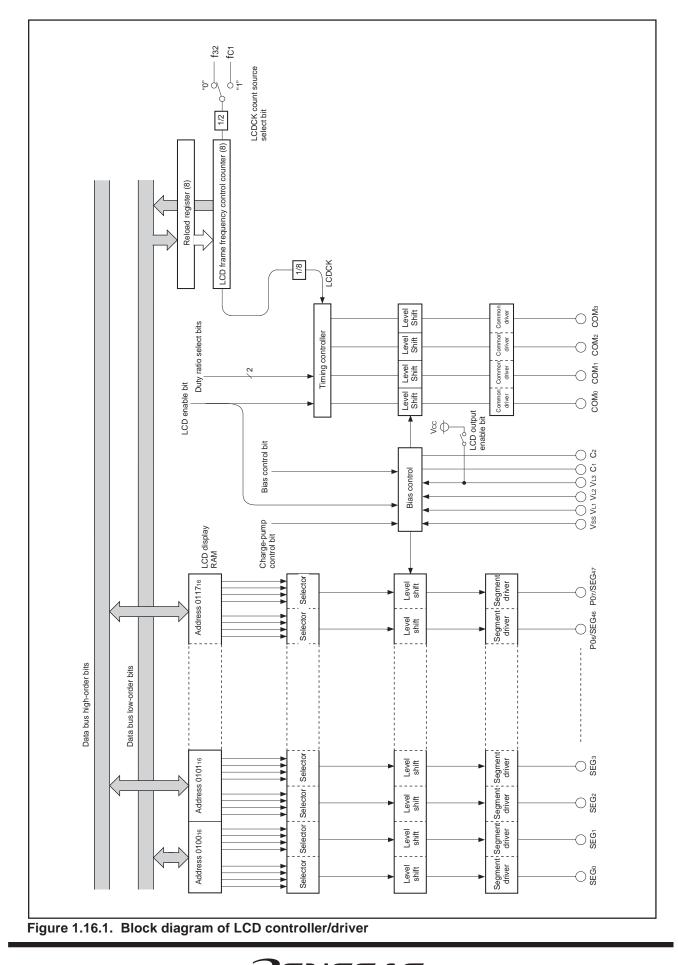

| (10)DMA0 control register                                                                                                      | (002C16)*** | 00000000000                              | (40)LCD mode register                          | (012016)*** | 0 0 0 0 0 0 0 0                               |

| (11)DMA1 control register                                                                                                      | (003C16)*** | 00000000000                              | (41)Segment output enable register             | (012216)*** | 00000000                                      |

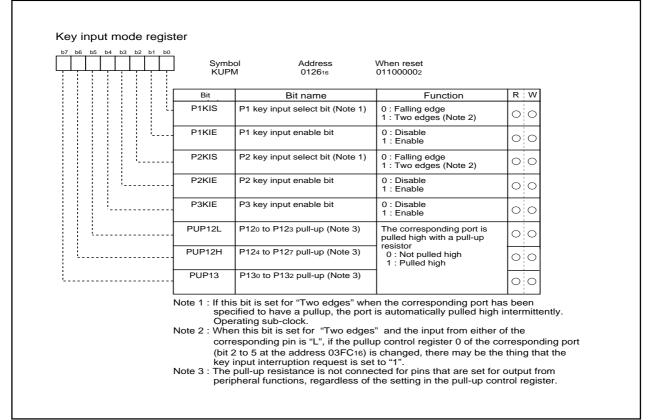

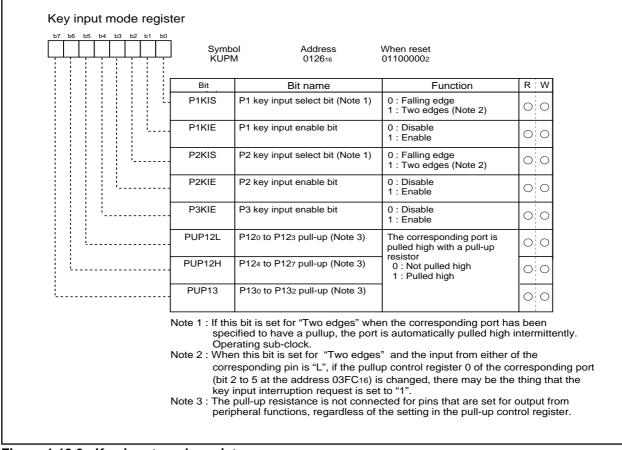

| (12) INT3 interrupt control register                                                                                           | (004416)*** |                                          | (42)Key input mode register                    | (012616)*** | 0 1 1 0 0 0 0 0                               |

| (13)Timer B5 interrupt control register                                                                                        | (004516)*** | ? 0 0 0                                  | (43)Count start flag 1                         | (034016)••• | 0000000                                       |

| (14)Timer B4 interrupt control register                                                                                        | (004616)*** | ?000                                     | (44)One-shot start flag 1                      | (034216)••• | 000000                                        |

| (15)Timer B3 interrupt control register                                                                                        | (004716)*** | ? 0 0 0                                  | (45)Trigger select flag 1                      | (034316)••• |                                               |

| (16)Timer A7 interrupt control register                                                                                        | (004816)*** | ? 0 0 0                                  | (46)Up-down flag 1                             | (034416)*** |                                               |

| (17)Timer A6 interrupt control register                                                                                        | (004916)*** | ? 0 0 0                                  | (47)Timer A5 mode register                     | (035616)*** | 0016                                          |

| (18)Timer A5 interrupt control register                                                                                        | (004A16)••• | ? 0 0 0                                  | (48)Timer A6 mode register                     | (035716)*** | 0016                                          |

| (19)DMA0 interrupt control register                                                                                            | (004B16)*** | ? 0 0 0                                  | (49)Timer A7 mode register                     | (035816)*** | 0016                                          |

| (20)DMA1 interrupt control register                                                                                            | (004C16)*** | ? 0 0 0                                  | (50)Timer B3 mode register                     | (035B16)*** | 00?0000                                       |

| (21)Key input interrupt control register                                                                                       | (004D16)*** | 2000                                     | (51)Timer B4 mode register                     | (035C16)*** | 0 0 ? 🗙 0 0 0                                 |

| (22)A-D conversion interrupt control register                                                                                  | (004E16)*** | ? 0 0 0                                  | (52)Timer B5 mode register                     | (035D16)*** | 00?0000                                       |

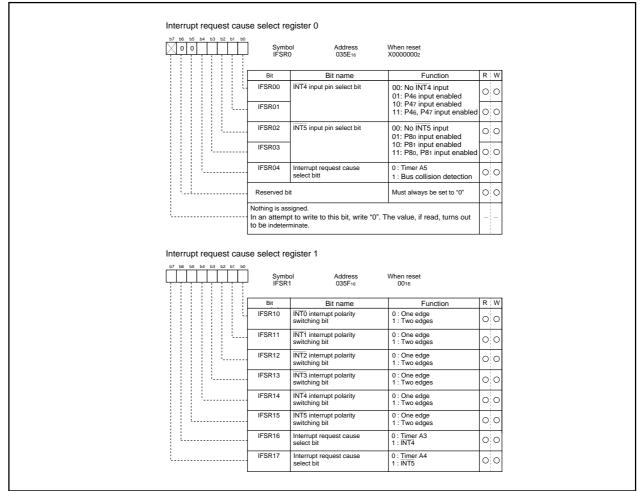

| (23)UART2 transmit interrupt control register                                                                                  | (004F16)*** | 2000                                     | (53)Interrupt cause select register 0          | (035E16)*** | $X \circ \circ \circ \circ \circ \circ \circ$ |

| (24)UART2 receive interrupt control register                                                                                   | (005016)*** | ? 0 0 0                                  | (54)Interrupt cause select register 1          | (035F16)••• | 0016                                          |

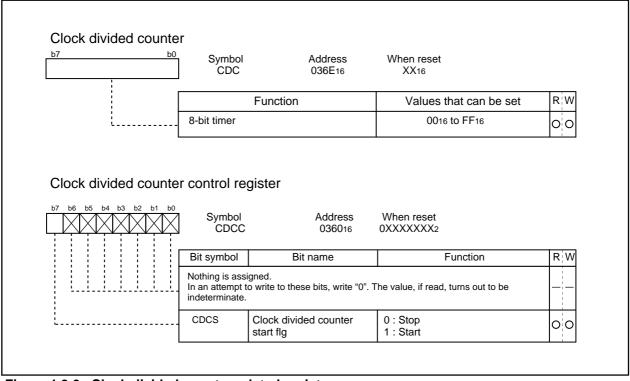

| (25)UART0 transmit interrupt control register                                                                                  | (005116)*** | ? 0 0 0                                  | (55)Clock division counter control register    | (036016)*** | $\circ X X X X X X X X X X X X X X X X X X X$ |

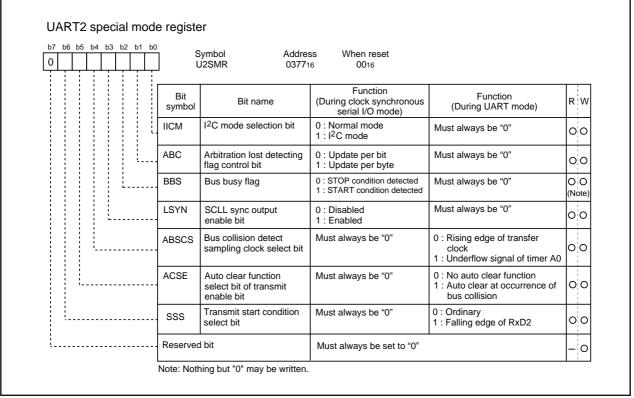

| (26)UART0 receive interrupt control register                                                                                   | (005216)*** | ? 0 0 0                                  | (56)UART2 special mode register 2              | (037616)*** | 0016                                          |

|                                                                                                                                |             |                                          | (57)UART2 special mode register                | (037716)*** | 0016                                          |

|                                                                                                                                |             |                                          | (58)UART2 transmit/receive mode register       | (037816)*** | 0016                                          |

| The content of other registers and RAM is undefined when the microcomputer is reset. The initial values must therefore be set. |             |                                          |                                                |             |                                               |

|                                                                                                                                |             | othing is mapped to this bit<br>ndefined |                                                |             |                                               |

Figure 1.6.3. Device's internal status after a reset is cleared

| (59)UART2 transmit/receive control register 0                                                                                  | (037C16)··· 0 0 0 0 1 0 0 0    | (85)A-D control register 0           | (03D616)··· X 0 0 0 ? ? ?   |  |

|--------------------------------------------------------------------------------------------------------------------------------|--------------------------------|--------------------------------------|-----------------------------|--|

| (60)UART2 transmit/receive control register 1                                                                                  | (037D16)··· 0 0 0 0 0 1 0      | (86)A-D control register 1           | (03D716)···· 0016           |  |

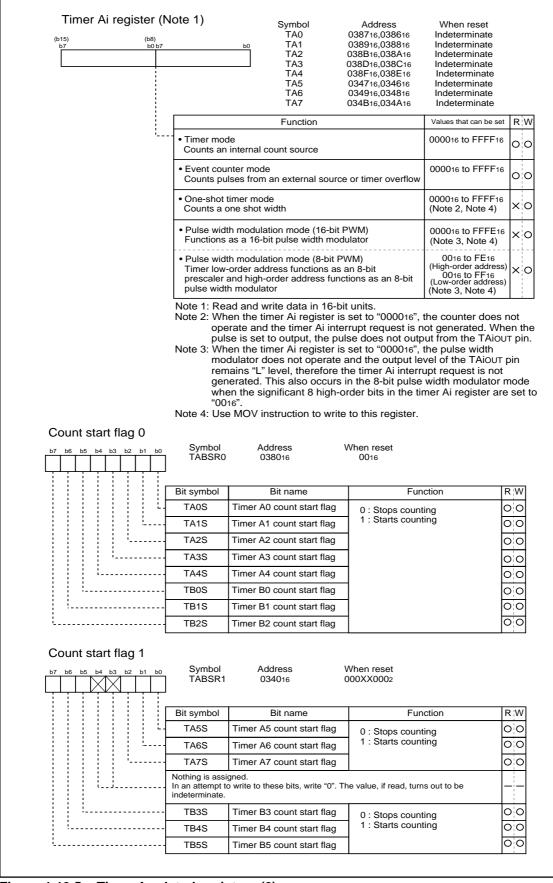

| (61)Count start flag 0                                                                                                         | (038016) 0016                  | (87)D-A control register             | (03DC16)···                 |  |

| (62) Clock prescaler reset flag                                                                                                | (038116)                       | (88)Port P0 direction register       | (03E216)···· 0016           |  |

| (63)One-shot start flag 0                                                                                                      | (038216) 0 0 0 0 0 0           | (89)Port P1 direction register       | (03E316)· · · 0016          |  |

| (64)Trigger select flag 0                                                                                                      | (038316) 0016                  | (90)Port P2 direction register       | (03E616)· · · 0016          |  |

| (65)Up-down flag 0                                                                                                             | (038416) 0016                  | (91)Port P3 direction register       | (03E716)···                 |  |

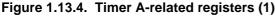

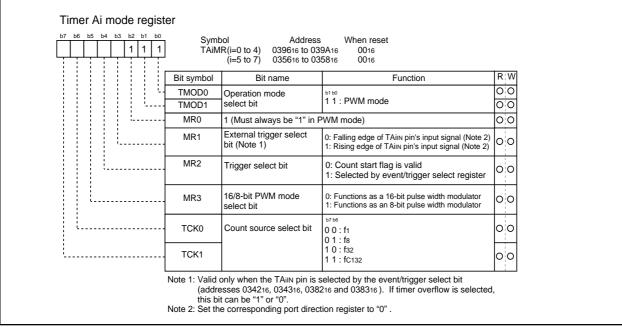

| (66)Timer A0 mode register                                                                                                     | (039616) 0016                  | (92)Port P4 direction register       | (03EA16)···                 |  |

| (67)Timer A1 mode register                                                                                                     | (039716) 0016                  | (93)Port P5 direction register       | (03EB16)···                 |  |

| (68)Timer A2 mode register                                                                                                     | (039816) 0016                  | (94)Port P6 direction register       | (03EE16)· · · 0016          |  |

| (69)Timer A3 mode register                                                                                                     | (039916) 0016                  | (95)Port P7 direction register       | (03EF16)····                |  |

| (70)Timer A4 mode register                                                                                                     | (039A16)· · · 0016             | (96)Port P8 direction register       | (03F216)· · · 0016          |  |

| (71)Timer B0 mode register                                                                                                     | (039B16)··· 0 0 ? 0 0 0 0      | (97)Port P9 direction register       | (03F316)· · · 0016          |  |

| (72)Timer B1 mode register                                                                                                     | (039C16)··· 0 0 ? 0 0 0 0      | (98)Port P10 direction register      | (03F616)· · · 0016          |  |

| (73)Timer B2 mode register                                                                                                     | (039D16)··· 0 0 ? 0 0 0 0      | (99)Port P11 direction register      | (03F716)· · · 0016          |  |

| (74)UART0 transmit/receive mode register                                                                                       | (03A016)· · · 0016             | (100)Port P12 direction register     | (03FA16)···                 |  |

| (75)UART0 transmit/receive control register 0                                                                                  | (03A416)··· 0 0 0 0 1 0 0 0    | (101)Port P13 direction register     | (03FB16)···                 |  |

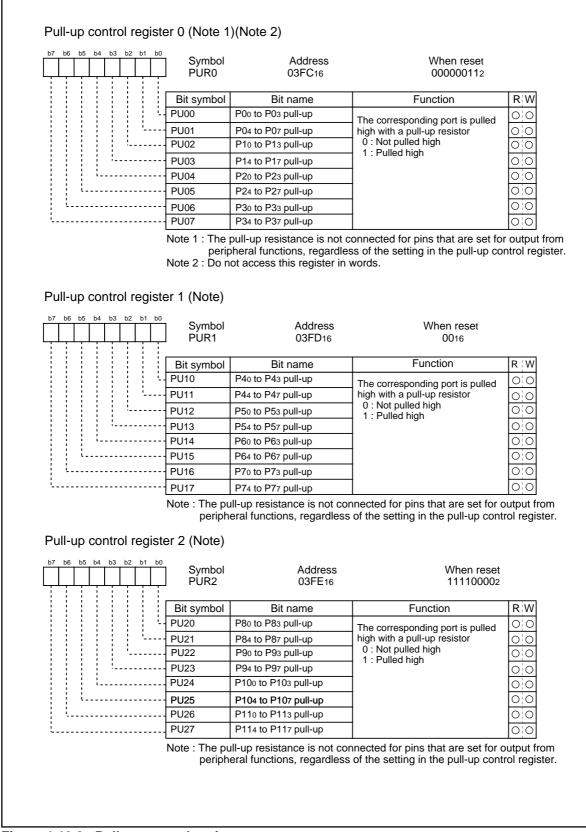

| (76)UART0 transmit/receive control register 1                                                                                  | (03A516)··· 0 0 0 0 0 0 1 0    | (102)Pull-up control register 0      | (03FC16)··· 0 0 0 0 0 1 1   |  |

| (77)UART1 transmit/receive mode register                                                                                       | (03A816)· · · 0016             | (103)Pull-up control register 1      | (03FD16)· · · 0016          |  |

| (78)UART1 transmit/receive control register 0                                                                                  | (03AC16)···00001000            | (104)Pull-up control register 2      | (03FE16)··· 1 1 1 1 0 0 0 0 |  |

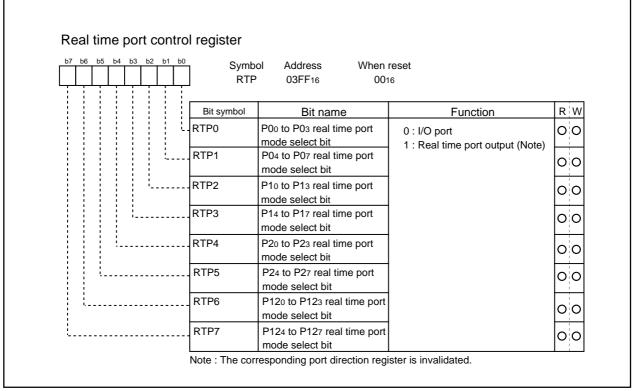

| (79)UART1 transmit/receive control register 1                                                                                  | (03AD16)···00000010            | (105)Real time port control register | (03FF16)· · · 0016          |  |

| (80)UART transmit/receive control register 2                                                                                   | (03B016)··· 0 0 0 0 0 0 0 0    | (106)Data registers (R0/R1/R2/R3)    | 000016                      |  |

| (81)Flash memory control register (Note)                                                                                       | 0 (03B416)···                  | (107)Address registers (A0/A1)       | 000016                      |  |

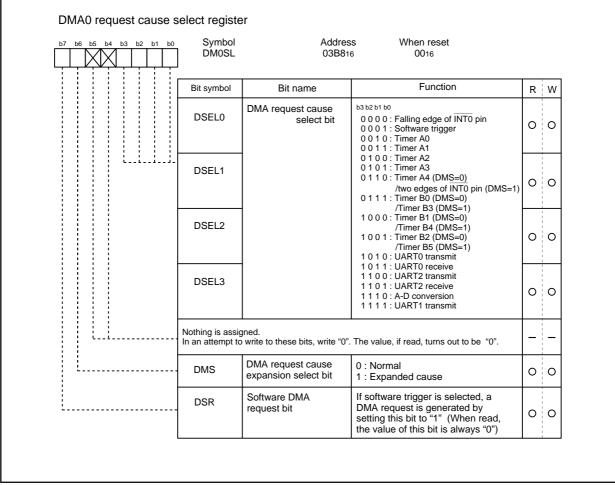

| (82)DMA0 cause select register                                                                                                 | (03B816)· · · 0016             | (108)Frame base register (FB)        | 000016                      |  |

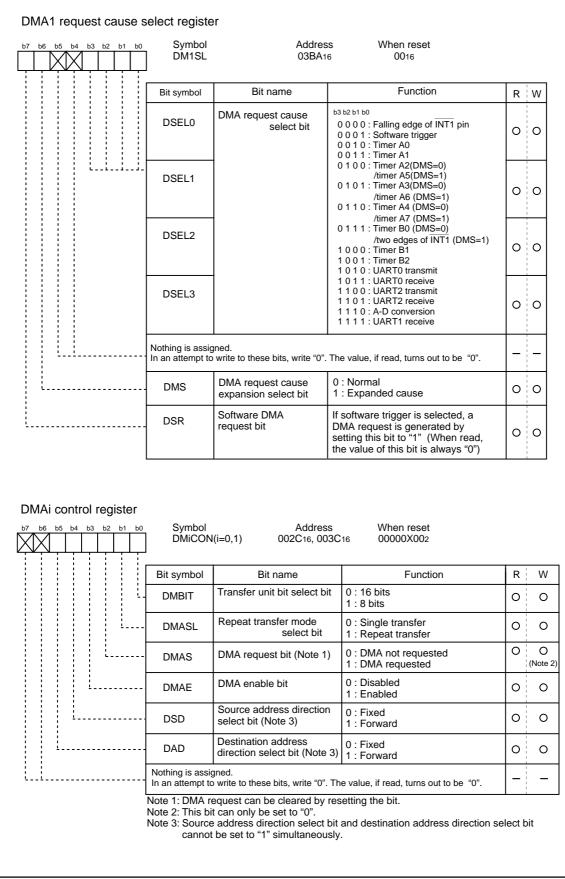

| (83)DMA1 cause select register                                                                                                 | (03BA16)···                    | (109)Interrupt table register (INTB) | 0000016                     |  |

| (84) A-D control register 2                                                                                                    | (03D416)···                    | (110)User stack pointer (USP)        | 000016                      |  |

|                                                                                                                                |                                | (111)Interrupt stack pointer (ISP)   | 000016                      |  |

|                                                                                                                                |                                | (112)Static base register (SB)       | 000016                      |  |

|                                                                                                                                |                                | (113)Flag register (FLG)             | 000016                      |  |

| x : Nothing is mapped to this bit<br>? : Undefined                                                                             |                                |                                      |                             |  |

| The content of other registers and RAM is undefined when the microcomputer is reset. The initial values must therefore be set. |                                |                                      |                             |  |

| Note : This register is only e                                                                                                 | exist in flash memory version. |                                      |                             |  |

| 000016           |                                                |

|------------------|------------------------------------------------|

| 000116           |                                                |

| 000216           |                                                |

| 000316           |                                                |

| 000416           | Processor mode register 0 (PM0)                |

| 000516           | Processor mode register 1(PM1)                 |

| 000616           | System clock control register 0 (CM0)          |

| 000716<br>000816 | System clock control register 1 (CM1)          |

| 000916           |                                                |

| 000A16           | Address match interrupt enable register (AIER) |

| 000B16           | Protect register (PRCR)                        |

| 000C16           |                                                |

| 000D16           |                                                |

| 000E16           | Watchdog timer start register (WDTS)           |

| 000F16           | Watchdog timer control register (WDC)          |

| 001016           |                                                |

| 001116           | Address match interrupt register 0 (RMAD0)     |

| 001216           |                                                |

| 001316           |                                                |

| 001416           | Address motch interrupt register 1 (DMAD4)     |

| 001516           | Address match interrupt register 1 (RMAD1)     |

| 001716           |                                                |

| 001816           |                                                |

| 001916           |                                                |

| 001A16           |                                                |

| 001B16           |                                                |

| 001C16           |                                                |

| 001D16           |                                                |

| 001E16           |                                                |

| 001F16           |                                                |

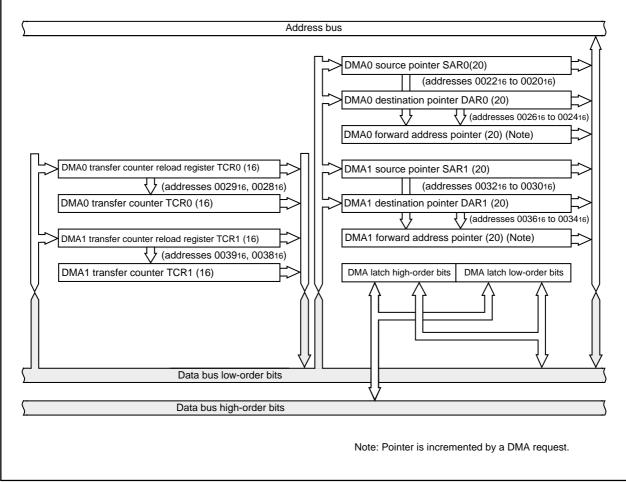

| 002016<br>002116 | DMA0 source pointer (SAR0)                     |

| 002116           |                                                |

| 002316           |                                                |

| 002416           |                                                |

| 002516           | DMA0 destination pointer (DAR0)                |

| 002616           |                                                |

| 002716           |                                                |

| 002816           | DMA0 transfer counter (TCR0)                   |

| 002916           |                                                |

| 002A16<br>002B16 |                                                |

| 002D18           | DMA0 control register (DM0CON)                 |

| 002D16           |                                                |

| 002E16           |                                                |

| 002F16           |                                                |

| 003016           |                                                |

| 003116           | DMA1 source pointer (SAR1)                     |

| 003216           |                                                |

| 003316           |                                                |

| 003416           | DMA1 doctination pointer (DAR1)                |

| 003516<br>003616 | DMA1 destination pointer (DAR1)                |

| 003016           |                                                |

| 003816           |                                                |

| 003916           | DMA1 transfer counter (TCR1)                   |

| 003A16           |                                                |

| 003B16           |                                                |

| 003C16           | DMA1 control register (DM1CON)                 |

| 003D16           |                                                |

| 003E16           |                                                |

| 003F16           |                                                |

|                  |                                                |

|                  |                                                |

| 4016         |                                                                                                       |

|--------------|-------------------------------------------------------------------------------------------------------|

| 4116         |                                                                                                       |

| 4216         |                                                                                                       |

| 4316         |                                                                                                       |

| 4416         | INT3 interrupt control register (INT3IC)                                                              |

| 4516         | Timer B5 interrupt control register (TB5IC)                                                           |

| 4616         | Timer B4 interrupt control register (TB4IC)                                                           |

| 4716         | Timer B3 interrupt control register (TB3IC)                                                           |

| 4816         | Timer A7 interrupt control register (TA7IC)                                                           |

| 4916         | Timer A6 interrupt control register (TA6IC)                                                           |

| 4A16         | Timer A5 interrupt control register (TA5IC)                                                           |

| 4B16         | Bus collision detection interrupt control register (BCNIC)<br>DMA0 interrupt control register (DM0IC) |

| +D16<br>4C16 |                                                                                                       |

| D16          | DMA1 interrupt control register (DM1IC)                                                               |

| E16          | Key input interrupt control register (KUPIC)<br>A-D conversion interrupt control register (ADIC)      |

| F16          | UART2 transmit interrupt control register (S2TIC)                                                     |

| 016          | UART2 receive interrupt control register (S2RIC)                                                      |

| 116          | UART0 transmit interrupt control register (S0TIC)                                                     |

| 5216         | UART0 receive interrupt control register (S0RIC)                                                      |

| 5316         | UART1 transmit interrupt control register (S1TIC)                                                     |

| 5416         | UART1 receive interrupt control register (S1RIC)                                                      |

| 5516         | Timer A0 interrupt control register (TA0IC)                                                           |

| 616          | Timer A1 interrupt control register (TA1IC)                                                           |

| 5716         | Timer A2 interrupt control register (TA2IC)                                                           |

| 816          | Timer A3 interrupt control register (TA3IC)                                                           |

|              | INT4 interrupt control register (INT4IC)                                                              |

| 5916         | Timer A4 interrupt control register (TA4IC)                                                           |

|              | INT5 interrupt control register (INT5IC)                                                              |

| A16          | Timer B0 interrupt control register (TB0IC)                                                           |

| B16          | Timer B1 interrupt control register (TB1IC)                                                           |

| C16          | Timer B2 interrupt control register (TB2IC)<br>INT0 interrupt control register (INT0IC)               |

| 5E16         | INT1 interrupt control register (INT1IC)                                                              |

| F16          | INT2 interrupt control register (INT11C)                                                              |

| Ĵ            |                                                                                                       |

| 016          |                                                                                                       |

| 1116         | LCD RAM0(LRAM0)<br>LCD RAM1(LRAM1)                                                                    |

| 216          | LCD RAMIT(LRAMIT)<br>LCD RAM2(LRAM2)                                                                  |

| 316          | LCD RAM2(LRAM2)<br>LCD RAM3(LRAM3)                                                                    |

| 416          | LCD RAMS(LRAMS)<br>LCD RAM4(LRAM4)                                                                    |

| 516          | LCD RAM5(LRAM5)                                                                                       |

| 616          | LCD RAM6(LRAM6)                                                                                       |

| 716          | LCD RAM7(LRAM7)                                                                                       |

| 816          | LCD RAM8(LRAM8)                                                                                       |

| 916          | LCD RAM9(LRAM9)                                                                                       |

| A16          | LCD RAM10(LRAM10)                                                                                     |

| B16          | LCD RAM11(LRAM11)                                                                                     |

| C16          | LCD RAM12(LRAM12)                                                                                     |

| D16          | LCD RAM13(LRAM13)                                                                                     |

| E16          | LCD RAM14(LRAM14)                                                                                     |

| F16          | LCD RAM15(LRAM15)                                                                                     |

| D16          | LCD RAM16(LRAM16)                                                                                     |

| 116<br>246   | LCD RAM17(LRAM17)                                                                                     |

| 216          | LCD RAM18(LRAM18)                                                                                     |

| 316<br>416   | LCD RAM19(LRAM19)                                                                                     |

| 416<br>516   | LCD RAM20(LRAM20)                                                                                     |

| 516<br>516   | LCD RAM21(LRAM21)<br>LCD RAM22(LRAM22)                                                                |

| 716          | LCD RAM23(LRAM23)                                                                                     |

| <u>°</u>     |                                                                                                       |

| )16          | LCD mode register (LCDM)                                                                              |

| 16<br>16     |                                                                                                       |

| 216          | Segment output enable register (SEG)                                                                  |

|              |                                                                                                       |

|              |                                                                                                       |

| 816          | LCD frame frequency counter (LCDTIM)                                                                  |

|              | LCD frame frequency counter (LCDTIM)                                                                  |

Note : Locations in the SFR area where nothing is allocated are reserved areas. Do not access these areas for read or write.

Figure 1.7.1. Location of peripheral unit control registers (1)

| 034016                               | Count start flag 1 (TABSR1)                                                              |

|--------------------------------------|------------------------------------------------------------------------------------------|

| 034116                               |                                                                                          |

| 034216                               | One-shot start flag 1 (ONSF1)                                                            |

| 034316                               | Trigger select register 1 (TRGSR1)                                                       |

| 034416                               | Up-down flag 1(UDF1)                                                                     |

| 34516                                |                                                                                          |

| )34616<br>)34716                     | Timer A5 register (TA5)                                                                  |

| )34816                               |                                                                                          |

| )34916                               | Timer A6 register (TA6)                                                                  |

| 34A16                                |                                                                                          |

| 34B16                                | Timer A7 register (TA7)                                                                  |

| 34C16                                |                                                                                          |

| 34D16                                |                                                                                          |

| 34E16                                |                                                                                          |

| 34F16                                |                                                                                          |

| 35016                                | Timer B3 register (TB3)                                                                  |

| 35116                                | ·                                                                                        |

| 35216                                | Timer B4 register (TB4)                                                                  |

| 35316                                |                                                                                          |

| 35416                                | Timer B5 register (TB5)                                                                  |

| 35516                                | ,                                                                                        |

| 35616                                | Timer A5 mode register (TA5MR)                                                           |

| 35716                                | Timer A6 mode register (TA6MR)                                                           |

| 35816<br>35916                       | Timer A7 mode register (TA7MR)                                                           |

| 35A16                                |                                                                                          |

| 35B16                                | Timer B3 mode register (TB3MR)                                                           |

| 35C16                                | Timer B4 mode register (TB3MR)                                                           |

| 35D16                                | Timer B5 mode register (TB5MR)                                                           |

| 35E16                                | Interrupt cause select register 0 (IFSR0)                                                |

| 35F16                                | Interrupt cause select register 1 (IFSR1)                                                |

| 36016                                | Clock division counter control register (CDCC)                                           |

| 36116                                |                                                                                          |

| 36216                                |                                                                                          |

| 36316                                |                                                                                          |

| 36416                                |                                                                                          |

| 36516                                |                                                                                          |

| 36616                                |                                                                                          |

| 36716                                |                                                                                          |

| 36816                                |                                                                                          |

| 36916                                |                                                                                          |

| 36A16                                |                                                                                          |

| 36B16                                |                                                                                          |

| 36C16                                |                                                                                          |

| 36D16<br>36E16                       | Clock division counter (CDC)                                                             |

| 36E16<br>36F16                       | Clock division counter (CDC)                                                             |

| 37016                                |                                                                                          |

| 37116                                |                                                                                          |

| 37216                                |                                                                                          |

| 37316                                |                                                                                          |

| 37416                                |                                                                                          |

| 37516                                |                                                                                          |

| 37616                                | UART2 special mode register 2(U2SMR2)                                                    |

| 37716                                | UART2 special mode register (U2SMR)                                                      |

| 37816                                | UART2 transmit/receive mode register (U2MR)                                              |

| 37916                                | UART2 bit rate generator (U2BRG)                                                         |

| 37A16                                | UART2 transmit buffer register (U2TB)                                                    |

| 37B16                                |                                                                                          |

|                                      | UART2 transmit/receive control register 0 (U2C0)                                         |

| 1                                    |                                                                                          |

| 1                                    | UART2 transmit/receive control register 1 (U2C1)                                         |

| )37C16<br>)37D16<br>)37E16<br>)37F16 | UART2 transmit/receive control register 1 (U2C1)<br>UART2 receive buffer register (U2RB) |

| 038016           | Count start flag 0 (TABSR0)                        |

|------------------|----------------------------------------------------|

| 038116           | Clock prescaler reset flag (CPSRF)                 |

| 038216           | One-shot start flag 0 (ONSF0)                      |

| 038316           | Trigger select register 0 (TRGSR0)                 |

| 038416           | Up-down flag 0 (UDF0)                              |

| 038516           |                                                    |

| 038616           | Timer A0 register (TA0)                            |

| 038716           | Timer A0 register (TA0)                            |

| 038816           | Timer A1 register (TA1)                            |

| 038916           |                                                    |

| 038A16           | Timer AD register (TAD)                            |

| 038B16           | Timer A2 register (TA2)                            |

| 038C16           | Timer A2 register (TA2)                            |

| 038D16           | Timer A3 register (TA3)                            |

| 038E16           | Timer $\Lambda 4$ register $(T\Lambda 4)$          |

| 038F16           | Timer A4 register (TA4)                            |

| 039016           |                                                    |

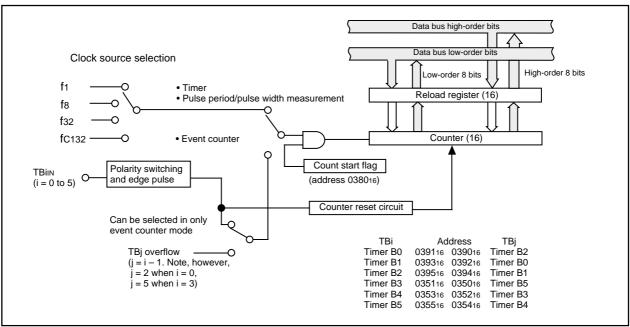

| 039116           | Timer B0 register (TB0)                            |

| 039216           | Timer P1 register (TP1)                            |

| 039316           | Timer B1 register (TB1)                            |

| 039416           | Timer D0 as sister (TD0)                           |

| 039516           | Timer B2 register (TB2)                            |

| 039616           | Timer A0 mode register (TA0MR)                     |

| 039716           | Timer A1 mode register (TA1MR)                     |

| 039816           | Timer A2 mode register (TA2MR)                     |

| 039916           | Timer A3 mode register (TA3MR)                     |

| 039A16           | Timer A4 mode register (TA4MR)                     |

| 039B16           | Timer B0 mode register (TB0MR)                     |

| 039C16           | Timer B1 mode register (TB1MR)                     |

| 039D16           | Timer B2 mode register (TB2MR)                     |

| 039E16           |                                                    |

| 039E16           |                                                    |

|                  | UART0 transmit/receive mode register (U0MR)        |

| 03A016           |                                                    |

| 03A116           | UART0 bit rate generator (U0BRG)                   |

| 03A216           | UART0 transmit buffer register (U0TB)              |

| 03A316           | LIADTO transmit/reasing control register 0 (LIOCO) |

| 03A416           | UART0 transmit/receive control register 0 (U0C0)   |

| 03A516           | UART0 transmit/receive control register 1 (U0C1)   |

| 03A616           | UART0 receive buffer register (U0RB)               |

| 03A716           | UART1 transmit/receive mode register (U1MR)        |

| 03A816           |                                                    |

| 03A916           | UART1 bit rate generator (U1BRG)                   |

| 03AA16           | UART1 transmit buffer register (U1TB)              |

| 03AB16           | LIAPT1 transmit/receive control register 0 /LI1C0) |

| 03AC16           | UART1 transmit/receive control register 0 (U1C0)   |

| 03AD16           | UART1 transmit/receive control register 1 (U1C1)   |

| 03AE16           | UART1 receive buffer register (U1RB)               |

| 03AF16           |                                                    |

| 03B016           | UART transmit/receive control register 2 (UCON)    |

| 03B116           |                                                    |

| 03B216           |                                                    |

| 03B316           | Fleeh memory control register (FMOD) (Note 4)      |

| 03B416           | Flash memory control register (FMCR)(Note 1)       |

| 03B516           |                                                    |

| 03B616           |                                                    |

| 03B716           |                                                    |

| 03B816           | DMA0 request cause select register (DM0SL)         |

| 03B916           |                                                    |

| 03BA16           | DMA1 request cause select register (DM1SL)         |

| 03BB16           |                                                    |

| 03BC16           |                                                    |

|                  |                                                    |

| 03BD16           |                                                    |

| 03BD16<br>03BE16 |                                                    |

|                  |                                                    |

Note 1: This register is only exist in flash memory version. Note 2: Locations in the SFR area where nothing is allocated are reserved areas. Do not access these areas for read or write.

Figure 1.7.2. Location of peripheral unit control registers (2)

| 03C016           | A-D register 0 (AD0)                                                 |

|------------------|----------------------------------------------------------------------|

| 03C116           |                                                                      |

| 03C216           | A-D register 1 (AD1)                                                 |

| 03C316           | <b>5</b> ( )                                                         |

| 03C416           | A-D register 2 (AD2)                                                 |

| 03C516           |                                                                      |

| 03C616<br>03C716 | A-D register 3 (AD3)                                                 |

| 03C816           |                                                                      |

| 03C916           | A-D register 4 (AD4)                                                 |

| 03CA16           | A-D register 5 (AD5)                                                 |

| 03CB16           | A-D Tegister 5 (ADS)                                                 |

| 03CC16           | A-D register 6 (AD6)                                                 |

| 03CD16           |                                                                      |

| 03CE16           | A-D register 7 (AD7)                                                 |

| 03CF16<br>03D016 |                                                                      |

| 03D018           |                                                                      |

| 03D216           |                                                                      |

| 03D316           |                                                                      |

| 03D416           | A-D control register 2 (ADCON2)                                      |

| 03D516           |                                                                      |

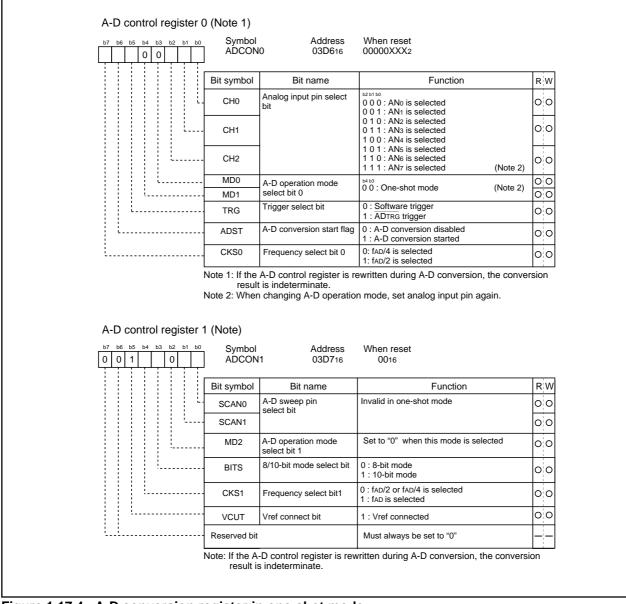

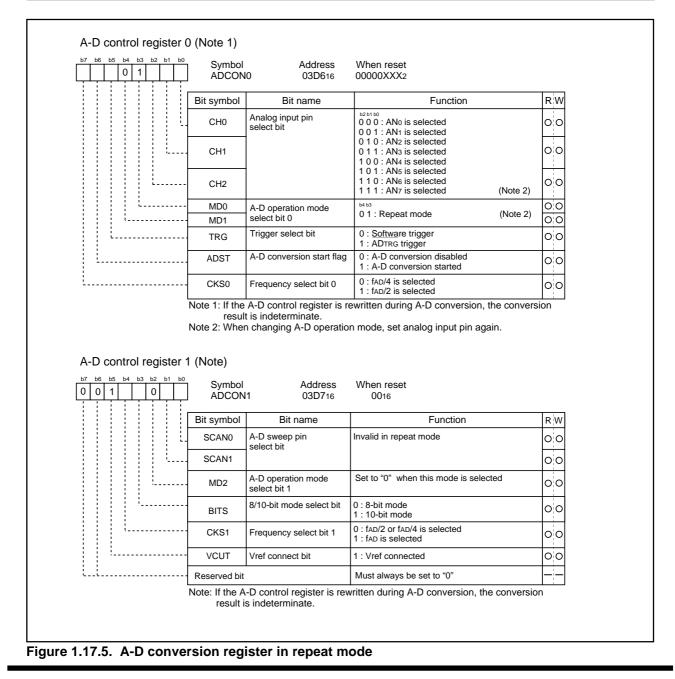

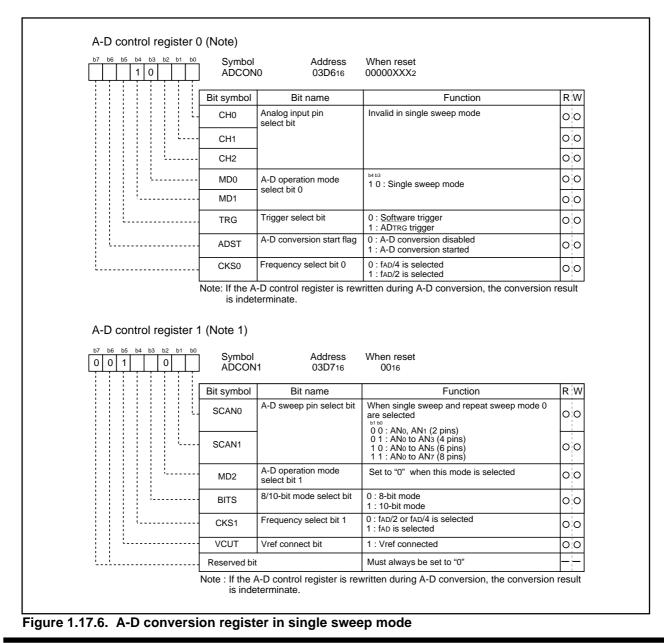

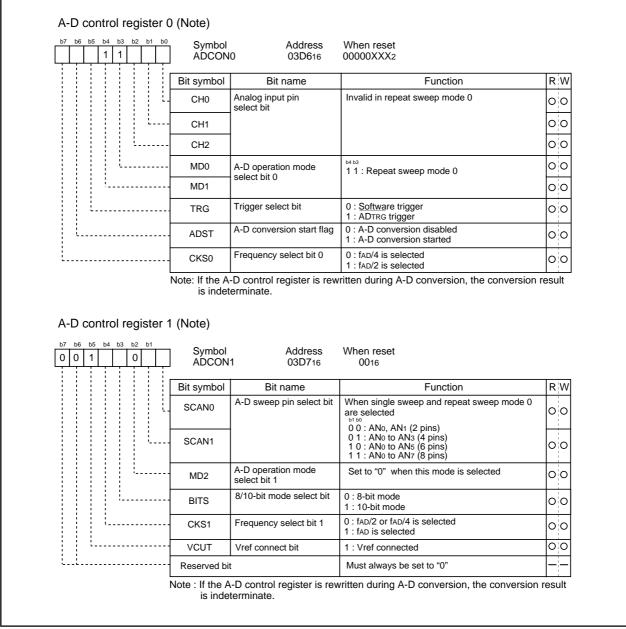

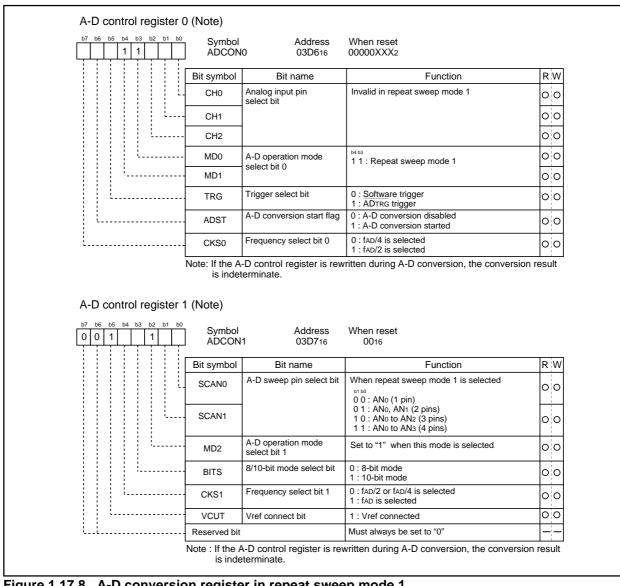

| 03D616           | A-D control register 0 (ADCON0)                                      |

| 03D716           | A-D control register 1 (ADCON1)                                      |

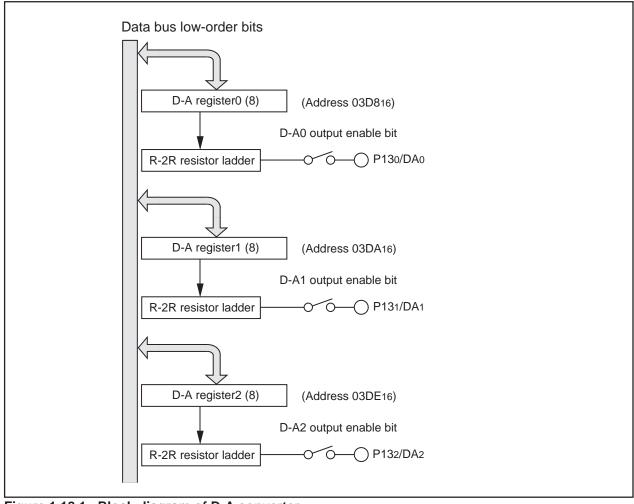

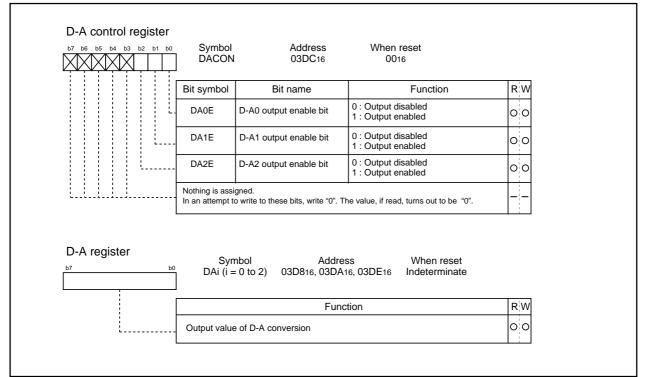

| 03D816           | D-A register 0 (DA0)                                                 |

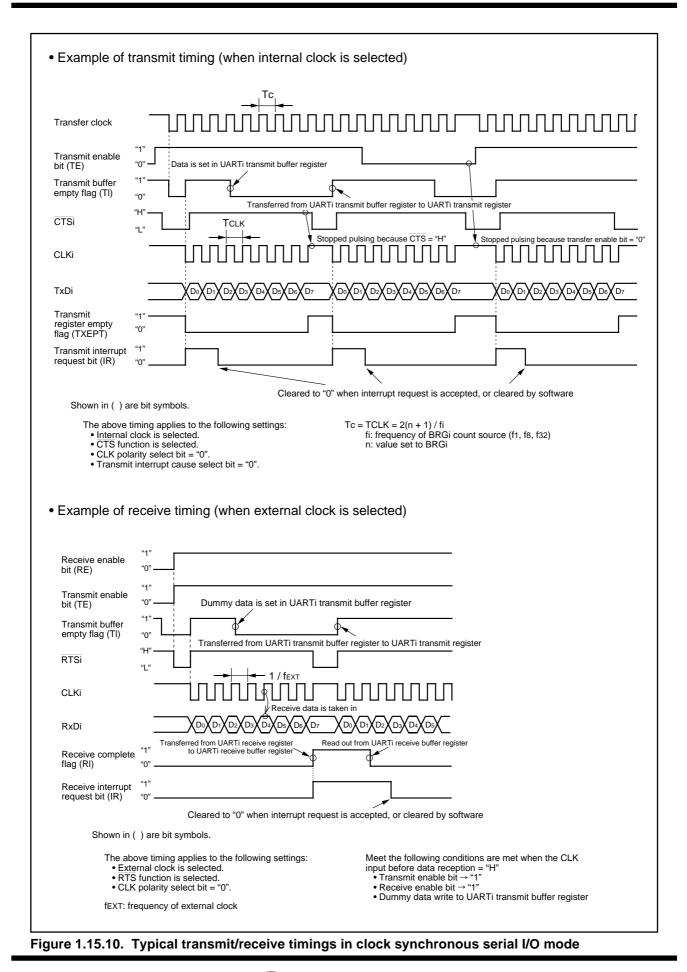

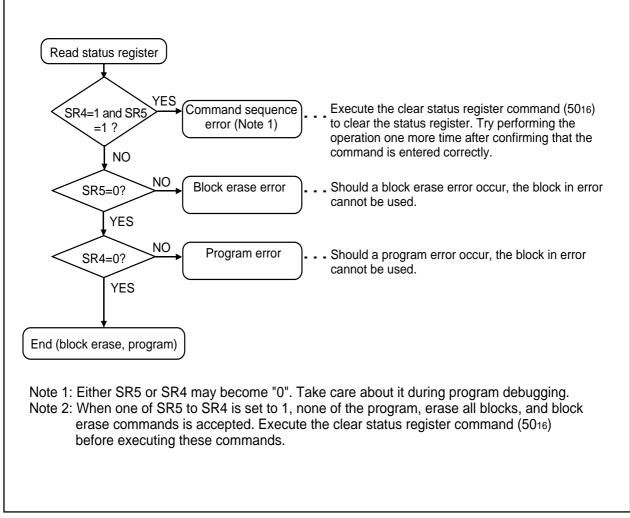

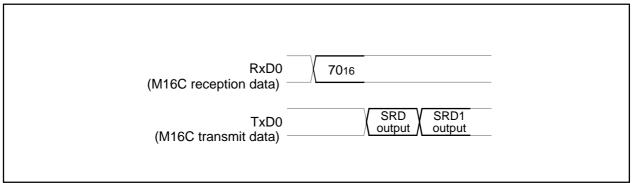

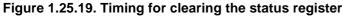

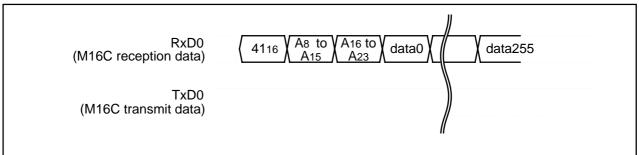

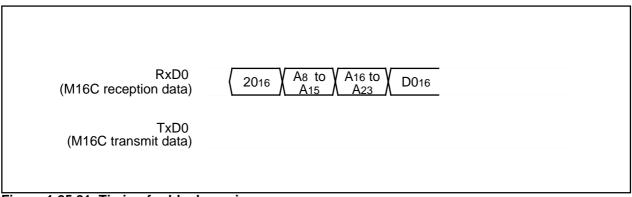

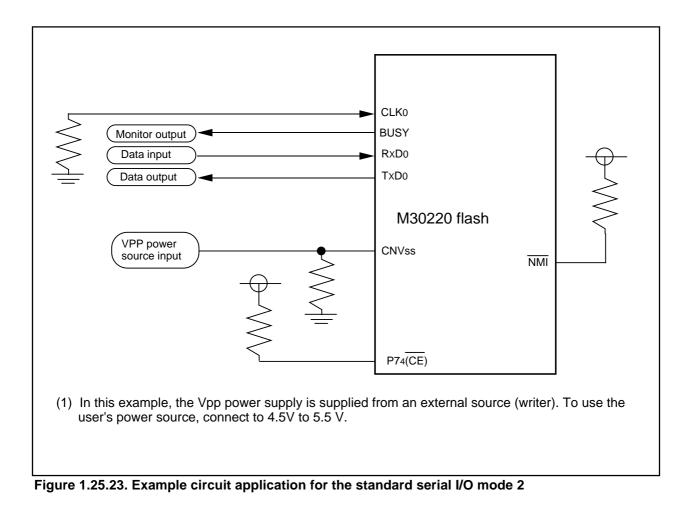

| 03D916<br>03DA16 | D-A register 1 (DA1)                                                 |