#### Data Sheet

#### August 2000 File Number 3035.2

## Radiation Hardened 16-Bit CMOS Microprocessor

intercil

The Intersil HS-80C86RH high performance radiation hardened 16-bit CMOS CPU is manufactured using a hardened field, self aligned silicon gate CMOS process. Two modes of operation, MINimum for small systems and MAXimum for larger applications such as multiprocessing, allow user configuration to achieve the highest performance level. Industry standard operation allows use of existing NMOS 8086 hardware and software designs.

Specifications for Rad Hard QML devices are controlled by the Defense Supply Center in Columbus (DSCC). The SMD numbers listed here must be used when ordering.

Detailed Electrical Specifications for these devices are contained in SMD 5962-95722. A "hot-link" is provided on our homepage for downloading. www.intersil.com/spacedefense/space.asp

#### **Ordering Information**

| ORDERING NUMBER   | INTERNAL<br>MKT. NUMBER | TEMP. RANGE<br>( <sup>o</sup> C) |

|-------------------|-------------------------|----------------------------------|

| 5962R9572201QQC   | HS1-80C86RH-8           | -55 to 125                       |

| 5962R9572201QXC   | HS9-80C86RH-8           | -55 to 125                       |

| 5962R9572201VQC   | HS1-80C86RH-Q           | -55 to 125                       |

| 5962R9572201VXC   | HS9-80C86RH-Q           | -55 to 125                       |

| HS1-80C86RH/Proto | HS1-80C86RH/Proto       | -55 to 125                       |

| HS9-80C86RH/Proto | HS9-80C86RH/Proto       | -55 to 125                       |

#### Features

- Electrically Screened to SMD # 5962-95722

- QML Qualified per MIL-PRF-38535 Requirements

- Radiation Performance

- Latch Up Free EPI-CMOS

- Total Dose......100 krad(Si) (Max)

- Low Power Operation

- ICCSB..... 500μA (Max)

- ICCOP ..... 12mA/MHz (Max)

- Pin Compatible with NMOS 8086 and Intersil 80C86

- Completely Static Design DC to 5MHz

- 1MB Direct Memory Addressing Capability

- 24 Operand Addressing Modes

- Bit, Byte, Word, and Block Move Operations

- 8-Bit and 16-Bit Signed/Unsigned Arithmetic

- Binary or Decimal

- Multiply and Divide

- Bus-Hold Circuitry Eliminates Pull-up Resistors for CMOS Designs

- Hardened Field, Self-Aligned, Junction-Isolated CMOS

Process

- Single 5V Power Supply

- Military Temperature Range ..... -35°C to 125°C

1

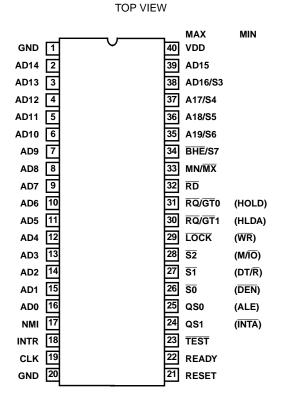

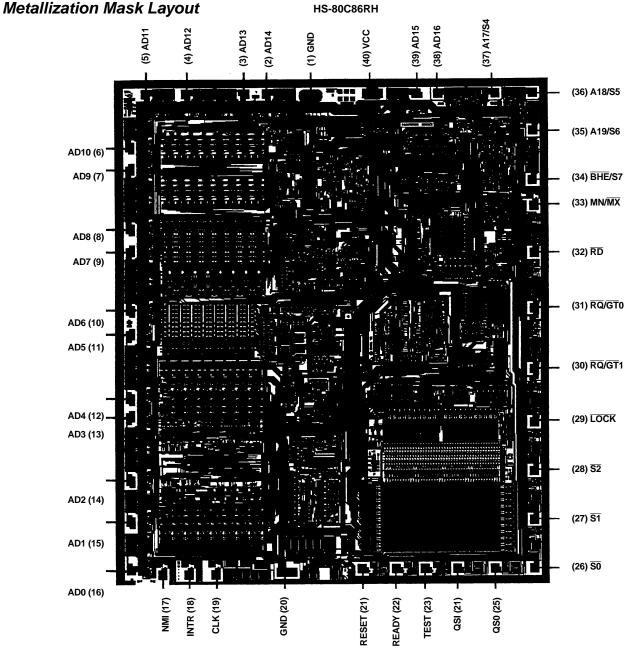

### Pinout

#### HS-80C86RH 40 LEAD CERAMIC DUAL-IN-LINE METAL SEAL PACKAGE (SBDIP) MIL-STD-1835, CDIP2-T40

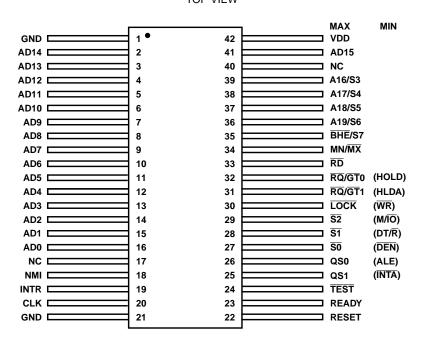

#### HS-80C86RH 42 LEAD CERAMIC METAL SEAL FLATPACK PACKAGE (FLATPACK) INTERSIL OUTLINE K42.A TOP VIEW

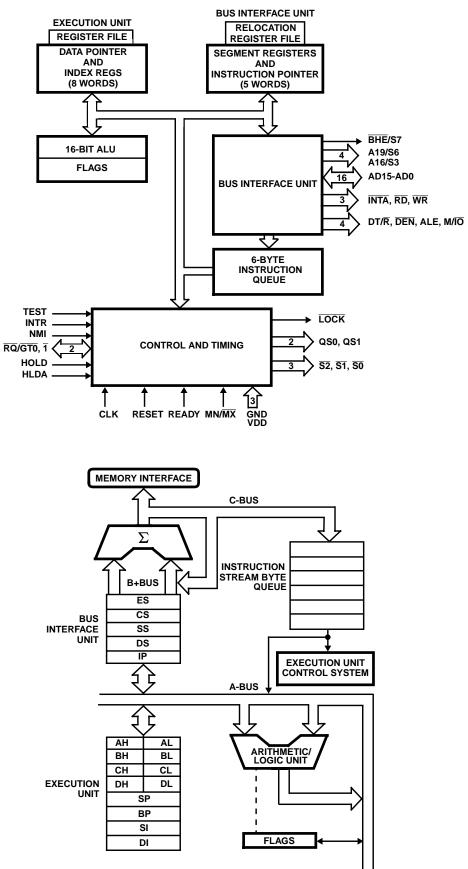

## **Functional Diagram**

# **Pin Descriptions**

| SYMBOL                               | PIN<br>NUMBER | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                       |  |  |

|--------------------------------------|---------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                                      |               |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ems in either minimum or maximum mode. The "Local Bus" in these descriptions 6RH (without regard to additional bus buffers).                                                                                                                                                                                                          |  |  |

| AD15-AD0                             | 2-16, 39      | I/O  | (T2, T3, TW, T4<br>during T1 wher<br>Eight-bit oriente<br>(See BHE). The                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ADDRESS DATA BUS: These lines constitute the time multiplexed memory/IO address (T1) and data (T2, T3, TW, T4) bus. AO is analogous to BHE for the lower byte of the data bus, pins D7-D0. It is LOW during T1 when a byte is to be transferred on the lower portion of the bus in memory or I/O operations. Eight-bit oriented devices tied to the lower half would normally use AD0 to condition chip select functions (See BHE). These lines are active HIGH and are held at high impedance to the last valid logic level during interrupt acknowledge and local bus "hold acknowledge" or "grant sequence". |                                                                                                                                                                                                                                                                                                                                       |  |  |

| A19/S6<br>A18/S5<br>A17/S4<br>A16/S3 | 35-38         | 0    | ADDRESS/STATUS: During T1, these are the four most significant address lines for memory operations<br>During I/O operations these lines are low. During memory and I/O operations, status information is<br>available on these lines during T2, T3, TW, T4. S6 is always zero. The status of the interrupt enable FLAG<br>bit (S5) is updated at the beginning of each CLK cycle. S4 and S3 are encoded.                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                       |  |  |

|                                      |               |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | s which segment register is presently being used for data accessing. These lines ance to the last valid logic level during local bus "hold acknowledge" or "grant                                                                                                                                                                     |  |  |

|                                      |               |      | S4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <b>S</b> 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                       |  |  |

|                                      |               |      | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Extra Data                                                                                                                                                                                                                                                                                                                            |  |  |

|                                      |               |      | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Stack                                                                                                                                                                                                                                                                                                                                 |  |  |

|                                      |               |      | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Code or None                                                                                                                                                                                                                                                                                                                          |  |  |

|                                      |               |      | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Data                                                                                                                                                                                                                                                                                                                                  |  |  |

| BHE/S7                               | 34            | 0    | BUS HIGH ENABLE/STATUS: During T1 the bus high enable signal (BHE) should be used to enable<br>onto the most significant half of the data bus, pins D15-D8. Eight bit oriented devices tied to the u<br>half of the bus would normally use BHE to condition chip select functions. BHE is LOW during T1 for u<br>write, and interrupt acknowledge cycles when a byte is to be transferred on the high portion of the<br>The S7 status information is available during T2, T3 and T4. The signal is active LOW, and is held at<br>impedance to the last valid logic level during interrupt acknowledge and local bus "hold acknowledge<br>"grant sequence"; it is LOW during T1 for the first interrupt acknowledge cycle. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                       |  |  |

|                                      |               |      | BHE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | A0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                       |  |  |

|                                      |               |      | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Whole Word                                                                                                                                                                                                                                                                                                                            |  |  |

|                                      |               |      | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Upper Byte from/to Odd Address                                                                                                                                                                                                                                                                                                        |  |  |

|                                      |               |      | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Lower Byte from/to Even Address                                                                                                                                                                                                                                                                                                       |  |  |

|                                      |               |      | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | None                                                                                                                                                                                                                                                                                                                                  |  |  |

| RD                                   | 32            | 0    | on the state of t<br>local bus. RD is<br>in T2 until the 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | the M/ <del>IO</del><br>active L<br>0C86 loc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | icates that the processor is performing a memory or I/O read cycle, depending or $\overline{S2}$ pin. This signal is used to read devices which reside on the HS-80C86RH OW during T2, T3 and TW of any read cycle, and is guaranteed to remain HIGH ral bus has floated.                                                             |  |  |

|                                      |               |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | n impedance logic one state during "hold acknowledge" or "grant sequence".                                                                                                                                                                                                                                                            |  |  |

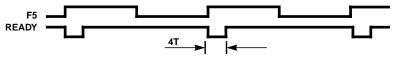

| READY                                | 22            | I    | READY: is the acknowledgment from the addressed memory or I/O device that will complete the data transfer. The RDY signal from memory or I/O is synchronized by the HS-82C85RH Clock Generator to form READY. This signal is active HIGH. The HS-80C86RH READY input is not synchronized. Correct operation is not guaranteed if the Setup and Hold Times are not met.                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                       |  |  |

| INTR                                 | 18            | I    | instruction to de interrupt service                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | etermine<br>e routine<br>ironized a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | : is a level triggered input which is sampled during the last clock cycle of each if the processor should enter into an interrupt acknowledge operation. If so, an is called via an interrupt vector lookup table located in system memory. INTR is and can be internally masked by software resetting the interrupt enable bit. This |  |  |

| TEST                                 | 23            | I    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | rocessor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ed by the "Wait" instruction. If the TEST input is LOW execution continues, waits in an "Idle" state. This input is synchronized internally during each clock e of CLK.                                                                                                                                                               |  |  |

# **Pin Descriptions** (Continued)

| SYMBOL            | PIN<br>NUMBER                                                           | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

|-------------------|-------------------------------------------------------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

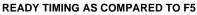

| NMI               | 17                                                                      | I    | NON-MASKABLE INTERRUPT: is an edge triggered input which causes a type 2 interrupt. An interrupt service routine is called via an interrupt vector lookup table located in system memory. NMI is not maskable internally by software. A transition from LOW to HIGH initiates the interrupt at the end of the current instruction. This input is internally synchronized.                                                                                                                                                                                                              |  |

| RESET             | 21                                                                      | I    | RESET: causes the processor to immediately terminate its present activity. The signal must change fro LOW to HIGH and remain active HIGH for at least 4 CLK cycles. It restarts execution, as described in the Instruction Set description, when RESET returns LOW. RESET is internally synchronized.                                                                                                                                                                                                                                                                                  |  |

| CLK               | 19                                                                      | I    | CLOCK: provides the basic timing for the processor and bus controller. It is asymmetric with a 33% duty cycle to provide optimized internal timing.                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| VDD               | 40                                                                      |      | VDD: +5V power supply pin. A $0.1\mu$ F capacitor between pins 20 and 40 is recommended for decoupling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| GND               | 1, 20                                                                   |      | GND: Ground. Note: both must be connected. A $0.1\mu F$ capacitor between pins 1 and 20 is recommended for decoupling.                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| MN/MX             | 33                                                                      | I    | MINIMUM/MAXIMUM: Indicates what mode the processor is to operate in. The two modes are discussed in the following sections.                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

|                   |                                                                         |      | re for the HS-80C86RH system in maximum mode (i.e., $MN/\overline{MX} = GND$ ). Only the pin functions which are d below.                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| <u>50, 51, 52</u> | que to maximum mode are described b<br>10, S1, S2 26-28 O S I I I I b s |      | STATUS: is active during T4, T1 and T2 and is returned to the passive state (1,1,1) during T3 or during TW when READY is HIGH. This status is used by the 82C88 Bus Controller to generate all memory and I/O access control signals. Any change by $\overline{S2}$ , $\overline{S1}$ , or $\overline{S0}$ during T4 is used to indicate the beginning of a bus cycle, and the return to the passive state in T3 or TW is used to indicate the end of a bus cycle. These status lines are encoded. These signals are held at a high impedance logic one state during "grant sequence". |  |

**S**0

Interrupt Acknowledge

Read I/O Port

Write I/O Port

Code Access

Read Memory

Write Memory Passive

Halt

S2

**S1**

# HS-80C86RH

# Pin Descriptions (Continued)

| SYMBOL           | PIN<br>NUMBER | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

|------------------|---------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

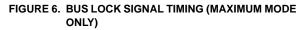

| RQ/GT0<br>RQ/GT1 | 31, 30        | I/O  | REQUEST/GRANT: pins are used by other local bus masters to force the processor to release the local bus at the end of the processor's current bus cycle. Each pin is bidirectional with RQ/GT0 having highe priority than RQ/GT1. RQ/GT has an internal pull-up bus hold device so it may be left unconnected. The request/grant sequence is as follows (see RQ/GT Sequence Timing.)                                                        |  |  |

|                  |               |      | 1. A pulse of 1 CLK wide from another local bus master indicates a local bus request ("hold") to the HS-80C86RH (pulse 1).                                                                                                                                                                                                                                                                                                                  |  |  |

|                  |               |      | 2. During a T4 or T1 clock cycle, a pulse 1 CLK wide from the HS-80C86RH to the requesting master (pulse 2) indicates that the HS-80C86RH has allowed the local bus to float and that it will enter the "grant sequence" state at the next CLK. The CPU's bus interface unit is disconnected logically from the local bus during "grant sequence".                                                                                          |  |  |

|                  |               |      | <ol> <li>A pulse 1 CLK wide from the requesting master indicates to the HS-80C86RH (pulse 3) that the "hold"<br/>request is about to end and that the HS-80C86RH can reclaim the local bus at the next CLK. The<br/>CPU then enters T4 (or T1 if no bus cycles pending).</li> </ol>                                                                                                                                                         |  |  |

|                  |               |      | Each Master-Master exchange of the local bus is a sequence of 3 pulses. There must be one idle CLK cycle after each bus exchange. Pulses are active low.                                                                                                                                                                                                                                                                                    |  |  |

|                  |               |      | If the request is made while the CPU is performing a memory cycle, it will release the local bus during T4 of the cycle when all the following conditions are met:                                                                                                                                                                                                                                                                          |  |  |

|                  |               |      | 1. Request occurs on or before T2.                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

|                  |               |      | 2. Current cycle is not the low byte of a word (on an odd address).                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|                  |               |      | 3. Current cycle is not the first acknowledge of an interrupt acknowledge sequence.                                                                                                                                                                                                                                                                                                                                                         |  |  |

|                  |               |      | 4. A locked instruction is not currently executing.                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|                  |               |      | If the local bus is idle when the request is made the two possible events will follow:                                                                                                                                                                                                                                                                                                                                                      |  |  |

|                  |               |      | 1. Local bus will be released during the next cycle.                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

|                  |               |      | <ol> <li>A memory cycle will start within 3 CLKs. Now the four rules for a currently active memory cycle<br/>apply with condition number 1 already satisfied.</li> </ol>                                                                                                                                                                                                                                                                    |  |  |

| LOCK             | 29            | 0    | LOCK: output indicates that other system bus masters are not to gain control of the system bus while LOCK is active LOW. The LOCK signal is activated by the "LOCK" prefix instruction and remains active until the completion of the next instruction. This signal is active LOW, and is held at a HIGH impedance logic one state during "grant sequence". In MAX mode, LOCK is automatically generated during T2 of the first INTA cycle. |  |  |

| QS1, QS0         | 24, 25        | 0    | QUEUE STATUS: The queue status is valid during the CLK cycle after which the queue operation is performed.                                                                                                                                                                                                                                                                                                                                  |  |  |

|                  |               |      | QS1 and QS2 provide status to allow external tracking of the internal HS-80C86RH instruction queue Note that QS1, QS0 never become high impedance.                                                                                                                                                                                                                                                                                          |  |  |

|                  |               |      | QS1 QS0                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

|                  |               |      | 0 0 No Operation                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

|                  |               |      | 0 1 First Byte of Opcode from Queue                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|                  |               |      | 1 0 Empty the Queue                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|                  |               |      | 1 1 Subsequent Byte from Queue                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| • •              |               | •    | are for the HS-80C86RH in minimum mode (i.e., $MN/\overline{MX} = VDD$ ). Only the pin functions which are unique er pin functions are as described below.                                                                                                                                                                                                                                                                                  |  |  |

| M/IO             | 28            | 0    | STATUS LINE: logically equivalent to $\overline{S2}$ in the maximum mode. It is used to distinguish a memor access from an I/O access. M/IO becomes valid in the T4 preceding a bus cycle and remains valid unt the final T4 of the cycle (M = HIGH, IO = LOW). M/IO is held to a high impedance logic zero during loca bus "hold acknowledge".                                                                                             |  |  |

| WR               | 29            | 0    | WRITE: indicates that the processor is performing a write memory or write I/O cycle, depending on the state of the M/IO signal. WR is active for T2, T3 and TW of any write cycle. It is active LOW, and is held to high impedance logic one during local bus "hold acknowledge".                                                                                                                                                           |  |  |

| INTA             | 24            | 0    | INTERRUPT ACKNOWLEDGE: is used as a read strobe for interrupt acknowledge cycles. It is activ LOW during T2, T3 and TW of each interrupt acknowledge cycle. Note that INTA is never floated.                                                                                                                                                                                                                                                |  |  |

## **Pin Descriptions** (Continued)

| SYMBOL       | PIN<br>NUMBER | TYPE   | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|--------------|---------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ALE          | 25            | 0      | ADDRESS LATCH ENABLE: is provided by the processor to latch the address into the 82C82 latch. It is a HIGH pulse active during clock LOW of T1 of any bus cycle. Note that ALE is never floated.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| DT/R         | 27            | 0      | DATA TRANSMIT/RECEIVE: is needed in a minimum system that desires to use a data bus transceiver. It is used to control the direction of data flow through the transceiver. Logically, $DT/\overline{R}$ is equivalent to $\overline{S1}$ in maximum mode, and its timing is the same as for $M/\overline{IO}$ (T = HIGH, R = LOW). $DT/\overline{R}$ is held to a high impedance logic one during local bus "hold acknowledge".                                                                                                                                                                                                                                                    |

| DEN          | 26            | 0      | DATA ENABLE: provided as an output enable for a bus transceiver in a minimum system which uses the transceiver. DEN is active LOW during each memory and I/O access and for INTA cycles. For a read or INTA cycle it is active from the middle of T2 until the middle of T4, while for a write cycle it is active from the beginning of T2 until the middle of T4. DEN is held to a high impedance logic one during local bus "hold acknowledge".                                                                                                                                                                                                                                  |

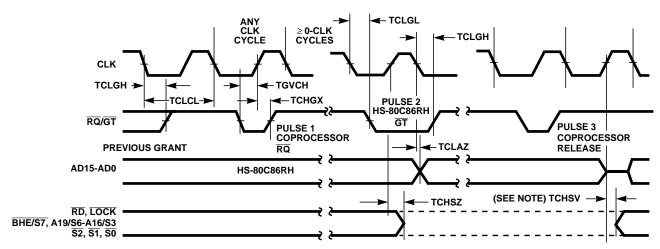

| HOLD<br>HLDA | 31<br>30      | I<br>O | HOLD: indicates that another master is requesting a local bus "hold". To be a acknowledged, HOLD must<br>be active HIGH. The processor receiving the "hold" will issue a "hold acknowledge" (HLDA) in the middle<br>of a T4 or T1 clock cycle. Simultaneously with the issuance of HLDA, the processor will float the local bus<br>and control lines. After HOLD is detected as being LOW, the processor will lower HLDA, and when the<br>processor needs to run another cycle, it will again drive the local bus and control lines.<br>HOLD is not an asynchronous input. External synchronization should be provided if the system cannot<br>otherwise guarantee the setup time. |

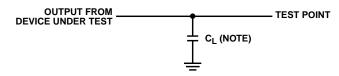

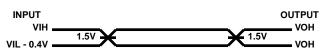

## AC Test Circuit

## AC Testing Input, Output Waveform

NOTE: All inputs signals (other than CLK) must switch between VIL Max -0.4V and VIH Min +0.4. CLK must switch between 0.4V and VDD -0.4V. TR and TF must be less than or equal to 15ns. CLK TR and TF must be less than or equal to 10ns.

# Timing Diagrams

NOTE: Includes stray and jig capacitance.

RESET, NMI, AND MN/MX TIMING AS COMPARED TO F14 AND F16

- 4. F0 = 100kHz, 50% duty cycle square wave.

- F1 = F0/2, F2 = F1/2 . . . F16 = F15/2.

- 5. READY, RESET, and NMI timing are as shown:  $T = 10\mu s$ .

- 6. All signals have rise/fall time limits: 100ns < t-rise, t-fall < 500ns.

- 7. RESET has a pulse width = 8T and occurs every two cycles of F16.

- 8. NMI has a pulse width = 4T and occurs every two cycles of F16.

- 9. MN/ $\overline{\text{MX}}$  is a 50% duty cycle square wave and changes every eight cycles of F16.

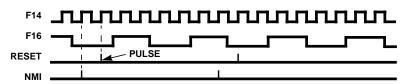

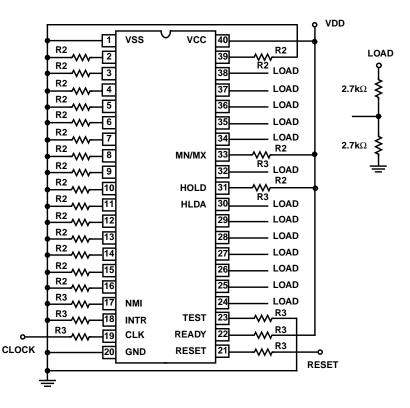

# Irradiation Circuit

- 10. VDD =  $5.0V \pm 0.5V$

- 11.  $R2 = 3.3k\Omega$ ,  $R3 = 47k\Omega$

- 12. Pins Tied to GND: 1-18, 20, 23, 39 Pins Tied to VCC: 22, 31, 33, 40 Pins With Loads: 24-29, 30, 32, 34-38 Pins Brought Out: 19 (Clock), 21 (Reset)

- 13. Clock and reset should be brought out separately so they can be toggled before irradiation.

- 14. Group E Sample Size is 2 Die/Wafer.

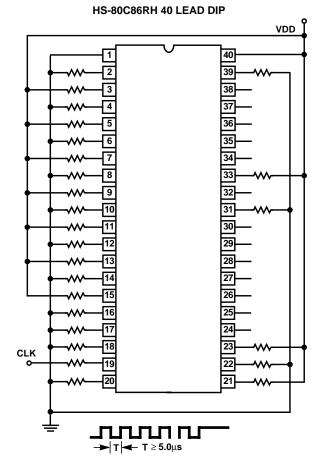

## **Burn-In Circuits**

#### STATIC

#### NOTES:

- 15.  $VDD = +6.5V \pm 10\%$ .

- 16.  $T_A = 125^{\circ}C$  Minimum.

- 17. Part is Static Sensitive.

- 18. Voltages Must Be Ramped.

- 19. Package: 40 Lead DIP.

- 20. Resistors:

$\begin{array}{l} 10 \text{k}\Omega \pm 10\% \\ (\text{Pins } 17, 18, 21\text{-}23, 31, 33) \\ 2.7 \text{k}\Omega \pm 5\% \ (\text{Pins } 2\text{-}16, 39) \\ 1.0 \text{k}\Omega \pm 5\% \ 1/10W \ \text{Min} \ (\text{Pin } 19) \\ \text{Minimum of } 5 \ \text{CLK Pulses} \\ \text{After Initial Pulses, CLK is Left High} \\ \text{Pulses are } 50\% \ \text{Duty Cycle Square Wave} \end{array}$

#### DYNAMIC

#### NOTES:

- 21. VDD = 6.5V ±5% (Burn-In).

- 22. VDD = 6.0V ±5% (Life Test).

- 23. T<sub>A</sub> = 125<sup>o</sup>C.

- 24. Package: 40 Lead DIP.

- 25. Part is Static Sensitive.

- 26. Voltage Must Be Ramped.

- 27. Resistors: 10kΩ (Pins 17, 18, 21, 22, 23, 33) 3.3kΩ (Pins 2-16, 19, 30, 31, 39) 2.7kΩ Loads As Indicated All Resistors Are At Least 1/8W, ±10% F0 = 100kHz, F1 = F0/2, F2 = F1/2... RESET, NMI low after initialization. READY pulsed low every 320ms MN/MX changes state every 5.24s

9

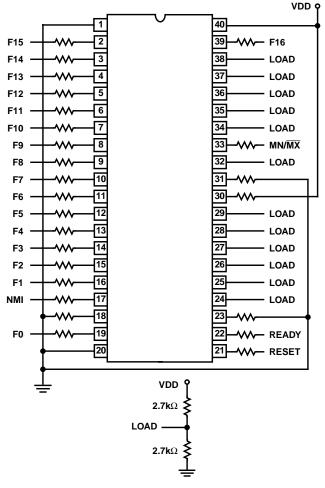

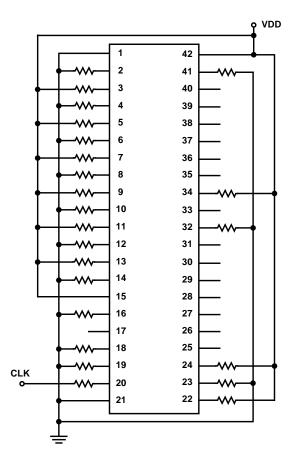

## Burn-In Circuits (Continued) HS-80C86RH 42 LEAD FLATPACK

#### HS-80C86RH 42 LEAD FLATPACK

#### STATIC

#### NOTES:

- 28. VDD = +6.5V  $\pm 10\%$ .

- 29.  $T_A = 125^{\circ}C$  Minimum.

- 30. Part is Static Sensitive.

- 31. Voltages Must Be Ramped.

- 32. Package: 42 Lead Flatpack.

- 33. Resistors: 10k $\Omega \pm 10\%$ (Pins 18, 19, 22-24, 32, 34) 2.7k $\Omega \pm 5\%$  (Pins 2-16, 41) 1.0k $\Omega \pm 5\%$  1/10W Min (Pin 20) Minimum of 5 CLK Pulses After Initial Pulses, CLK is Left High Pulses are 50% Duty Cycle Square Wave

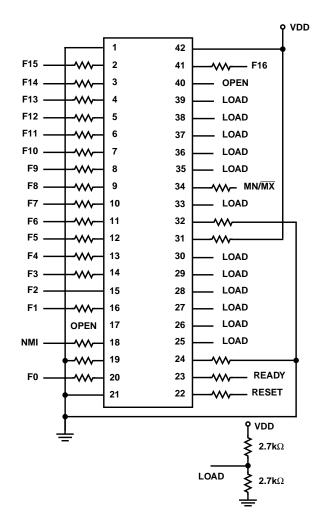

#### DYNAMIC

- 34. VDD = 6.5V ±5% (Burn-In).

- 35. VDD = 6.0V ±5% (Life Test).

- 36.  $T_A = 125^{\circ}C$ .

- 37. Package: 42 Lead Flatpack.

- 38. Part is Static Sensitive.

- 39. Voltage Must Be Ramped.

- 40. Resistors: 10k $\Omega$  (Pins 17, 18, 19, 22, 23, 24, 34) 3.3k $\Omega$  (Pins 2-16, 20, 31, 32, 41) 2.7k $\Omega$  Loads As Indicated All Resistors Are At Least 1/8W, ±10% F0 = 100kHz, F1 = F0/2, F2 = F1/2... RESET, NMI low after initialization. READY pulsed low every 320µs MN/MX changes state every 5.24s

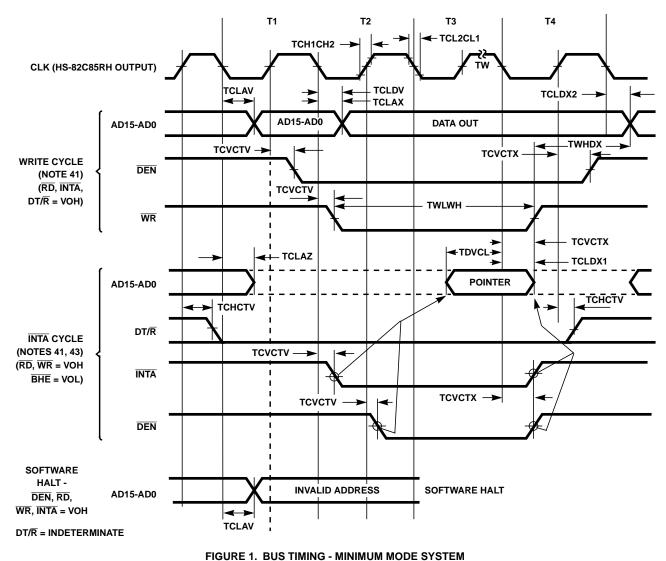

## Waveforms

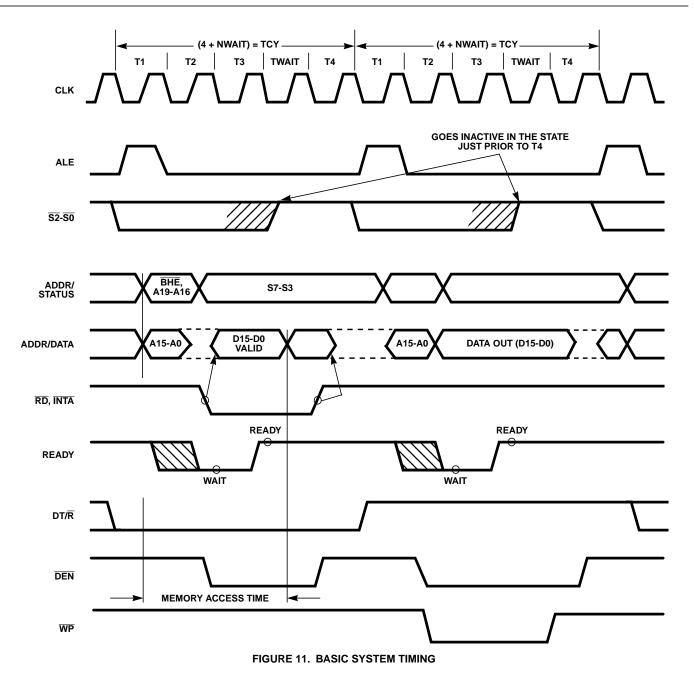

- 41. All signals switch between VOH and VOL unless otherwise specified.

- 42. RDY is sampled near the end of T2, T3, TW to determine if TW machines states are to be inserted.

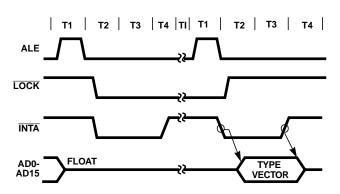

- 43. Two INTA cycles run back-to-back. The HS-80C86RH local ADDR/DATA bus is inactive during both INTA cycles. Control signals are shown for the second INTA cycle.

- 44. Signals at HS-82C85RH are shown for reference only.

- 45. All timing measurements are made at 1.5V unless otherwise noted.

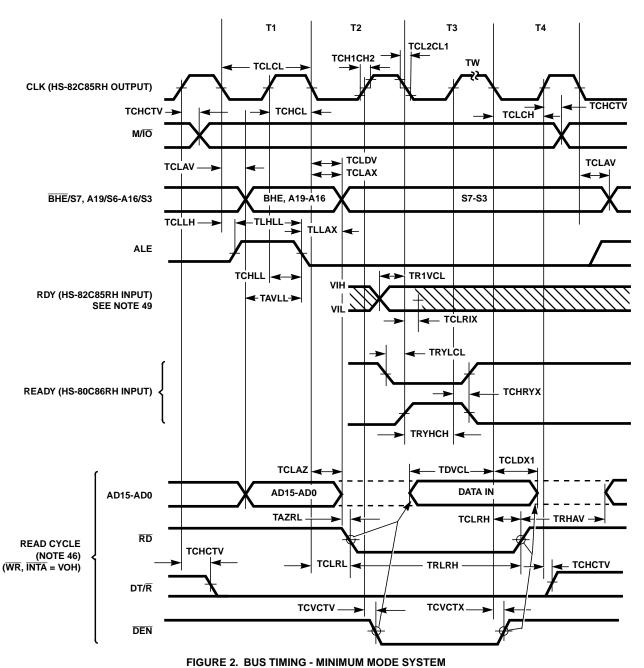

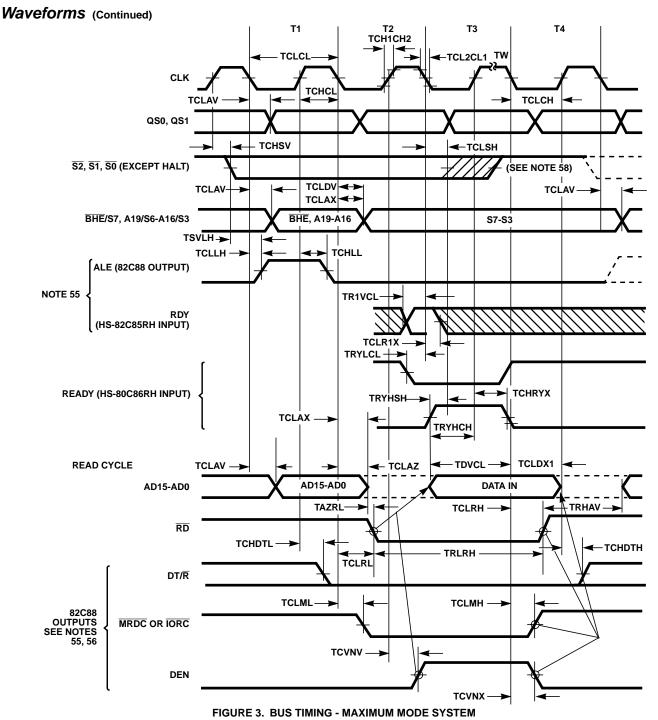

Waveforms (Continued)

- 46. All signals switch between VOH and VOL unless otherwise specified.

- 47. RDY is sampled near the end of T2, T3, TW to determine if TW machines states are to be inserted.

- 48. Two INTA cycles run back-to-back. The HS-80C86RH local ADDR/DATA bus is inactive during both INTA cycles. Control signals are shown for the second INTA cycle.

- 49. Signals at HS-82C85RH are shown for reference only.

- 50. All timing measurements are made at 1.5V unless otherwise noted.

- 51. All signals switch between VOH and VOL unless otherwise specified.

- 52. RDY is sampled near the end of T2, T3, TW to determine if TW machines states are to be inserted.

- 53. Cascade address is valid between first and second  $\overline{\text{INTA}}$  cycle.

- 54. Two INTA cycles run back-to-back. The HS-80C86RH local ADDR/DATA bus is inactive during both INTA cycles. Control for pointer address is shown for the second INTA cycle.

- 55. Signals at HS-82C85RH or 82C88 are shown for reference only.

- 56. The issuance of the 82C88 command and control signals (MRDC, MWTC, AMWC, IORC, IOWC, AIOWC, INTA and DEN) lags the active high 82C88 CEN.

- 57. All timing measurements are made at 1.5V unless otherwise noted.

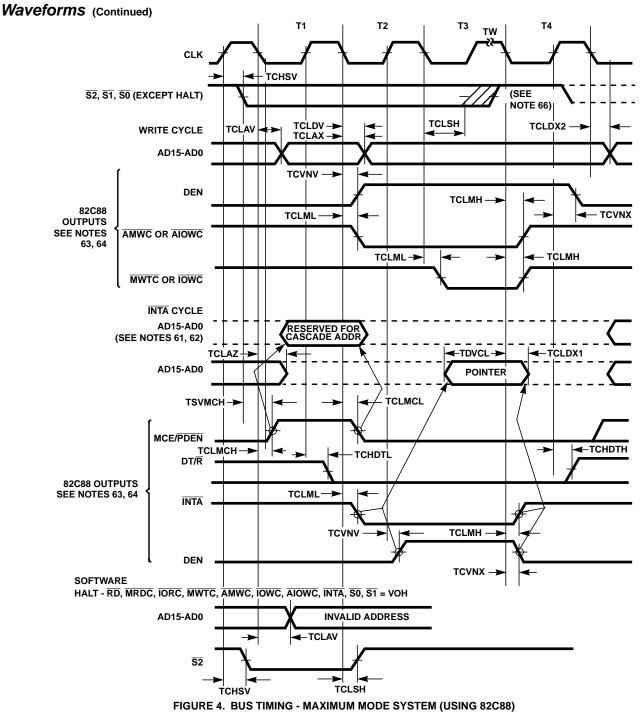

- 58. Status inactive in state just prior to T4.

- 59. All signals switch between VOH and VOL unless otherwise specified.

- 60. RDY is sampled near the end of T2, T3, TW to determine if TW machines states are to be inserted.

- 61. Cascade address is valid between first and second INTA cycle.

- 62. Two INTA cycles run back-to-back. The HS-80C86RH local ADDR/DATA bus is inactive during both INTA cycles. Control for pointer address is shown for the second INTA cycle.

- 63. Signals at HS-82C85RH or 82C88 are shown for reference only.

- 64. The issuance of the 82C88 command and control signals (MRDC, MWTC, AMWC, IORC, IOWC, AIOWC, INTA and DEN) lags the active high 82C88 CEN.

- 65. All timing measurements are made at 1.5V unless otherwise noted.

- 66. Status inactive in state just prior to T4.

#### Waveforms (Continued)

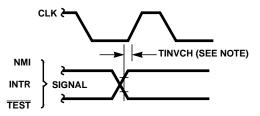

NOTE: Setup Requirements for asynchronous signals only to guarantee recognition at next CLK.

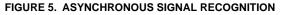

NOTE: The coprocessor may not drive the buses outside the region shown without risking contention. FIGURE 7. REQUEST/GRANT SEQUENCE TIMING (MAXIMUM MODE ONLY)

FIGURE 8. HOLD/HOLD ACKNOWLEDGE TIMING (MINIMUM MODE ONLY)

# Functional Description

### Static Operation

All HS-80C86RH circuitry is of static design. Internal registers, counters and latches are static and require no refresh as with dynamic circuit design. This eliminates the minimum operating frequency restriction placed on other microprocessors. The CMOS HS-80C86RH can operate from DC to 5MHz. The processor clock may be stopped in either state (HIGH/LOW) and held there indefinitely. This type of operation is especially useful for system debug or power critical applications.

The HS-80C86RH can be single stepped using only the CPU clock. This state can be maintained as long as is necessary. Single step clock operation allows simple interface circuitry to provide critical information for bringing up your system.

Static design also allows very low frequency operation (down to DC). In a power critical situation, this can provide extremely low power operation since HS-80C86RH power dissipation is directly related to operating frequency. As the system frequency is reduced, so is the operating power until, ultimately, at a DC input frequency, the HS-80C86RH power requirement is the standby current, ( $500\mu$ A maximum).

### Internal Architecture

The internal functions of the HS-80C86RH processor are partitioned logically into two processing units. The first is the Bus Interface Unit (BIU) and the second is the Execution Unit (EU) as shown in the CPU functional diagram.

These units can interact directly but for the most part perform as separate asynchronous operational processors. The bus interface unit provides the functions related to instruction fetching and queuing, operand fetch and store, and address relocation. This unit also provides the basic bus control. The overlap of instruction pre-fetching provided by this unit serves to increase processor performance through improved bus bandwidth utilization. Up to 6 bytes of the instruction stream can be queued while waiting for decoding and execution.

The instruction stream queuing mechanism allows the BIU to keep the memory utilized very efficiently. Whenever there is space for at least 2 bytes in the queue, the BIU will attempt a word fetch memory cycle. This greatly reduces "dead-time" on the memory bus. The queue acts as a First-In-First-Out (FIFO) buffer, from which the EU extracts instruction bytes as required. If the queue is empty (following a branch instruction, for example), the first byte into the queue immediately becomes available to the EU.

The execution unit receives pre-fetched instructions from the BIU queue and provides un-relocated operand addresses to the BIU. Memory operands are passed through the BIU for processing by the EU, which passes results to the BIU for storage.

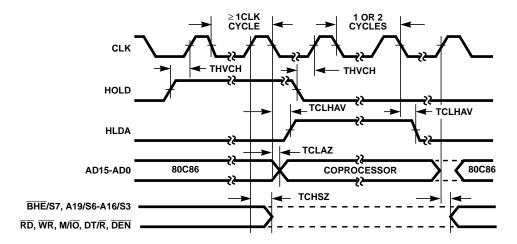

### Memory Organization

The processor provides a 20-bit address to memory, which locates the byte being referenced. The memory is organized as a linear array of up to 1 million bytes, addressed as 00000(H) to FFFFF(H). The memory is logically divided into code, data, extra and stack segments of up to 64K bytes each, with each segment falling on 16 byte boundaries. (See Figure 9).

| TYPE OF MEMORY<br>REFERENCE    | DEFAULT<br>SEGMENT<br>BASE | ALTERNATE<br>SEGMENT<br>BASE | OFFSET               |  |  |  |

|--------------------------------|----------------------------|------------------------------|----------------------|--|--|--|

| Instruction Fetch              | CS                         | None                         | IP                   |  |  |  |

| Stack Operation                | SS                         | None                         | SP                   |  |  |  |

| Variable<br>(Except Following) | DS                         | CS, ES, SS                   | Effective<br>Address |  |  |  |

| String Source                  | DS                         | CS, ES, SS                   | SI                   |  |  |  |

| String Destination             | ES                         | None                         | DI                   |  |  |  |

| BP Used as Base<br>Register    | SS                         | CS, DS, ES                   | Effective<br>Address |  |  |  |

TABLE 1.

All memory references are made relative to base addresses contained in high speed segment registers. The segment types were chosen based on the addressing needs of programs. The segment register to be selected is automatically chosen according to the specific rules of Table 1. All information in one segment type share the same logical attributes (e.g., code or data). By structuring memory into relocatable areas of similar characteristics and by automatically selecting segment registers, programs are shorter, faster and more structured. (See Table 1).

Word (16-bit) operands can be located on even or odd address boundaries and are thus not constrained to even boundaries as is the case in many 16-bit computers. For address and data operands, the least significant byte of the word is stored in the lower valued address location and the most significant byte in the next higher address location. The BIU automatically performs the proper number of memory accesses, one if the word operand is on an even byte boundary and two if it is on an odd byte boundary. Except for the performance penalty, this double access is transparent to the software. The performance penalty does not occur for instruction fetches; only word operands.

Physically, the memory is organized as a high bank (D15-D6) and a low bank (D7-D0) of 512K bytes addressed in parallel by the processor's address lines.

Byte data with even addresses is transferred on the D7-D0 bus lines while odd addressed byte data (A0 HIGH) is transferred on the D15-D6 bus lines. The processor provides two enable signals, BHE and A0, to selectively allow reading from or writing into either an odd byte location, even byte location, or both. The instruction stream is fetched from memory as words and is addressed internally by the processor at the byte level as necessary.

In referencing word data, the BIU requires one or two memory cycles depending on whether the starting byte of the word is on an even or odd address, respectively. Consequently, in referencing word operands performance can be optimized by locating data on even address boundaries. This is an especially useful technique for using the stack, since odd address references to the stack may adversely affect the context switching time for interrupt processing or task multiplexing.

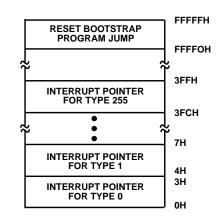

Certain locations in memory are reserved for specific CPU operations (See Figure 10). Locations from address FFFF0H through FFFFFH are reserved for operations including a jump to the initial program loading routine. Following RESET, the CPU will always begin execution at location FFF0H where the jump must be located. Locations 00000H through 003FFH are reserved for interrupt operations. Each of the 256 possible interrupt service routines is accessed through its own pair of 16-bit pointers - segment address pointer and offset address pointer. The first pointer, used as the offset address, is loaded into the 1P and the second pointer, which designates the base address is loaded into the CS. At this point program control is transferred to the interrupt routine. The pointer elements are assumed to have been stored at the respective places in reserved memory prior to occurrence of interrupts.

FIGURE 10. RESERVED MEMORY LOCATIONS

## Minimum and Maximum Operation Modes

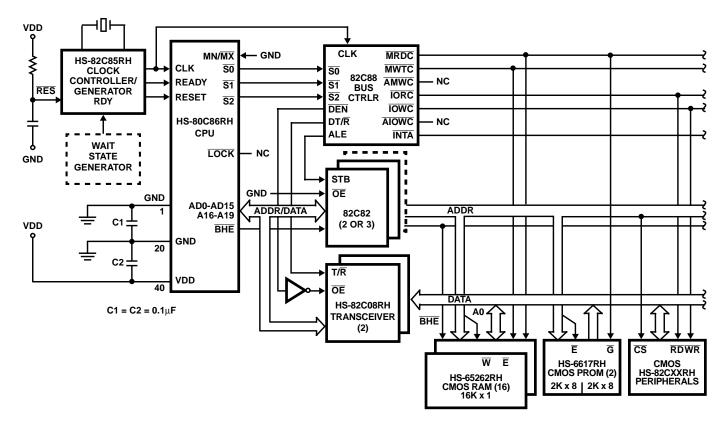

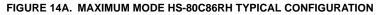

The requirements for supporting minimum and maximum HS-80C86RH systems are sufficiently different that they cannot be met efficiently using 40 uniquely defined pins. Consequently, the HS-80C86RH is equipped with a strap pin  $(MN/\overline{MX})$  which defines the system configuration. The definition of a certain subset of the pins changes, dependent on the condition of the strap pin. When the MN/\overline{MX} pin is strapped to GND, the HS-80C86RH defines pins 24 through 31 and 34 in maximum mode. When the MN/\overline{MX} pin is strapped to VDD, the HS-80C86RH generates bus control signals itself on pins 24 through 31 and 34.

### **Bus Operation**