# *Multi***GEN**<sup>™</sup> GF9105A Component Digital Transcoder

DATA SHEET

#### **FEATURES**

- drop in replacement for the GF9105 with lower power and increased functionality

- · new mode for HVF output

- new mode for using low frequency clocks with nonmultiplexed I/O data

- optimized HOST IF control signals for ensured shared bus compatibility

- · multiple format conversions from one device

4:2:2:4 <-> 4:4:4:4

4:2:2:4 <-> R/G/B/KEY

4:2:2:4 <-> Y/U/V/KEY

Y/U/V/KEY <-> R/G/B/KEY

4:4:4:4 <-> R/G/B/KEY

4:4:4:4 <-> Y/U/V/KEY

- ITU-R-601 compliant interpolation/decimation filters

- supports both single link 4:4:4:4 (SMPTE RP174) and dual link 4:4:4:4 (SMPTE RP175) compliant I/O

- transparent conversions between Y/U/V and R/G/B color spaces.

- fully programmable 3X3 Color Space Converter (CSC)

- 13 bit Color Space Converter coefficients

- 13 bit KEY Channel scaling coefficient

- multiplexed and non-multiplexed I/O data

- · bi-directional I/O data ports with tri-stating

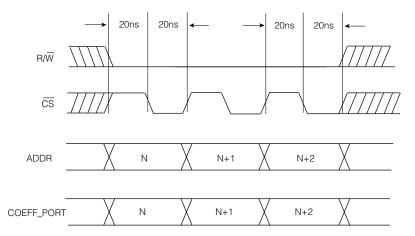

- parallel HOST IF for reading and writing multiplier coefficients and device configuration words

- single +5V power supply.

#### **ORDERING INFORMATION**

| PART NUMBER | PACKAGE      |

|-------------|--------------|

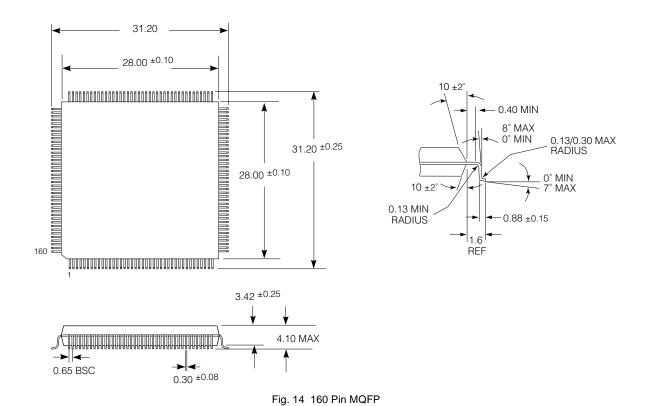

| GF9105ACQQ  | 160 Pin MQFP |

#### **DEVICE OVERVIEW**

The GF9105A is a drop in replacement for the GF9105 with lower power and increased functionality. This increased functionality gives the user the option of having HVF output signals and the option of using a low frequency clock when operating with non-multiplexed input and output data. The GF9105A is a flexible VDSP engine capable of performing a variety of format conversions. The flexible architecture of the GF9105A also allows the user to perform a wide range of DSP functions that require a general 3X3 multiplier structure and/or high performance 1:2 interpolation and 2:1 decimation filters. Device configuration is selected by writing configuration words through an asynchronous parallel interface (HOST IF).

The GF9105A accepts either multiplexed or non-multiplexed input data and may produce either multiplexed or non-multiplexed output data. External H, V and F inputs allow for the insertion of TRS words into multiplexed output data streams.

All interpolation and decimation filtering required for ITU-R-601 compliant 4:2:2:4 <-> 4:4:4:4 sample rate conversions has been integrated into the GF9105A. In addition, all input and output offset adjustments required for transparent conversions between the Y/U/V and R/G/B color spaces have been included within the GF9105A.

The color space converter within the GF9105A has 13 bit multiplier coefficients, has 13 bit output resolution, maintains full precision throughout the 3X3 calculation and has a true unity gain by-pass mode. Sufficient resolution is maintained within the color space converter to ensure that truly transparent Y/U/V <-> R/G/B conversions may be achieved. A user programmable output clipper allows the GF9105A to output a variety of word lengths to meet specific system requirements.

The GF9105A is packaged in a 160 pin MQFP package, operates from a single +5V supply.

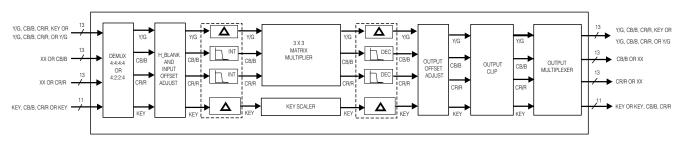

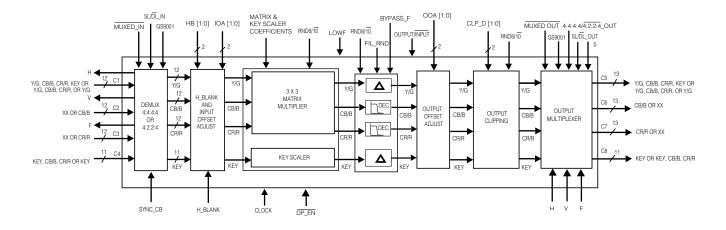

**GENERAL FUNCTIONALITY OF GF9105A CORE**

Revision Date: March 2000 Document No. 521 - 88 - 03

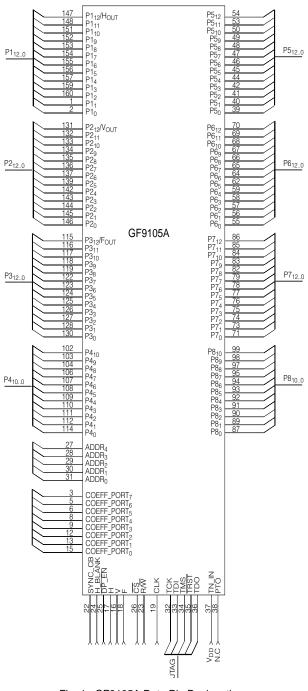

# PIN DESCRIPTION

| PIN NO.                                                                                       | SYMBOL                   | DESCRIPTION                                                                                                                                                                                                                                         |

|-----------------------------------------------------------------------------------------------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11, 20, 51, 60, 80,<br>101, 121, 141, 150                                                     | $V_{DD}$                 | +5 V ±5% power supply.                                                                                                                                                                                                                              |

| 4, 7, 10, 14, 21, 43, 52, 61, 63, 72, 81, 88, 96, 100, 105, 113, 120, 129, 138, 140, 149, 158 | GND                      | Ground.                                                                                                                                                                                                                                             |

| 147, 148, 151-157,<br>159, 160, 1, 2                                                          | P1 <sub>120</sub>        | Data Port No. 1: Depending on device configuration, P1 <sub>120</sub> may operate as an input data port or an output data port. Note: When HVF output is enabled H is always presented on P1 <sub>12</sub> regardless of the state of INPUT/OUTPUT. |

| 131-137, 139, 142-<br>146                                                                     | P2 <sub>120</sub>        | Data Port No. 2: Depending on device configuration, P2 <sub>120</sub> may operate as an input data port or an output data port. Note: When HVF output is enabled V is always presented on P2 <sub>12</sub> regardless of the state of INPUT/OUTPUT. |

| 115-119, 122-128,<br>130                                                                      | P3 <sub>120</sub>        | Data Port No. 3: Depending on device configuration, P3 <sub>120</sub> may operate as an input data port or an output data port. Note: When HVF output is enabled F is always presented on P3 <sub>12</sub> regardless of the state of INPUT/OUTPUT. |

| 102-104, 106-112,<br>114                                                                      | P4 <sub>100</sub>        | Data Port No. 4: Depending on device configuration, P4 <sub>100</sub> may operate as an input data port or an output data port.                                                                                                                     |

| 54, 53, 50-44, 42-39                                                                          | P5 <sub>120</sub>        | Data Port No. 5: Depending on device configuration, P5 <sub>120</sub> may operate as an input data port or an output data port.                                                                                                                     |

| 70-64, 62, 59-55                                                                              | P6 <sub>120</sub>        | Data Port No. 6: Depending on device configuration, P6 <sub>120</sub> may operate as an input data port or an output data port.                                                                                                                     |

| 86-82, 79-73, 71                                                                              | P7 <sub>120</sub>        | Data Port No. 7: Depending on device configuration, P7 <sub>120</sub> may operate as an input data port or an output data port.                                                                                                                     |

| 99-97, 95-89, 87                                                                              | P8 <sub>100</sub>        | Data Port No. 8: Depending on device configuration, P8 <sub>100</sub> may operate as an input data port or an output data port.                                                                                                                     |

| 22                                                                                            | SYNC_CB                  | Synchronization: Control signal input. SYNC_CB is used to synchronize the GF9105A to the incoming data stream.                                                                                                                                      |

| 24                                                                                            | H_BLANK                  | Horizontal Blanking: Control signal input. H_BLANK is used to replace portions of the input data with a user selectable set of blanking levels.                                                                                                     |

| 25                                                                                            | DP_EN                    | Data Port Enable: Control signal input. DP_EN is used to enable and disable data ports P1 - P8.                                                                                                                                                     |

| 17                                                                                            | Н                        | Horizontal: Control signal input. H identifies the horizontal blanking interval for the output multiplexer.                                                                                                                                         |

| 16                                                                                            | V                        | Vertical: Control signal input. V identifies the vertical blanking interval for the output multiplexer.                                                                                                                                             |

| 18                                                                                            | F                        | Field: Control signal input. F is used to identify field information for the output multiplexer.                                                                                                                                                    |

| 26                                                                                            | CS                       | Chip Select: Host interface control signal input.                                                                                                                                                                                                   |

| 23                                                                                            | R/W                      | Read/Write: Host interface control signal input.                                                                                                                                                                                                    |

| 27-31                                                                                         | ADDR <sub>40</sub>       | Coefficient Address: Input port to identify which GF9105A device address shall be written to/read from.                                                                                                                                             |

| 3, 5, 6, 8, 9, 12, 13,<br>15                                                                  | COEFF_PORT <sub>70</sub> | Coefficient Port: Host interface bi-directional data port for Color Space Converter coefficients, KEY scaler coefficient and device configuration words.                                                                                            |

| 19                                                                                            | CLK                      | System Clock: All timing information is relative to the rising edge of CLK.                                                                                                                                                                         |

| 32                                                                                            | TCK                      | JTAG Test Clock Input: Independent clock signal for JTAG.                                                                                                                                                                                           |

## **PIN DESCRIPTION**

| PIN NO. | SYMBOL | DESCRIPTION                                                       |

|---------|--------|-------------------------------------------------------------------|

| 33      | TDI    | JTAG Test Data Input: Serial input for JTAG test data.            |

| 34      | TMS    | JTAG Test Mode Select: Serial input for selecting JTAG test mode. |

| 35      | TRST   | JTAG Test Reset: Connect to GND for normal operation.             |

| 36      | TDO    | JTAG Test Data Output: Serial output for JTAG test data.          |

| 37      | TN_IN  | Connect to V <sub>DD</sub> .                                      |

| 38      | PTO    | No Connect.                                                       |

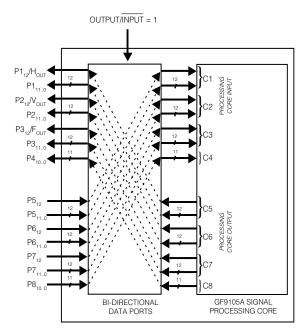

Fig. 1 GF9105A Data Pin Designations

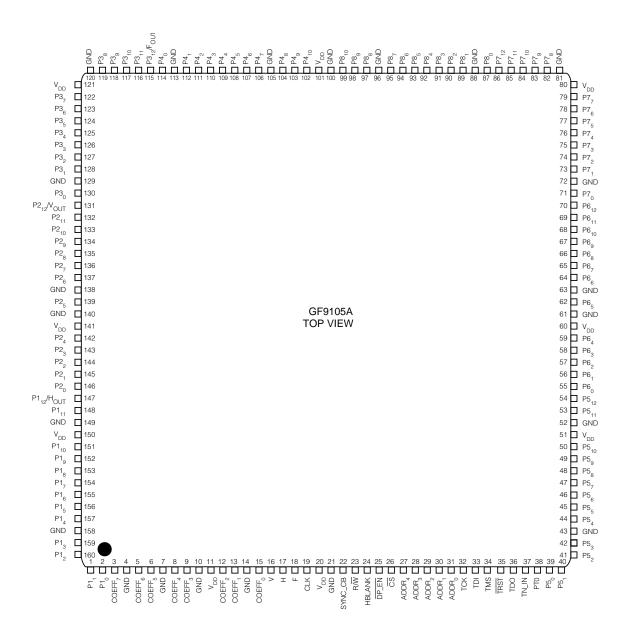

Fig. 2 GF9105A Pin Connections

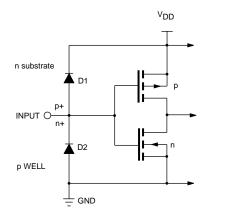

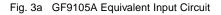

Fig. 3b GF9105A Equivalent Output Circuit

521 - 88 - 03 4

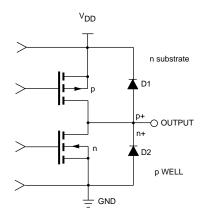

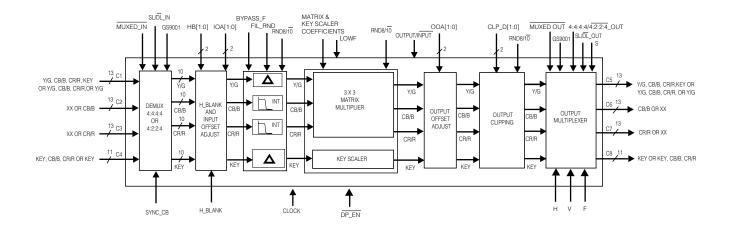

Fig. 4a Functional Block Diagram of GF9105A (OUTPUT/INPUT = 0, HVF\_OUT = 0)

Fig. 4b Functional Block Diagram of GF9105A (OUTPUT/INPUT = 1, HVF\_OUT = 0)

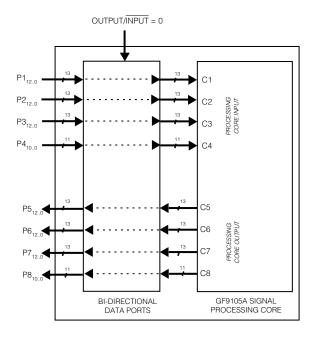

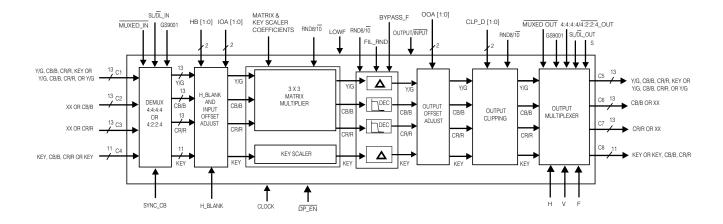

Fig. 4c Functional Block Diagram of GF9105A (OUTPUT/INPUT = 0, HVF\_OUT = 1)

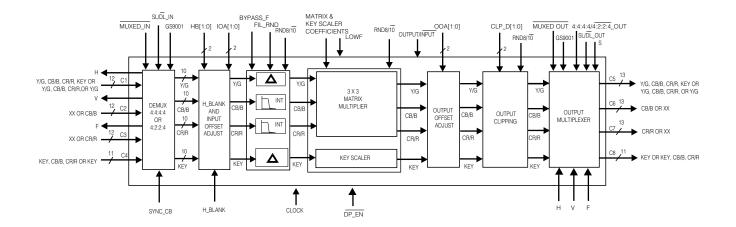

Fig. 4d Functional Block Diagram of GF9105A (OUTPUT/INPUT = 1, HVF\_OUT = 1)

Fig. 5a Functionality of GF9105A Processing Core when  $INT/\overline{DEC} = 1$ ,  $HVF\_OUT = 0$

Fig. 5b Functionality of GF9105A Processing Core when INT/DEC = 0, HVF\_OUT = 0

Fig. 5c Functionality of GF9105A Processing Core when INT/ $\overline{DEC}$  = 1, HVF\_OUT = 1

Fig. 5d Functionality of GF9105A Processing Core when INT/DEC = 0, HVF\_OUT = 1

#### **GF9105A DETAILED DEVICE DESCRIPTION**

#### **INPUT/OUTPUT DATA PORTS**

The GF9105A has 8 bi-directional data ports, labelled P1 to P8. P1 to P3 and P5 to P7 are 13-bit data ports while P4 and P8 are 11-bit data ports. The OUTPUT/INPUT control bit and the HVF\_OUT control bit (See Host Programming Section and figures 4a - 4d) control how P1 to P8 are configured.

When OUTPUT/INPUT is set low and when HVF\_OUT is set low, P1<sub>12..0</sub>, P2<sub>12..0</sub>, P3<sub>12..0</sub>, P4<sub>10..0</sub> are configured as input video data ports and P5<sub>12..0</sub>, P6<sub>12..0</sub>, P6<sub>12..0</sub>, P8<sub>10..0</sub> are configured as output video data ports (refer to Figure 4a).

When OUTPUT/ $\overline{\text{INPUT}}$  is set low and when HVF\_OUT is set high, P1<sub>11..0</sub>, P2<sub>11..0</sub>, P3<sub>11..0</sub>, P4<sub>10..0</sub> are configured as input video data ports and P5<sub>12..0</sub>, P6<sub>12..0</sub>, P7<sub>12..0</sub>, P8<sub>10..0</sub> are configured as output video data ports. In this mode, P1<sub>12</sub>, P2<sub>12</sub>, P3<sub>12</sub> are configured as outputs for H, V, and F output data. P1<sub>12</sub> carries H data, P2<sub>12</sub> carries V data and P3<sub>12</sub> carries F data (refer to Figure 4c).

When OUTPUT/INPUT is set high and when HVF\_OUT is set low, P1<sub>12..0</sub>, P2<sub>12..0</sub>, P3<sub>12..0</sub>, P4<sub>10..0</sub> are configured as output video data ports and P5<sub>12..0</sub>, P6<sub>12..0</sub>, P7<sub>12..0</sub>, P8<sub>10..0</sub> are configured as input video data ports (refer to Figure 4b).

When OUTPUT/ $\overline{\text{INPUT}}$  is set high and when HVF\_OUT is set high, P1<sub>11..0</sub>, P2<sub>11..0</sub>, P3<sub>11..0</sub>, P4<sub>10..0</sub> are configured as output video data ports and P5<sub>12..0</sub>, P6<sub>12..0</sub>, P7<sub>12..0</sub>, P8<sub>10..0</sub> are configured as input video data ports. In this mode, P1<sub>12</sub>, P2<sub>12</sub>, P3<sub>12</sub> are configured as outputs for HVF output data. P1<sub>12</sub> carries H data, P2<sub>12</sub> carries V data and P3<sub>12</sub> carries F data (refer to Figure 4d).

Note: No bi-directional I/Os should be driven until after the OUTPUT/INPUT and the HVF\_OUT control bits have been set (unless DP\_EN is set high to tri-state the outputs). This will ensure that any potential conflicts between input and output data buses are avoided.

## OUTPUT/INPUT AND HVF CONTROL BIT

| OUTPUT/INPUT | HVF_OUT | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                     |

|--------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0            | 0       | P1 <sub>120</sub> , P2 <sub>120</sub> , P3 <sub>120</sub> , P4 <sub>100</sub> are configured as input video data ports. P5 <sub>120</sub> , P6 <sub>120</sub> , P7 <sub>120</sub> , P8 <sub>100</sub> are configured as output video data ports. Refer to Figure 4a.                                                                                                            |

| 0            | 1       | P1 <sub>110</sub> , P2 <sub>110</sub> , P3 <sub>110</sub> , P4 <sub>100</sub> are configured as input video data ports. P1 <sub>12</sub> , P2 <sub>12</sub> , P3 <sub>12</sub> are configured as H, V and F outputs, respectively. P5 <sub>120</sub> , P6 <sub>120</sub> , P7 <sub>120</sub> , P8 <sub>100</sub> are configured as output video data ports. Refer to Figure 4c. |

| 1            | 0       | P1 <sub>120</sub> , P2 <sub>120</sub> , P3 <sub>120</sub> , P4 <sub>100</sub> are configured as output video data ports. P5 <sub>120</sub> , P6 <sub>120</sub> , P7 <sub>120</sub> , P8 <sub>100</sub> are configured as input video data ports. Refer to Figure 4b.                                                                                                            |

| 1            | 1       | P1 <sub>110</sub> , P2 <sub>110</sub> , P3 <sub>110</sub> , P4 <sub>100</sub> are configured as output video data ports. P1 <sub>12</sub> , P2 <sub>12</sub> , P3 <sub>12</sub> are configured as H, V and F outputs, respectively. P5 <sub>120</sub> , P6 <sub>120</sub> , P7 <sub>120</sub> , P8 <sub>100</sub> are configured as input video data ports. Refer to Figure 4d. |

For H, V, F output timing refer to the Timing Reference Signal Section of this data sheet.

#### **DATA PORT ENABLE**

DP\_EN is used for synchronously enabling and disabling the bi-directional data ports of the GF9105A. When DP\_EN is set high, the data ports are disabled and set to a high impedance state. When DP\_EN is set low, all data ports are enabled.

## **DP\_EN CONTROL PIN**

| DP_EN | DESCRIPTION                                        |  |  |  |  |  |

|-------|----------------------------------------------------|--|--|--|--|--|

| 0     | Output data ports enabled.                         |  |  |  |  |  |

| 1     | Output data ports disabled (high impedance state). |  |  |  |  |  |

#### INPUT CLOCK (CLK)

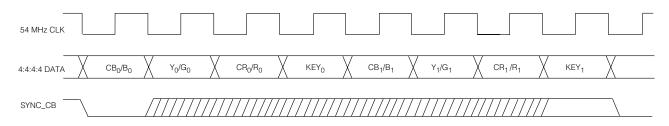

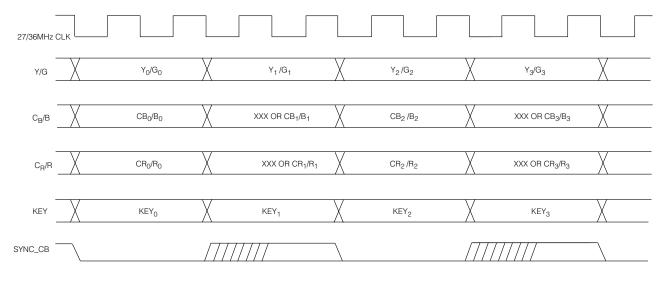

For standard video signals, the clock input (CLK) of the GF9105A runs at one of three rates: 13.5/18MHz, 27/36MHz or 54MHz. The 18 MHz and 36 MHz variations on main clock frequencies are used in 16 x 9 video applications where luminance is sampled at 18 MHz. The use of a 27/36MHz clock with the GF9105A is the most common application. These clocks can be used with any format of input or output data with the exception of single link mode. Figures 7a and 7c show multiplexed and non-multiplexed input data with a 27/36MHz clock. When the GF9105A is used with either SMPTE RP174 compliant single link input or output data, the input clock must run at 54 MHz (see Figure 7b).

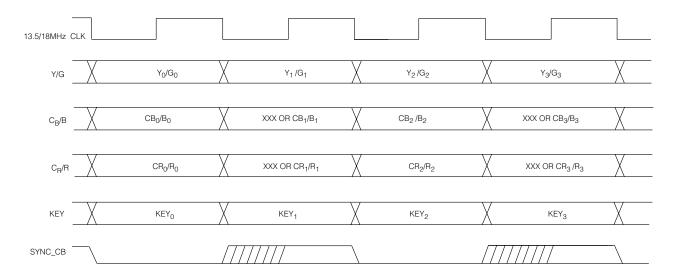

A 13.5/18 MHz input clock speed can only be used when both the input and output data are in a non multiplexed format (see Figure 7d). This clock rate was added to the GF9105A for use when the device is operating with non-multiplexed input and output data, since in this case a 27.0MHz clock may not be available. To use the 13.5 MHz input clock rate, the LOWF control bit must be set HIGH. When input clock rates of 27.0 MHz or 54.0 MHz are used, the LOWF control bit must be set LOW. Please note, when using the GF9105A with non-multiplexed 4:2:2:4 or 4:4:4:4 input data and an input clock rate of 27/36MHz, two rising edges of the 27/36MHz input clock are required to latch in a 13.5/18MHz input data rate (see Figure 7c).

| INPUT CLOCK SUMMARY    |                                                                           |  |  |  |  |  |  |  |

|------------------------|---------------------------------------------------------------------------|--|--|--|--|--|--|--|

| INPUT CLOCK RATE (MHz) | MODES                                                                     |  |  |  |  |  |  |  |

| 13.5/18 MHz            | Non-multiplexed Input Data<br>AND<br>Non-multiplexed Output Data (LOWF=1) |  |  |  |  |  |  |  |

| 27/36 MHz              | All Input / Output Data Formats<br>EXCEPT Single Link                     |  |  |  |  |  |  |  |

| 54 MHz                 | SMPTE RP174 Single Link Input<br>OR Output Data                           |  |  |  |  |  |  |  |

#### **BASIC OPERATION OF THE GF9105A**

The basic operating mode for the GF9105A is selected via the INT/DEC control bit (See Host Programming Section). The effective block diagram of the GF9105A Processing Core depends on the state of INT/DEC. When INT/DEC is set high, the internal FIR filters are set for interpolation and are placed in front of the programmable 3X3 color space converter. Refer to Figures 5a and 5c for a functional block diagram of the GF9105A processing core when INT/DEC is set high. When INT/DEC is set low, the internal FIR filters are set for decimation and are placed after the programmable 3X3 color space converter. Refer to Figures 5b and 5d for a functional block diagram of the GF9105A with INT/DEC set low. In these figures, static control bits (signals loaded via the asynchronous parallel interface) are shown at the top of the diagram and control signals with dedicated input pins are shown at the bottom of the diagram.

#### INT/DEC CONTROL BIT

| INT/DEC | DESCRIPTION                                                                                             |

|---------|---------------------------------------------------------------------------------------------------------|

| 0       | FIR filters set for decimation. FIR filters placed after the 3X3 multiplier as in Figure 5b and 5d.     |

| 1       | FIR filters set for interpolation. FIR filters placed before the 3x3 multiplier as in Figure 5a and 5c. |

There are seven basic blocks that make up the GF9105A. These are:

- Input De-multiplexer

- Horizontal Blanking and Input Offset Adjustment

- FIR Filters

- 3x3 Color Space Converter and KEY Scaler

- · Output Offset Adjustment

- Output Clipping

- Output Multiplexer

Since the GF9105A Processing Core functionality depends on the state of INT/DEC, device operation will be described first for the case where INT/DEC is set high and then for the case where INT/DEC is set low.

## GF9105A OPERATION IN INTERPOLATION MODE (INT/ $\overline{DEC} = 1$ )

Refer to Figures 5a and 5c for a functional block diagram of GF9105A operation with INT/DEC = 1

#### **BIT WEIGHTING**

Although the input data ports are physically 13 bits or 11 bits wide, the GF9105A Processing Core is limited to processing 10 or 8-bit unsigned input data while INT/DEC is set high. It should be noted that while INT/DEC is set low, the GF9105A Processing Core will accept up to 13 bit input data. Refer to later sections for a description of Processing Core functionality while INT/DEC is set low.

As mentioned above, the GF9105A is limited to processing 10 or 8-bit unsigned input data while  $INT/\overline{DEC}$  is set high. This input data must be properly embedded within the input data ports. The following table illustrates how to properly embed 10 or 8-bit data within the 13 bit data ports. Note that when  $OUTPUT/\overline{INPUT}=0$  and  $HVF_OUT=1$ ,  $P1_{12}$ ,  $P2_{12}$  and  $P3_{12}$  (which corresponds to  $b_{12}$ ) are outputs rather than inputs. These 3 outputs are used for presenting output H, V and F output signals. The user should be careful to ensure that  $P1_{12}$ ,  $P2_{12}$  and  $P3_{12}$ , are not driven by upstream logic when  $OUTPUT/\overline{INPUT}=0$  and  $HVF_OUT=1$ . Other unused inputs should be set low by the user.

| OUTPUT/INPUT = 0, HVF_OUT = 0                                               | 13 BIT PHYSICAL INTERFACE |                 |                 |                |                |                |                |                |                |                |                |                |                |

|-----------------------------------------------------------------------------|---------------------------|-----------------|-----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|

| DATA PORT REFERENCE                                                         | b <sub>12</sub>           | b <sub>11</sub> | b <sub>10</sub> | b <sub>9</sub> | b <sub>8</sub> | b <sub>7</sub> | b <sub>6</sub> | b <sub>5</sub> | b <sub>4</sub> | b <sub>3</sub> | b <sub>2</sub> | b <sub>1</sub> | b <sub>0</sub> |

| Input Port: P1 <sub>120</sub> to P3 <sub>120</sub> Embedded 10 bit signal   | 0                         | 0               | 0               | b <sub>9</sub> | b <sub>8</sub> | b <sub>7</sub> | b <sub>6</sub> | b <sub>5</sub> | b <sub>4</sub> | b <sub>3</sub> | b <sub>2</sub> | b <sub>1</sub> | b <sub>0</sub> |

| Input Port: P4 <sub>100</sub><br>Embedded 10 bit signal                     | NA                        | NA              | 0               | b <sub>9</sub> | b <sub>8</sub> | b <sub>7</sub> | b <sub>6</sub> | b <sub>5</sub> | b <sub>4</sub> | b <sub>3</sub> | b <sub>2</sub> | b <sub>1</sub> | b <sub>0</sub> |

| Input Port: P1 <sub>120</sub> to P3 <sub>120</sub><br>Embedded 8 bit signal | 0                         | 0               | 0               | b <sub>7</sub> | b <sub>6</sub> | b <sub>5</sub> | b <sub>4</sub> | b <sub>3</sub> | b <sub>2</sub> | b <sub>1</sub> | b <sub>0</sub> | 0              | 0              |

| Input Port: P4 <sub>100</sub><br>Embedded 8 bit signal                      | NA                        | NA              | 0               | b <sub>7</sub> | b <sub>6</sub> | b <sub>5</sub> | b <sub>4</sub> | b <sub>3</sub> | b <sub>2</sub> | b <sub>1</sub> | b <sub>0</sub> | 0              | 0              |

## INPUT DE-MULTIPLEXER

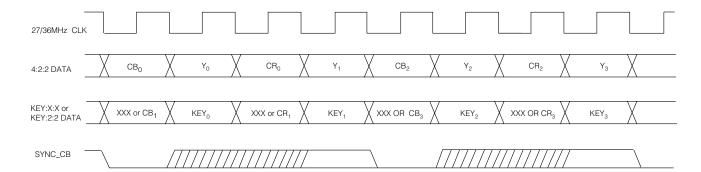

The MUXED\_IN and SL/DL\_IN control bits (See Host Programming Section) determine the input data format. The MUXED\_IN control bit is used to identify whether the incoming data is in a multiplexed or non-multiplexed format. The SL/DL\_IN control bit is used to identify whether the incoming data is in a single link or dual link format.

## Dual Link ( $SL/\overline{DL}_{IN} = 0$ )

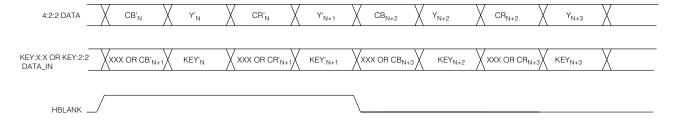

While  $\overline{\text{MUXED_IN}}$  is set low, input data is assumed to be two 10 bit streams in 4:2:2:4 or 4:4:4:4 data format as shown in Figure 7a. The input de-multiplexer separates the 4:2:2:4 or 4:4:4:4 input signals into four channels of Y/G,  $C_B/B$ ,  $C_R/R$  and KEY data. These four data streams are then passed to the next processing section.

When operating with multiplexed 4:2:2:4 or 4:4:4:4 input data, the 4:2:2 data stream enters the GF9105A Processing Core from Processing Core input port C1. While OUTPUT/INPUT=0 Processing Core port C1 corresponds to device data port P1

| OUTPUT/INPUT = 0, HVF_OUT = 1                                             | 13 BIT PHYSICAL INTERFACE |                 |                 |                |                |                |                |                |                |                |                |                |                |

|---------------------------------------------------------------------------|---------------------------|-----------------|-----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|

| DATA PORT REFERENCE                                                       | b <sub>12</sub>           | b <sub>11</sub> | b <sub>10</sub> | b <sub>9</sub> | b <sub>8</sub> | b <sub>7</sub> | b <sub>6</sub> | b <sub>5</sub> | b <sub>4</sub> | b <sub>3</sub> | b <sub>2</sub> | b <sub>1</sub> | b <sub>0</sub> |

| Input Port: P1 <sub>120</sub> to P3 <sub>120</sub> Embedded 10 bit signal | H, V, or F<br>output      | 0               | 0               | b <sub>9</sub> | b <sub>8</sub> | b <sub>7</sub> | b <sub>6</sub> | b <sub>5</sub> | b <sub>4</sub> | b <sub>3</sub> | b <sub>2</sub> | b <sub>1</sub> | b <sub>0</sub> |

| Input Port: P4 <sub>100</sub><br>Embedded 10 bit signal                   | NA                        | NA              | 0               | b <sub>9</sub> | b <sub>8</sub> | b <sub>7</sub> | b <sub>6</sub> | b <sub>5</sub> | b <sub>4</sub> | b <sub>3</sub> | b <sub>2</sub> | b <sub>1</sub> | b <sub>0</sub> |

| Input Port: P1 <sub>120</sub> to P3 <sub>120</sub> Embedded 8 bit signal  | H, V, or F<br>output      | 0               | 0               | b <sub>7</sub> | b <sub>6</sub> | b <sub>5</sub> | b <sub>4</sub> | b <sub>3</sub> | b <sub>2</sub> | b <sub>1</sub> | b <sub>0</sub> | 0              | 0              |

| Input Port: P4 <sub>100</sub> Embedded 8 bit signal                       | NA                        | NA              | 0               | b <sub>7</sub> | b <sub>6</sub> | b <sub>5</sub> | b <sub>4</sub> | b <sub>3</sub> | b <sub>2</sub> | b <sub>1</sub> | b <sub>0</sub> | 0              | 0              |

| OUTPUT/INPUT = 1, HVF_OUT = 0                                                | 13 BIT PHYSICAL INTERFACE |                 |                 |                |                |                |                |                |                |                |                |                |                |

|------------------------------------------------------------------------------|---------------------------|-----------------|-----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|

| DATA PORT REFERENCE                                                          | b <sub>12</sub>           | b <sub>11</sub> | b <sub>10</sub> | b <sub>9</sub> | b <sub>8</sub> | b <sub>7</sub> | b <sub>6</sub> | b <sub>5</sub> | b <sub>4</sub> | b <sub>3</sub> | b <sub>2</sub> | b <sub>1</sub> | b <sub>0</sub> |

| Input Port: P5 <sub>120</sub> to P7 <sub>120</sub><br>Embedded 10 bit signal | 0                         | 0               | 0               | b <sub>9</sub> | b <sub>8</sub> | b <sub>7</sub> | b <sub>6</sub> | b <sub>5</sub> | b <sub>4</sub> | b <sub>3</sub> | b <sub>2</sub> | b <sub>1</sub> | b <sub>0</sub> |

| Input Port: P8 <sub>100</sub><br>Embedded 10 bit signal                      | NA                        | NA              | 0               | b <sub>9</sub> | b <sub>8</sub> | b <sub>7</sub> | b <sub>6</sub> | b <sub>5</sub> | b <sub>4</sub> | b <sub>3</sub> | b <sub>2</sub> | b <sub>1</sub> | b <sub>0</sub> |

| Input Port: P5 <sub>120</sub> to P7 <sub>120</sub><br>Embedded 8 bit signal  | 0                         | 0               | 0               | b <sub>7</sub> | b <sub>6</sub> | b <sub>5</sub> | b <sub>4</sub> | b <sub>3</sub> | b <sub>2</sub> | b <sub>1</sub> | b <sub>0</sub> | 0              | 0              |

| Input Port: P8 <sub>100</sub><br>Embedded 8 bit signal                       | NA                        | NA              | 0               | b <sub>7</sub> | b <sub>6</sub> | b <sub>5</sub> | b <sub>4</sub> | b <sub>3</sub> | b <sub>2</sub> | b <sub>1</sub> | b <sub>0</sub> | 0              | 0              |

| OUTPUT/INPUT = 1, HVF_OUT = 1                                                | 13 BIT PHYSICAL INTERFACE |                 |                 |                |                |                |                |                |                |                |                |                |                |

|------------------------------------------------------------------------------|---------------------------|-----------------|-----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|

| DATA PORT REFERENCE                                                          | b <sub>12</sub>           | b <sub>11</sub> | b <sub>10</sub> | b <sub>9</sub> | b <sub>8</sub> | b <sub>7</sub> | b <sub>6</sub> | b <sub>5</sub> | b <sub>4</sub> | b <sub>3</sub> | b <sub>2</sub> | b <sub>1</sub> | b <sub>0</sub> |

| Input Port: P5 <sub>120</sub> to P7 <sub>120</sub><br>Embedded 10 bit signal | 0                         | 0               | 0               | b <sub>9</sub> | b <sub>8</sub> | b <sub>7</sub> | b <sub>6</sub> | b <sub>5</sub> | b <sub>4</sub> | b <sub>3</sub> | b <sub>2</sub> | b <sub>1</sub> | b <sub>0</sub> |

| Input Port: P8 <sub>100</sub><br>Embedded 10 bit signal                      | NA                        | NA              | 0               | b <sub>9</sub> | b <sub>8</sub> | b <sub>7</sub> | b <sub>6</sub> | b <sub>5</sub> | b <sub>4</sub> | b <sub>3</sub> | b <sub>2</sub> | b <sub>1</sub> | b <sub>0</sub> |

| Input Port: P5 <sub>120</sub> to P7 <sub>120</sub><br>Embedded 8 bit signal  | 0                         | 0               | 0               | b <sub>7</sub> | b <sub>6</sub> | b <sub>5</sub> | b <sub>4</sub> | b <sub>3</sub> | b <sub>2</sub> | b <sub>1</sub> | b <sub>0</sub> | 0              | 0              |

| Input Port: P8 <sub>100</sub><br>Embedded 8 bit signal                       | NA                        | NA              | 0               | b <sub>7</sub> | b <sub>6</sub> | b <sub>5</sub> | b <sub>4</sub> | b <sub>3</sub> | b <sub>2</sub> | b <sub>1</sub> | b <sub>0</sub> | 0              | 0              |

(refer to Figures 4a and 4c). While OUTPUT/INPUT=1 Processing Core port C1 corresponds to device data port P5 (Refer to Figures 4b and 4d).

The KEY:2:2 or KEY:XX:XX data enters the GF9105A Processing Core from Processing Core input port C4. While OUTPUT/ INPUT=0, Processing Core port C4 corresponds to device data port P4 (Refer to Figures 4a and 4c). While OUTPUT/ INPUT=1, Processing Core port C4 corresponds to device data port P8 (Refer to Figures 4b and 4d).

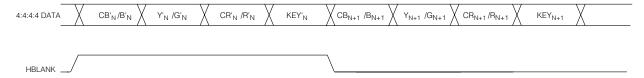

When MUXED\_IN is set high, input data is assumed to be 4:2:2:4 or 4:4:4:4 data in a non-multiplexed format as shown in Figure 7c. Since the incoming data is already non-multiplexed, the input data is passed on to the next processing section unmodified. In this mode of operation, input data is presented to all four Processing Core input ports. While OUTPUT/INPUT=0, Processing Core ports C1-C4 correspond to device data ports P1-P4 (Refer to Figures 4a and 4c). While OUTPUT/INPUT=1 Processing Core ports C1-C4 correspond to device data ports P5-P8 (Refer to Figure 4b and 4d).

# Single Link (SL/DL\_IN = 1)

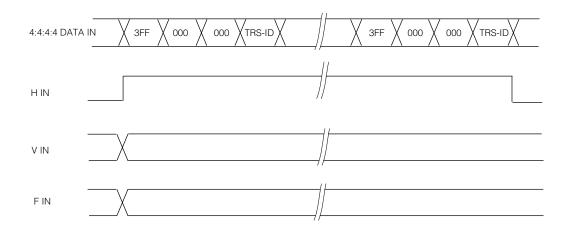

When operating with single link input data, the 4:4:4:4 data stream (SMPTE RP174 compliant) enters the GF9105A Processing Core from Processing Core input C1.

While OUTPUT/INPUT = 0 Processing Core Port C1 corresponds to device data port P1 (refer to Figures 4a and 4c). While OUTPUT/INPUT = 1 Processing Core Port C1 corresponds to device data port P5 (refer to Figures 4b and 4d). In this mode, the input clock (CLK) is operating at 54 MHz. Also, note that the MUXED\_IN control bit must be set low (MUXED\_IN = 0).

# MUXED IN AND SL/DL IN CONTROL BITS

| MUXED_IN | SL/DL_IN | DESCRIPTION                                   |

|----------|----------|-----------------------------------------------|

| 0        | 0        | Input is in a dual link multiplexed format.   |

| 0        | 1        | Input is in a single link multiplexed format. |

| 1        | XX       | Input is in a non-multiplexed format.         |

#### **SYNCHRONIZATION**

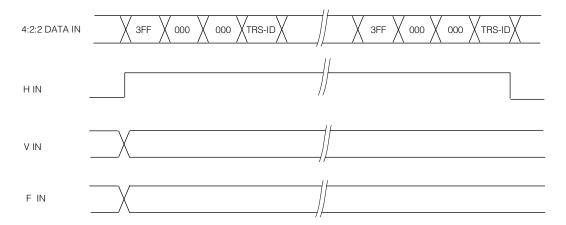

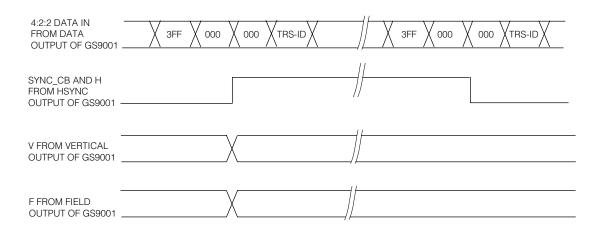

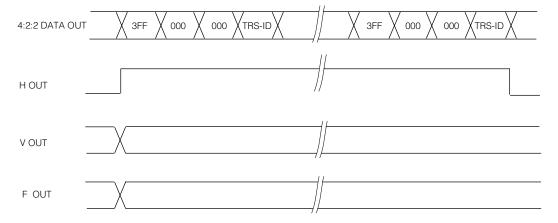

In order to properly synchronize the input de-multiplexer, the GF9105A requires a SYNC\_CB control signal input. For multiplexed input data, SYNC\_CB should change from high to low at the start of an even numbered CB sample. After synchronizing the device with the incoming data stream, SYNC\_CB can remain low until re-synchronization is desired. Refer to Figure 7a for timing of SYNC\_CB with a dual link multiplexed input data stream. Refer to Figure 7b for timing of SYNC\_CB with a single link multiplexed input data signal. The timing shown may be referred to as "standard SYNC\_CB timing".

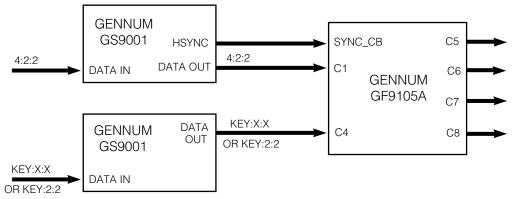

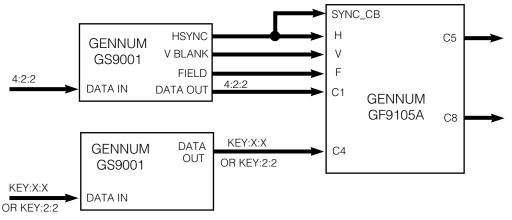

In order to simplify overall system design, the HSYNC output from the GS9001 EDH Coprocessor may be used as a SYNC\_CB signal when operated with a 4:2:2 or dual link 4:4:4:4 input signal. In this mode of operation, the 10 bit multiplexed data entering the GF9105A must be fed from the output of the GS9001 and the GF9105A's SYNC\_CB input must be fed from the GS9001's HSYNC output (Refer to Figure 8a). To use this mode of operation the GF9105A's GS9001 control bit (*Refer to Host Programming Section*) must be set high. When operated with a 4:2:2 or a dual link 4:4:4:4 input signal and when the GS9001 control bit is set high, the GS9001's HSYNC, VSYNC, and FIELD output signals may also be used to drive the GS9105A's output multiplexer. Refer to the Timing Reference Signal section for information regarding this.

When dealing with single link 4:4:4:4 input or output signals "standard" SYNC\_CB timing above must be used. When using standard SYNC\_CB and HVF timing, the GS9001 control must be set low. The GS9020 may be used to provide such standard SYNC\_CB timing and HVF. When operated in this manner, the 10 bit multiplexed data entering the GF9105A must be fed from the output of the GS9020 and the GF9105A's SYNC\_CB and HVF inputs must be fed from the GS9020's H, V, F outputs. The same GS9020/GF9105A configuration may also be used when interfacing the GF9105A to a standard 4:2:2 or dual link 4:4:4:4 link input signal. In this case, the GS9001 control bit must still be set low.

#### **GS9001 CONTROL BIT**

| GS9001 | DESCRIPTION                                                      |

|--------|------------------------------------------------------------------|

| 0      | Standard SYNC_CB and H,V,F timing. Simple interface to GS9020.   |

| 1      | Modified SYNC_CB and H, V, F timing. Simple interface to GS9001. |

NOTE: Standard SYNC\_CB and H, V, F timing must be used when receiving or generating single link 4:4:4:4 signals.

With non-multiplexed input data, SYNC\_CB must change from high to low at the start of an even-numbered CB sample. It is important to note that SYNC\_CB changes from high to low on an even-numbered CB sample and not an odd-numbered sample. After synchronizing the device with the incoming data stream, the SYNC\_CB signal can remain low until resynchronization is desired. Refer to Figure 7c for timing of SYNC\_CB with non-multiplexed input data. Following the input demultiplexer, data is passed to the Horizontal Blanking section of the device.

#### HORIZONTAL BLANKING

When H\_BLANK is high, all four channels of input are forced to a user selectable set of levels. When H\_BLANK is low data is passed through the Horizontal Blanking section of the device unmodified. Refer to Figures 10a and 10b for typical timing of H\_BLANK with multiplexed input data and Figure 10c for typical timing with non-multiplexed input data. In these figures, a

prime (') indicates to which samples the H blanking will be applied. The HB<sub>1</sub> and HB<sub>0</sub> control bits (See Host Programming Section) determine which of the four sets of blanking levels are selected.

#### HB1 AND HB0 CONTROL BITS

| HB <sub>1</sub> | HB <sub>0</sub> | DESCRIPTION                                                                                                                |

|-----------------|-----------------|----------------------------------------------------------------------------------------------------------------------------|

| 0               | 0               | Blanking levels of 64, 512, 512 and 64 applied to Y/G, C <sub>B</sub> /B, C <sub>R</sub> /R and KEY channels respectively. |

| 0               | 1               | Blanking levels of 64, 64, 64 and 64 applied to Y/G, C <sub>B</sub> /B, C <sub>R</sub> /R and KEY channels respectively.   |

| 1               | 0               | Blanking levels of 0, 0, 0 and 0 applied to Y/G, C <sub>B</sub> /B, C <sub>R</sub> /R and KEY channels respectively.       |

| 1               | 1               | Blanking levels of 0, 512, 512 and 0 applied to Y/G, C <sub>B</sub> /B, C <sub>R</sub> /R and KEY channels respectively.   |

#### INPUT OFFSET ADJUSTMENT

Following the Horizontal Blanking function, a fixed set of offsets may be added to the input data. The  $IOA_1$  and  $IOA_0$  control bits (See Host Programming Section) specify which of the four possible input offset adjustments will be applied to the data. As an example, the interpolation/decimation filters operate on two's complement data, so for  $Y/C_B/C_R$  input,  $IOA_1$  and  $IOA_0$  should both be set low to remove the inherent offset from the incoming data.

## IOA<sub>1</sub> AND IOA<sub>0</sub> CONTROL BITS

| IOA <sub>1</sub> | IOA <sub>0</sub> | DESCRIPTION                                                                                                              |

|------------------|------------------|--------------------------------------------------------------------------------------------------------------------------|

| 0                | 0                | Offsets of -64, -512, -512 and -64 added to the Y/G, C <sub>B</sub> /B, C <sub>R</sub> /R and KEY channels respectively. |

| 0                | 1                | Offsets of -64, -64, -64 and -64 added to the Y/G, C <sub>B</sub> /B, C <sub>R</sub> /R and KEY channels respectively.   |

| 1                | 0                | Offsets of 0, 0, 0 and 0 added to the Y/G, C <sub>B</sub> /B, C <sub>R</sub> /R and KEY channels respectively.           |

| 1                | 1                | Offsets of 0, -512, -512 and 0 added to the Y/G, C <sub>B</sub> /B, C <sub>R</sub> /R and KEY channels respectively.     |

#### **FIR FILTERS**

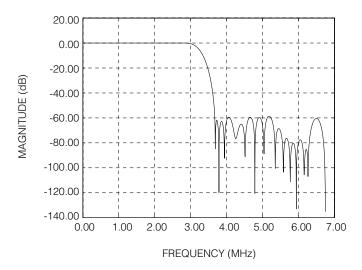

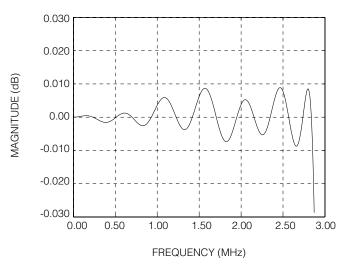

Following the Input Offset Adjustment, data is passed to the FIR filtering section of the device. These filters, when enabled, will up-sample  $C_B$  and  $C_R$  data by a factor of two so that 4:2:2:4 data is sample-rate converted to 4:4:4:4 data. Subsequent processing of co-sited Y,  $C_B$  and  $C_R$  samples may take place on such 4:4:4:4 data. The frequency response of these CCIR-601 compliant FIR filters is shown in Figures 6a and 6b and the characteristics are listed in Figure 6c. In order to maintain proper synchronization between all four channels of input data, the Y/G and KEY channels are passed through a digital delay line that matches the FIR filter latency. Output resolution from the FIR filters depends on the state of the RND8/ $\overline{10}$  and FIL\_RND control bits (See Host Programming Section). RND8/ $\overline{10}$  should always be set to match the data format being output by the device (high for 8 bit data or low for 10 bit data). FIL\_RND should be set low unless the GF9105A is being used in a mode where the 3X3 matrix is set for unity gain bypass mode. (See 3X3 Color Space Converter and KEY Scaler Section). In this case, FIL\_RND should be set high. The FIR filter only takes 10-bit input in interpolation mode and proper input offset has to be used.

## RND8/10 AND FIL RND CONTROL BITS

| RND8/10 | FIL_RND | DESCRIPTION                                                                                                     |

|---------|---------|-----------------------------------------------------------------------------------------------------------------|

| 0       | 0       | Output has minimum rounding for high accuracy for a non-identity matrix, using 10-bit input data.               |

| 0       | 1       | More rounding is performed to increase overall accuracy when matrix is being bypassed, using 10-bit input data. |

| 1       | 0       | Output has minimum rounding for high accuracy for a non-identity matrix, using 8-bit input data.                |

| 1       | 1       | More rounding is performed to increase overall accuracy when matrix is being bypassed, using 8-bit input data.  |

The BYPASS\_F control bit (See Host Programming Section) can be used to bypass the interpolation filters. When this bit is set low, the filters are enabled and normal operation occurs. When this bit is set high, the filters are bypassed and the data is passed through the filter section unmodified. FIL\_RND should be set low when BYPASS\_F is set high. Total latency through the filter is independent of the BYPASS\_F control signal. Note that after changing the state of BYPASS\_F, an initialization period corresponding to the device's latency is required before valid data is available at the output of the device.

#### BYPASS\_F CONTROL BIT

| BYPASS_F | DESCRIPTION                                                                      |

|----------|----------------------------------------------------------------------------------|

| 0        | Filters are enabled. Data is sample-rate converted from 4:2:2:4 to 4:4:4:4 data. |

| 1        | Filters are disabled. Data is passed through the filter section unmodified.      |

#### 3X3 COLOR SPACE CONVERTER AND KEY SCALER

In this section, a 3X3 matrix multiplication (color space conversion) may be performed on the Y/G,  $C_B/B$  and  $C_R/R$  data. The 3X3 matrix multiplier has 13-bit two's complement coefficients and maintains full precision throughout the 3X3 calculation. The nine 13-bit coefficients (*See Host Programming Section*) used in this 3X3 calculation determine the color space conversion that the GF9105A will perform. These coefficients are referred to as  $CM_{ij}$ , where i refers to the row and j refers to the column in which  $CM_{ii}$  is found. The matrix multiplication can be shown as:

$$\begin{bmatrix} \text{Y/G}_{\text{OUT}} \\ \text{C}_{\text{B}}/\text{B}_{\text{OUT}} \\ \text{C}_{\text{R}}/\text{R}_{\text{OUT}} \end{bmatrix} = \begin{bmatrix} \text{CM}_{11} & \text{CM}_{12} & \text{CM}_{13} \\ \text{CM}_{21} & \text{CM}_{22} & \text{CM}_{23} \\ \text{CM}_{31} & \text{CM}_{32} & \text{CM}_{33} \end{bmatrix} \begin{bmatrix} \text{Y/G}_{\text{IN}} \\ \text{C}_{\text{B}}/\text{B}_{\text{IN}} \\ \text{C}_{\text{R}}/\text{R}_{\text{IN}} \end{bmatrix}$$

The nine matrix coefficients have 13-bit two's complement resolution and cover a range from -4 to +3.9990234375. Bit weighting for the coefficients is as follows:

| Coefficient Bit | b <sub>12</sub> | b <sub>11</sub> | b <sub>10</sub> | b <sub>9</sub>  | b <sub>8</sub>  | b <sub>7</sub>  | b <sub>6</sub>  | b <sub>5</sub>  | b <sub>4</sub>  | b <sub>3</sub>  | b <sub>2</sub>  | b <sub>1</sub>  | b <sub>0</sub>   |

|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|------------------|

| Weighting       | -2 <sup>2</sup> | 2 <sup>1</sup>  | 2 <sup>0</sup>  | 2 <sup>-1</sup> | 2 <sup>-2</sup> | 2 <sup>-3</sup> | 2 <sup>-4</sup> | 2 <sup>-5</sup> | 2 <sup>-6</sup> | 2 <sup>-7</sup> | 2 <sup>-8</sup> | 2 <sup>-9</sup> | 2 <sup>-10</sup> |

Matrix bypassing can be accomplished by setting FIL\_RND high and loading an identity matrix, by setting  $CM_{11}$ ,  $CM_{22}$  and  $CM_{33}$  to unity and setting the remaining six coefficients to zero. In this mode, gain through the matrix stage is 1.000.

Typical examples of matrix coefficients that will provide full range RGB to  $YC_BC_R$ , and  $YC_BC_R$  to full range RGB conversions are:

$$\begin{bmatrix} Y \\ C_B \\ C_R \end{bmatrix} = \begin{bmatrix} 0.5027 & 0.0976 & 0.2561 \\ -0.2899 & 0.4376 & -0.1477 \\ -0.3633 & -0.0711 & 0.4374 \end{bmatrix} \begin{bmatrix} G \\ B \\ R \end{bmatrix}$$

$$\begin{bmatrix} G \\ B \\ R \end{bmatrix} = \begin{bmatrix} 1.1677 & -0.3931 & -0.8164 \\ 1.1677 & 2.0248 & 0 \\ 1.1677 & 0 & 1.6025 \end{bmatrix} \begin{bmatrix} Y \\ C_B \\ C_R \end{bmatrix}$$

KEY signals may also be scaled by a programmable scaling factor. The KEY scaling coefficient (See HOST Programming Section) has the same resolution and bit weighting as the nine 3X3 matrix multiplier coefficients.

Typical examples of KEY scaler values that could be used are:

KEY scaler = 0.8563 for full range RGB to  $YC_BC_R$  conversions. KEY scaler = 1.1677 for  $YC_BC_R$  to full range RGB conversions.

#### MATRIX OUTPUT RESOLUTION

Full precision is maintained within the 3X3 matrix multiplier until the output is rounded to a 13-bit or 11-bit word, depending on the state of the RND8/10 control bit.

### 3X3 MATRIX MULITPLIER OUTPUT RESOLUTION FOR Y/G, CB/B AND CB/R CHANNELS

| RND8/10 | DESCRIPTION                                |  |  |  |  |  |  |

|---------|--------------------------------------------|--|--|--|--|--|--|

| 0       | Matrix output channels rounded to 13 bits. |  |  |  |  |  |  |

| 1       | Matrix output channels rounded to 11 bits. |  |  |  |  |  |  |

Output from the KEY scaler is also rounded and clipped based on the state of the RND8/10 control bit.

#### **KEY SCALER OUTPUT**

| RND8/10 | DESCRIPTION                              |  |  |  |  |  |  |

|---------|------------------------------------------|--|--|--|--|--|--|

| 0       | Output of KEY Scaler rounded to 11 bits. |  |  |  |  |  |  |

| 1       | Output of KEY Scaler rounded to 9 bits.  |  |  |  |  |  |  |

#### **OUTPUT OFFSET ADJUSTMENT**

Output offset adjustment is provided to allow a specified set of offsets to be added to the data streams. The control bits  $OOA_1$  and  $OOA_0$  (See Host Programming Section) determine which set of offsets is applied to the data.

# OOA<sub>1</sub> AND OOA<sub>0</sub> CONTROL BITS

| OOA <sub>1</sub> | OOA <sub>0</sub> | DESCRIPTION                                                                                                              |

|------------------|------------------|--------------------------------------------------------------------------------------------------------------------------|

| 0                | 0                | Offsets of 64, 512, 512 and 64 are added to the Y/G, C <sub>B</sub> /B, C <sub>R</sub> /R and KEY channels respectively. |

| 0                | 1                | Offsets of 64, 64, 64 and 64 are added to the Y/G, C <sub>B</sub> /B, C <sub>R</sub> /R and KEY channels respectively.   |

| 1                | 0                | Offsets of 0, 0, 0 and 0 are added to the Y/G, C <sub>B</sub> /B, C <sub>R</sub> /R and KEY channels respectively.       |

| 1                | 1                | Offsets of 0, 512, 512 and 0 are added to the Y/G, C <sub>B</sub> /B, C <sub>R</sub> /R and KEY channels respectively.   |

#### **OUTPUT CLIPPING**

In the output clipping block, the data is clipped to a specific number of bits. The CLP\_D<sub>1</sub> and CLP\_D<sub>0</sub> control bits (See Host Programming Section) determine the clipping mode that will occur.

## **OUTPUT MULTIPLEXER**

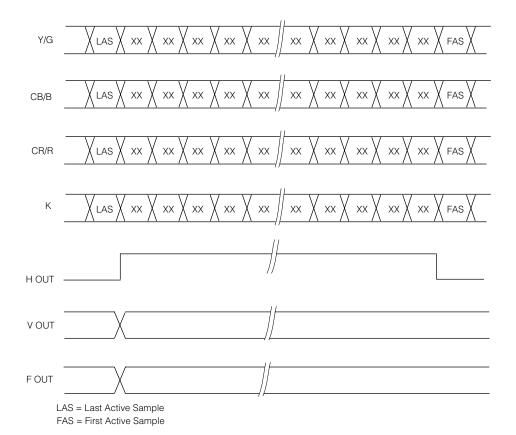

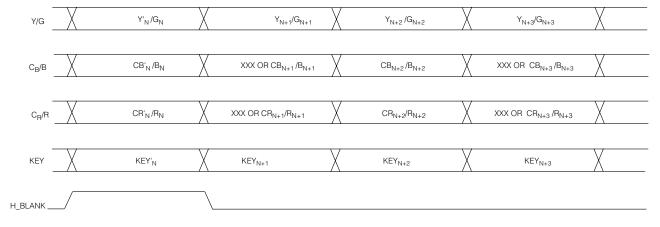

The MUXED\_OUT, 4:4:4:4/4:2:2:4\_OUT, SL/DL\_OUT and HVF\_OUT control bits (See Host Programming Section) determine the output data format.

## Dual Link ( $SL/\overline{DL}$ \_OUT = 0)

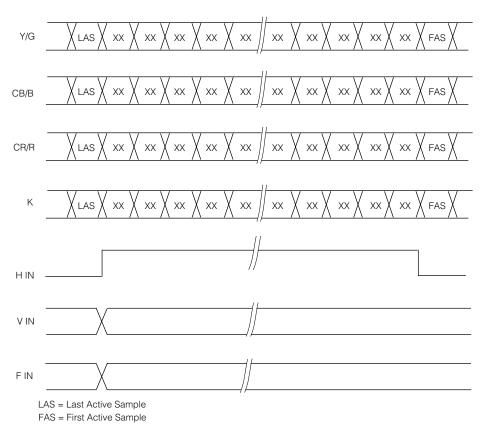

When  $\overline{\text{MUXED\_OUT}}$  and  $4:4:4:4/\overline{4:2:2:4}$ \_OUT are both set low, the device will multiplex the three channels of Y/G,  $C_B/B$  and  $C_R/R$  data into a single channel of 4:2:2 data as prescribed by SMPTE 125M. KEY information will be presented in a KEY:2:2 format where the  $C_B/C_R$  samples in the key channel are set to color blanking levels as outlined in ITU-R-601. This mode can only be used when the output data has been rounded to 10-bit or 8-bit unsigned data. The 4:2:2 data stream is presented on Processing Core output data port C5 and the KEY:2:2 data is presented on Processing Core output data port C8.

When  $\overline{\text{MUXED\_OUT}}$  is set low and  $4:4:4:4/\overline{4:2:2:4}$ \_OUT is set high, the device will multiplex the four channels of Y/G, C<sub>B</sub>/B, C<sub>B</sub>/R and KEY information into two streams of 4:2:2 and KEY:2:2 data as prescribed by SMPTE 125M. This mode can only be used when the output data has been clipped to 10-bit or 8-bit unsigned data. The 4:2:2 data stream is presented on Processing Core output data port C5 and the KEY:2:2 data is output on Processing Core output data port C8. Timing Reference Signals (TRS) may be inserted into the output data streams with such TRS signals conforming to the EAV/SAV

## CLP\_D<sub>1</sub> AND CLP\_D<sub>0</sub> CONTROL BIT OPERATION

| RND8/10 | CLP_D <sub>1</sub> | CLP_D <sub>0</sub> | DESCRIPTION                                                                                                                                                                                              |

|---------|--------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0       | 0                  | 0                  | Y/G, $C_B/B$ , $C_R/R$ Channels: Clipped to a 13-bit two's complement number (Values -4096 to 4095) KEY Channel: Clipped to an 11-bit two's complement number (Values -1024 to +1023)                    |

| 0       | 0                  | 1                  | Y/G, C <sub>B</sub> /B, C <sub>R</sub> /R Channels: Clipped to a 12-bit two's complement number (Values -2048 to 2047) KEY Channel: Clipped to an 11-bit two's complement number (Values -1024 to +1023) |

| 0       | 1                  | 0                  | Y/G, C <sub>B</sub> /B, C <sub>R</sub> /R, KEY Channels: Clipped to a 10-bit unsigned number (Values 0 to +1023)                                                                                         |

| 0       | 1                  | 1                  | Y/G, C <sub>B</sub> /B, C <sub>R</sub> /R, KEY Channels: Clipped to a 10-bit unsigned number (Values +4 to +1019)                                                                                        |

| 1       | 0                  | 0                  | Y/G, C <sub>B</sub> /B, C <sub>R</sub> /R Channels: Clipped to a 11-bit two's complement number (Values -1024 to 1023) KEY Channel: Clipped to an 9-bit two's complement number (Values -256 to +255)    |

| 1       | 0                  | 1                  | Y/G, C <sub>B</sub> /B, C <sub>R</sub> /R Channels: Clipped to a 10-bit two's complement number (Values -512 to +511) KEY Channel: Clipped to an 9-bit two's complement number (Values -256 to +255)     |

| 1       | 1                  | 0                  | Y/G, C <sub>B</sub> /B, C <sub>R</sub> /R, KEY Channels: Clipped to a 8-bit unsigned number (Values 0 to +255)                                                                                           |

| 1       | 1                  | 1                  | Y/G, C <sub>B</sub> /B, C <sub>R</sub> /R, KEY Channels: Clipped to a 8-bit unsigned number (Values +1 to +254)                                                                                          |

formats as outlined in SMPTE 125M. (See TRS Insertion Section).

When OUTPUT/INPUT is set high, Processing Core output port C5 corresponds to device data port P1 and Processing Core output port C8 corresponds to device data port P4. While OUTPUT/INPUT is set low, Processing Core output port C5 corresponds to device data port P5 and Processing Core output port C8 corresponds to device data port P8.

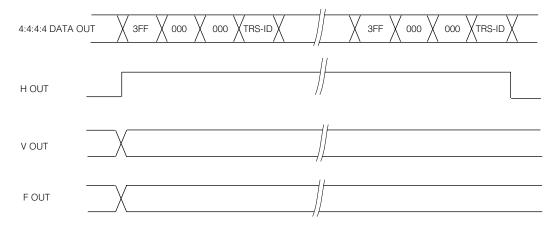

## Single Link ( $SL/\overline{DL}$ \_OUT = 1)

When generating single link output data, the 4:4:4:4 data stream (SMPTE RP174 compliant) exits the GF9105A Processing Core from Processing Core output C5. While OUTPUT/INPUT = 0 Processing Core port C5 corresponds to device data port P5(refer to Figure 4a). While OUTPUT/INPUT = 1 Processing Core Port C5 corresponds to device data port P1 (refer to Figure 4b). In this mode, the input clock (CLK) is operating at 54 MHz. Also, note that the MUXED\_OUT control bit must be set LOW (MUXED\_OUT = 0) and the 4:4:4:4/4:2:2:4\_OUT control bit must be set HIGH (4:4:4:4/4:2:2:4\_OUT = 1)

# MUXED\_OUT, 4:4:4:4/4:2:2:4\_OUT AND SL/DL\_OUT CONTROL BITS

| MUXED_OUT | 4:4:4:4/ <del>4:2:2:4</del> _OUT | SL/DL_OUT | DESCRIPTION                                              |  |  |  |  |  |

|-----------|----------------------------------|-----------|----------------------------------------------------------|--|--|--|--|--|

| 0         | 0                                | 0         | Output data in a 4:2:2:4 dual link multiplexed format.   |  |  |  |  |  |

| 0         | 1                                | 0         | Output data in a 4:4:4:4 dual link multiplexed format.   |  |  |  |  |  |

| 0         | 1                                | 1         | Output data in a 4:4:4:4 single link multiplexed format. |  |  |  |  |  |

| 1         | 0                                | XX        | Output 4:2:2:4 data in a non-multiplexed format.         |  |  |  |  |  |

| 1         | 1                                | XX        | Output 4:4:4:4 data in a non-multiplexed format.         |  |  |  |  |  |

When the device is configured for outputting non-multiplexed data and RND8/ $\overline{10}$  is set low, 13-bit two's complement, 12-bit two's complement, or 10-bit unsigned data may be output on Processing Core output data ports C5-C7 and 11-bit two's complement or 10-bit unsigned data output on the Processing Core output data port C8. The output data will be embedded within the physical 13-bit output ports as shown in the following tables. Note that when HVF\_OUT=1 and OUTPUT/ $\overline{\text{INPUT}}$ =1 b<sub>12</sub> of the GF9105As 13-bit two's complement output is not available. In this case, the 13-bit output data is clipped to a 12-bit two's complement number. Bit 12 (b<sub>12</sub>) of the 13 bit physical interface is used to output the H, V and F output signals. In this case, 13 bit output data is clipped 13 bit to a 12 bit two's complement number.

| OUTPUT/INPUT = 0, HVF_OUT = 0                                                                                 | 13 BIT PHYSICAL INTERFACE |                 |                 |                |                |                |                |                |                |                |                |                |                |

|---------------------------------------------------------------------------------------------------------------|---------------------------|-----------------|-----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|

| DATA PORT REFERENCE                                                                                           | b <sub>12</sub>           | b <sub>11</sub> | b <sub>10</sub> | b <sub>9</sub> | b <sub>8</sub> | b <sub>7</sub> | b <sub>6</sub> | b <sub>5</sub> | b <sub>4</sub> | b <sub>3</sub> | b <sub>2</sub> | b <sub>1</sub> | b <sub>0</sub> |

| Output Port: P5 <sub>120</sub> to P7 <sub>120</sub> 13-bit Two's Complement output                            | b <sub>12</sub>           | b <sub>11</sub> | b <sub>10</sub> | b <sub>9</sub> | b <sub>8</sub> | b <sub>7</sub> | b <sub>6</sub> | b <sub>5</sub> | b <sub>4</sub> | b <sub>3</sub> | b <sub>2</sub> | b <sub>1</sub> | b <sub>0</sub> |

| Output Port: P5 <sub>120</sub> to P7 <sub>120</sub> 12 bit Two's Complement output (b <sub>11</sub> extended) | b <sub>11</sub>           | b <sub>11</sub> | b <sub>10</sub> | b <sub>9</sub> | b <sub>8</sub> | b <sub>7</sub> | b <sub>6</sub> | b <sub>5</sub> | b <sub>4</sub> | b <sub>3</sub> | b <sub>2</sub> | b <sub>1</sub> | b <sub>0</sub> |

| Output Port: P5 <sub>120</sub> to P7 <sub>120</sub> 10 bit unsigned output                                    | 0                         | 0               | 0               | b <sub>9</sub> | b <sub>8</sub> | b <sub>7</sub> | b <sub>6</sub> | b <sub>5</sub> | b <sub>4</sub> | b <sub>3</sub> | b <sub>2</sub> | b <sub>1</sub> | b <sub>0</sub> |

| Output Port: P8 <sub>100</sub> 11-bit Two's Complement output                                                 | NA                        | NA              | b <sub>10</sub> | b <sub>9</sub> | b <sub>8</sub> | b <sub>7</sub> | b <sub>6</sub> | b <sub>5</sub> | b <sub>4</sub> | b <sub>3</sub> | b <sub>2</sub> | b <sub>1</sub> | b <sub>0</sub> |

| Output Port: P8 <sub>100</sub><br>10 bit unsigned output                                                      | NA                        | NA              | 0               | b <sub>9</sub> | b <sub>8</sub> | b <sub>7</sub> | b <sub>6</sub> | b <sub>5</sub> | b <sub>4</sub> | b <sub>3</sub> | b <sub>2</sub> | b <sub>1</sub> | b <sub>0</sub> |

| OUTPUT/INPUT = 0, HVF_OUT = 1                                                                                 |                     |                 |                 |                | 13 BIT         | PHYSI          | CAL IN         | ΓERFA          | CE             |                |                |                |                |

|---------------------------------------------------------------------------------------------------------------|---------------------|-----------------|-----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|

| DATA PORT REFERENCE                                                                                           | b <sub>12</sub>     | b <sub>11</sub> | b <sub>10</sub> | b <sub>9</sub> | b <sub>8</sub> | b <sub>7</sub> | b <sub>6</sub> | b <sub>5</sub> | b <sub>4</sub> | b <sub>3</sub> | b <sub>2</sub> | b <sub>1</sub> | b <sub>0</sub> |

| Output Port: P1 <sub>12</sub> , P2 <sub>12 or</sub> P3 <sub>12</sub>                                          | H, V or F<br>output | -               | -               | -              | -              | -              | -              | -              | -              | -              | -              | -              | -              |

| Output Port: P5 <sub>120</sub> to P7 <sub>120</sub> 13-bit Two's Complement output                            | b <sub>12</sub>     | b <sub>11</sub> | b <sub>10</sub> | b <sub>9</sub> | b <sub>8</sub> | b <sub>7</sub> | b <sub>6</sub> | b <sub>5</sub> | b <sub>4</sub> | b <sub>3</sub> | b <sub>2</sub> | b <sub>1</sub> | b <sub>0</sub> |

| Output Port: P5 <sub>120</sub> to P7 <sub>120</sub> 12-bit Two's Complement output (b <sub>11</sub> extended) | b <sub>11</sub>     | b <sub>11</sub> | b <sub>10</sub> | b <sub>9</sub> | b <sub>8</sub> | b <sub>7</sub> | b <sub>6</sub> | b <sub>5</sub> | b <sub>4</sub> | b <sub>3</sub> | b <sub>2</sub> | b <sub>1</sub> | b <sub>0</sub> |

| Output Port: P5 <sub>120</sub> to P7 <sub>120</sub> 10 bit unsigned output                                    | 0                   | 0               | 0               | b <sub>9</sub> | b <sub>8</sub> | b <sub>7</sub> | b <sub>6</sub> | b <sub>5</sub> | b <sub>4</sub> | b <sub>3</sub> | b <sub>2</sub> | b <sub>1</sub> | b <sub>0</sub> |

| Output Port: P8 <sub>100</sub> 11 bit Two's Complement output                                                 | NA                  | NA              | b <sub>10</sub> | b <sub>9</sub> | b <sub>8</sub> | b <sub>7</sub> | b <sub>6</sub> | b <sub>5</sub> | b <sub>4</sub> | b <sub>3</sub> | b <sub>2</sub> | b <sub>1</sub> | b <sub>0</sub> |

| Output Port: P8 <sub>100</sub> 10 bit unsigned output                                                         | NA                  | NA              | 0               | b <sub>9</sub> | b <sub>8</sub> | b <sub>7</sub> | b <sub>6</sub> | b <sub>5</sub> | b <sub>4</sub> | b <sub>3</sub> | b <sub>2</sub> | b <sub>1</sub> | b <sub>0</sub> |

When the device is configured for outputting non-multiplexed data and RND8/ $\overline{10}$  is set high, the output bit weighting is slightly modified. For non-multiplexed output formats, the device may output 11-bit two's complement, 10-bit two's complement or 8-bit unsigned data on Processing Core output data ports C5-C7, and 9-bit two's complement or 8-bit unsigned data may be output on Processing Core output data port C8. Note that when HVF\_OUT=1 and OUTPUT/ $\overline{INPUT}$ =1 the MSB of the 11-bit two's complement output is not available. In this case, the output data is clipped to a 10-bit two's complement number (-512 to + 511). Bit 12 (b<sub>12</sub>) of the physical interface is used to output the H, V and F output signals.

The output data will be embedded within the physical 13-bit output ports as shown below.

| OUTPUT/INPUT = 1, HVF_OUT = 0                                                                                 |                 |                 |                 |                | 13 BIT         | PHYSI          | CAL IN         | ΓERFAC         | CE             |                |                |                |                |

|---------------------------------------------------------------------------------------------------------------|-----------------|-----------------|-----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|

| DATA PORT REFERENCE                                                                                           | b <sub>12</sub> | b <sub>11</sub> | b <sub>10</sub> | b <sub>9</sub> | b <sub>8</sub> | b <sub>7</sub> | b <sub>6</sub> | b <sub>5</sub> | b <sub>4</sub> | b <sub>3</sub> | b <sub>2</sub> | b <sub>1</sub> | b <sub>0</sub> |

| Output Port: P1 <sub>120</sub> to P3 <sub>120</sub> 13 bit Two's Complement output                            | b <sub>12</sub> | b <sub>11</sub> | b <sub>10</sub> | b <sub>9</sub> | b <sub>8</sub> | b <sub>7</sub> | b <sub>6</sub> | b <sub>5</sub> | b <sub>4</sub> | b <sub>3</sub> | b <sub>2</sub> | b <sub>1</sub> | b <sub>0</sub> |

| Output Port: P1 <sub>120</sub> to P3 <sub>120</sub> 12-bit Two's Complement output (b <sub>11</sub> extended) | b <sub>11</sub> | b <sub>11</sub> | b <sub>10</sub> | b <sub>9</sub> | b <sub>8</sub> | b <sub>7</sub> | b <sub>6</sub> | b <sub>5</sub> | b <sub>4</sub> | b <sub>3</sub> | b <sub>2</sub> | b <sub>1</sub> | b <sub>0</sub> |

| Output Port: P1 <sub>120</sub> to P3 <sub>120</sub> 10 bit unsigned output                                    | 0               | 0               | 0               | b <sub>9</sub> | b <sub>8</sub> | b <sub>7</sub> | b <sub>6</sub> | b <sub>5</sub> | b <sub>4</sub> | b <sub>3</sub> | b <sub>2</sub> | b <sub>1</sub> | b <sub>0</sub> |

| Output Port: P4 <sub>100</sub> 11 bit Two's Complement output                                                 | NA              | NA              | b <sub>10</sub> | b <sub>9</sub> | b <sub>8</sub> | b <sub>7</sub> | b <sub>6</sub> | b <sub>5</sub> | b <sub>4</sub> | b <sub>3</sub> | b <sub>2</sub> | b <sub>1</sub> | b <sub>0</sub> |

| Output Port: P4 <sub>100</sub><br>10 bit unsigned output                                                      | NA              | NA              | 0               | b <sub>9</sub> | b <sub>8</sub> | b <sub>7</sub> | b <sub>6</sub> | b <sub>5</sub> | b <sub>4</sub> | b <sub>3</sub> | b <sub>2</sub> | b <sub>1</sub> | b <sub>0</sub> |

| OUTPUT/INPUT = 1, HVF_OUT = 1                                                      |                     |                 |                 |                | 13 BIT         | PHYSI          | CAL IN         | TERFAC         | CE             |                |                |                |                |

|------------------------------------------------------------------------------------|---------------------|-----------------|-----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|

| DATA PORT REFERENCE                                                                | b <sub>12</sub>     | b <sub>11</sub> | b <sub>10</sub> | b <sub>9</sub> | b <sub>8</sub> | b <sub>7</sub> | b <sub>6</sub> | b <sub>5</sub> | b <sub>4</sub> | b <sub>3</sub> | b <sub>2</sub> | b <sub>1</sub> | b <sub>0</sub> |

| Output Port: P1 <sub>120</sub> to P3 <sub>120</sub> 12 bit Two's Complement output | H, V or F<br>output | b <sub>11</sub> | b <sub>10</sub> | b <sub>9</sub> | b <sub>8</sub> | b <sub>7</sub> | b <sub>6</sub> | b <sub>5</sub> | b <sub>4</sub> | b <sub>3</sub> | b <sub>2</sub> | b <sub>1</sub> | b <sub>0</sub> |

| Output Port: P1 <sub>120</sub> to P3 <sub>120</sub> 10 bit unsigned output         | H, V or F<br>output | 0               | 0               | b <sub>9</sub> | b <sub>8</sub> | b <sub>7</sub> | b <sub>6</sub> | b <sub>5</sub> | b <sub>4</sub> | b <sub>3</sub> | b <sub>2</sub> | b <sub>1</sub> | b <sub>0</sub> |

| Output Port: P4 <sub>100</sub> 11 bit Two's Complement output                      | NA                  | NA              | b <sub>10</sub> | b <sub>9</sub> | b <sub>8</sub> | b <sub>7</sub> | b <sub>6</sub> | b <sub>5</sub> | b <sub>4</sub> | b <sub>3</sub> | b <sub>2</sub> | b <sub>1</sub> | b <sub>0</sub> |

| Output Port: P4 <sub>100</sub> 10 bit unsigned output                              | NA                  | NA              | 0               | b <sub>9</sub> | b <sub>8</sub> | b <sub>7</sub> | b <sub>6</sub> | b <sub>5</sub> | b <sub>4</sub> | b <sub>3</sub> | b <sub>2</sub> | b <sub>1</sub> | b <sub>0</sub> |

| OUTPUT/INPUT = 0, HVF_OUT = 0                                                                                |                 |                 |                 |                | 13 BIT         | PHYSI          | CAL IN         | ΓERFΑ          | CE             |                |                |                |                |

|--------------------------------------------------------------------------------------------------------------|-----------------|-----------------|-----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|

| DATA PORT REFERENCE                                                                                          | b <sub>12</sub> | b <sub>11</sub> | b <sub>10</sub> | b <sub>9</sub> | b <sub>8</sub> | b <sub>7</sub> | b <sub>6</sub> | b <sub>5</sub> | b <sub>4</sub> | b <sub>3</sub> | b <sub>2</sub> | b <sub>1</sub> | b <sub>0</sub> |

| Output Port: P5 <sub>120</sub> to P7 <sub>120</sub> 11 bit Two's Complement output                           | b <sub>10</sub> | b <sub>9</sub>  | b <sub>8</sub>  | b <sub>7</sub> | b <sub>6</sub> | b <sub>5</sub> | b <sub>4</sub> | b <sub>3</sub> | b <sub>2</sub> | b <sub>1</sub> | b <sub>0</sub> | 0              | 0              |

| Output Port: P5 <sub>120</sub> to P7 <sub>120</sub> 10 bit Two's Complement output (b <sub>9</sub> extended) | b <sub>9</sub>  | b <sub>9</sub>  | b <sub>8</sub>  | b <sub>7</sub> | b <sub>6</sub> | b <sub>5</sub> | b <sub>4</sub> | b <sub>3</sub> | b <sub>2</sub> | b <sub>1</sub> | b <sub>0</sub> | 0              | 0              |

| Output Port: P5 <sub>120</sub> to P7 <sub>120</sub><br>8 bit unsigned output                                 | 0               | 0               | 0               | b <sub>7</sub> | b <sub>6</sub> | b <sub>5</sub> | b <sub>4</sub> | b <sub>3</sub> | b <sub>2</sub> | b <sub>1</sub> | b <sub>0</sub> | 0              | 0              |

| Output Port: P8 <sub>100</sub> 9 bit Two's Complement output                                                 | NA              | NA              | b <sub>8</sub>  | b <sub>7</sub> | b <sub>6</sub> | b <sub>5</sub> | b <sub>4</sub> | b <sub>3</sub> | b <sub>2</sub> | b <sub>1</sub> | b <sub>0</sub> | 0              | 0              |

| Output Port: P8 <sub>100</sub><br>8 bit unsigned output                                                      | NA              | NA              | 0               | b <sub>7</sub> | b <sub>6</sub> | b <sub>5</sub> | b <sub>4</sub> | b <sub>3</sub> | b <sub>2</sub> | b <sub>1</sub> | b <sub>0</sub> | 0              | 0              |

When the device is configured for outputting multiplexed data, 8-bit or 10-bit unsigned data is transferred to the output data ports. Consult the tables of the Bit Weighting section for embedding 8 or 10 bits within 13 bit data ports. Note that when HVF\_OUT=1 and OUTPUT/INPUT=1, the MSB of the GF9105As 13 bit of the physical interfaces are used to output the H, V and F output signals.

| OUTPUT/INPUT = 0, HVF_OUT = 1                                                                                |                     |                 |                 |                | 13 BIT         | PHYSI          | CAL IN         | TERFA(         | CE             |                |                |                |                |

|--------------------------------------------------------------------------------------------------------------|---------------------|-----------------|-----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|

| DATA PORT REFERENCE                                                                                          | b <sub>12</sub>     | b <sub>11</sub> | b <sub>10</sub> | b <sub>9</sub> | b <sub>8</sub> | b <sub>7</sub> | b <sub>6</sub> | b <sub>5</sub> | b <sub>4</sub> | b <sub>3</sub> | b <sub>2</sub> | b <sub>1</sub> | b <sub>0</sub> |

| Output Port: P1 <sub>12</sub> , P2 <sub>12</sub> or P3 <sub>12</sub>                                         | H, V or F<br>output | -               | -               | -              | -              | -              | -              | -              | -              | -              | -              | -              | -              |

| Output Port: P5 <sub>120</sub> to P7 <sub>120</sub> 11 bit Two's Complement output                           | b <sub>10</sub>     | b <sub>9</sub>  | b <sub>8</sub>  | b <sub>7</sub> | b <sub>6</sub> | b <sub>5</sub> | b <sub>4</sub> | b <sub>3</sub> | b <sub>2</sub> | b <sub>1</sub> | b <sub>0</sub> | 0              | 0              |

| Output Port: P5 <sub>120</sub> to P7 <sub>120</sub> 10 bit Two's Complement output (b <sub>9</sub> extended) | b <sub>9</sub>      | b <sub>9</sub>  | b <sub>8</sub>  | b <sub>7</sub> | b <sub>6</sub> | b <sub>5</sub> | b <sub>4</sub> | b <sub>3</sub> | b <sub>2</sub> | b <sub>1</sub> | b <sub>0</sub> | 0              | 0              |

| Output Port: P5 <sub>120</sub> to P7 <sub>120</sub><br>8 bit unsigned output                                 | 0                   | 0               | 0               | b <sub>7</sub> | b <sub>6</sub> | b <sub>5</sub> | b <sub>4</sub> | b <sub>3</sub> | b <sub>2</sub> | b <sub>1</sub> | b <sub>0</sub> | 0              | 0              |

| Output Port: P8 <sub>100</sub> 9 bit Two's Complement output                                                 | NA                  | NA              | b <sub>8</sub>  | b <sub>7</sub> | b <sub>6</sub> | b <sub>5</sub> | b <sub>4</sub> | b <sub>3</sub> | b <sub>2</sub> | b <sub>1</sub> | b <sub>0</sub> | 0              | 0              |

| Output Port: P8 <sub>100</sub><br>8 bit unsigned output                                                      | NA                  | NA              | 0               | b <sub>7</sub> | b <sub>6</sub> | b <sub>5</sub> | b <sub>4</sub> | b <sub>3</sub> | b <sub>2</sub> | b <sub>1</sub> | b <sub>0</sub> | 0              | 0              |

| OUTPUT/INPUT = 1, HVF_OUT = 0                                                                                 |                 |                 |                 |                | 13 BIT         | PHYSI          | CAL IN         | ΓERFΑ          | CE             |                |                |                |                |

|---------------------------------------------------------------------------------------------------------------|-----------------|-----------------|-----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|

| DATA PORT REFERENCE                                                                                           | b <sub>12</sub> | b <sub>11</sub> | b <sub>10</sub> | b <sub>9</sub> | b <sub>8</sub> | b <sub>7</sub> | b <sub>6</sub> | b <sub>5</sub> | b <sub>4</sub> | $b_3$          | b <sub>2</sub> | b <sub>1</sub> | b <sub>0</sub> |

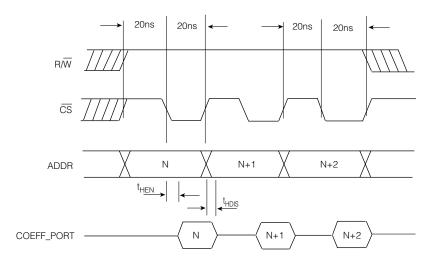

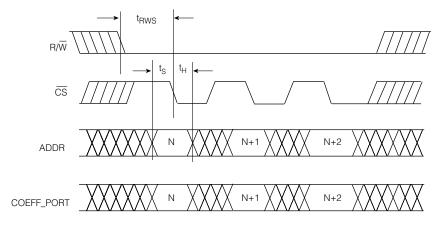

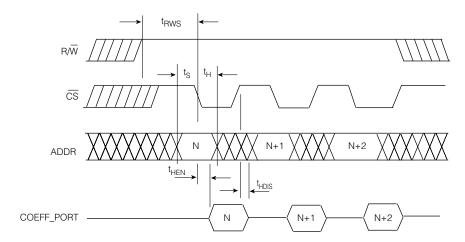

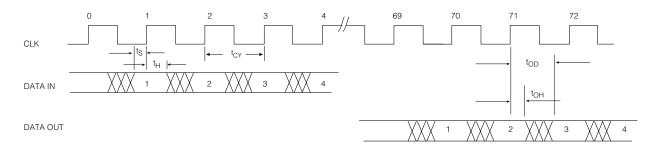

| Output Port: P1 <sub>120</sub> to P3 <sub>120</sub> 11 bit Two's Complement output                            | b <sub>10</sub> | b <sub>9</sub>  | b <sub>8</sub>  | b <sub>7</sub> | b <sub>6</sub> | b <sub>5</sub> | b <sub>4</sub> | b <sub>3</sub> | b <sub>2</sub> | b <sub>1</sub> | b <sub>0</sub> | 0              | 0              |