# W3011 1 GHz Quadrature Modulator

#### **Features**

- Guaranteed performance at 2.7 V power supply

- Output power of 3 dBm into 50  $\Omega$  load (single-ended) with 3 V operation

- Direct RF modulation with or without offset mixer

- Automatic power control (APC) capability

- Accurate 90° phase shifter for carrier

- Double-balanced active mixers minimize carrier feedthrough (origin offset)

- Low-current sleep mode

## **Applications**

- PDC 800 and American digital cellular mobile terminals

- Cellular base stations

## **Description**

The W3011 1 GHz Quadrature Modulator is a monolithic integrated circuit that provides direct

modulation of an RF carrier by I & Q baseband inputs. It is particularly suited for use in mobile and handheld cellular telephones designed to the IS-136 (North American 824 MHz to 849 MHz), PDC (Japan RCR-STD27 889 MHz to 958 MHz), and other digital personal-communications standards.

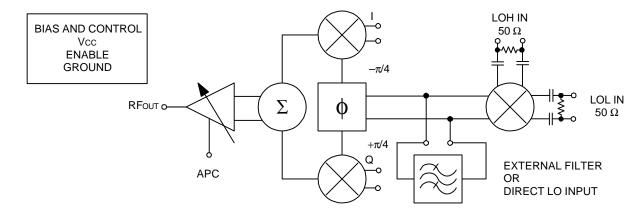

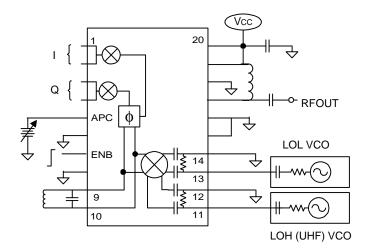

The circuit block diagram is shown in Figure 1. From two LO signals, LOL and LOH, the offset mixer produces an internal LO signal, which prevents the external VCOs from being pulled by the large transmitted signal. The phase shifter splits the LO signal into two carriers with 90° phase separation and equal amplitude.

These signals are fed to the in-phase (I) and quadrature-phase (Q) double-balanced mixers. The resulting signals are summed and fed into the output amplifier. This amplifier can provide 0 dBm linear output power, minimum, into a 50  $\Omega$  load.

The output power can be attenuated up to 50 dB by applying a control voltage to the APC input. Nominally, the output power is at maximum (+3 dBm) with VAPC > 2.2 V, and at minimum (-50 dBm) with VAPC < 0.8 V.

A CMOS/TTL-compatible logic input allows the device to be put into a powerdown mode in which less than 10  $\mu$ A of supply current is consumed.

Figure 1. Circuit Block Diagram

## **Pin Information**

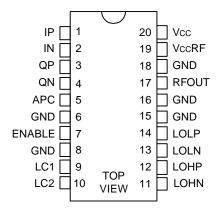

Figure 2. Pin Configuration

**Table 1. Pin Descriptions**

| Pin | Name   | Function                                           |

|-----|--------|----------------------------------------------------|

| 1   | IP     | Differential Baseband Input (in-phase)             |

| 2   | IN     | Differential Baseband Input (in-phase)             |

| 3   | QP     | Differential Baseband Input (quad-phase)           |

| 4   | QN     | Differential Baseband Input (quad-phase)           |

| 5   | APC    | Automatic Power Control dc Input                   |

| 6   | GND    | dc Ground                                          |

| 7   | ENABLE | Logic Enable                                       |

| 8   | GND    | dc Ground                                          |

| 9   | LC1    | Differential LO Input/External Filter              |

| 10  | LC2    | Differential LO Input/External Filter              |

| 11  | LOHN   | Differential High-frequency Local Oscillator Input |

| 12  | LOHP   | Differential High-frequency Local Oscillator Input |

| 13  | LOLN   | Differential Low-frequency Local Oscillator Input  |

| 14  | LOLP   | Differential Low-frequency Local Oscillator Input  |

| 15  | GND    | dc Ground                                          |

| 16  | GND    | dc Ground                                          |

| 17  | RFout  | Open-collector RF Output                           |

| 18  | GND    | dc Ground                                          |

| 19  | VccRF  | Positive Power Supply for RF Output Stage          |

| 20  | Vcc    | Positive Power Supply (nonoutput circuits)         |

## **Absolute Maximum Ratings**

Stresses in excess of the absolute maximum ratings can cause permanent damage to the device. These are absolute stress ratings only, as shown in Table 2. Functional operation of the device is not implied at these or any other conditions in excess of those given in the operations sections of the data sheet. Exposure to absolute maximum ratings for extended periods can adversely affect device reliability.

**Table 2. Absolute Maximum Ratings**

| Parameter                          | Symbol | Min  | Max | Unit |

|------------------------------------|--------|------|-----|------|

| Ambient Operating Temperature      | TA     | -35  | 85  | °C   |

| Storage Temperature                | Tstg   | -65  | 150 | °C   |

| Lead Temperature (soldering, 10 s) | _      | _    | 300 | °C   |

| Positive Supply Voltage            | Vcc    | -0.3 | 4.5 | V    |

| Power Dissipation                  | Pb     | _    | 650 | mW   |

| ac p-p Input Voltage               | Vp-p   | -0.3 | Vcc | V    |

| Digital Voltages                   | _      | -0.3 | Vcc | V    |

## **Handling Precautions**

Although protection circuitry has been designed into this device, proper precautions should be taken to avoid exposure to electrostatic discharge (ESD) during handling and mounting. Lucent Technologies Microelectronics Group employs a human-body model (HBM) and a charged-device model (CDM) for ESD-susceptibility testing and protection design evaluation. ESD voltage thresholds are dependent on the circuit parameters used to define the model. No industry-wide standard has been adopted for CDM. However, a standard HBM (resistance =  $1500 \Omega$ , capacitance = 100 pF) is widely used and, therefore, can be used for comparison purposes. The HBM ESD threshold presented here was obtained by using these circuit parameters:

| ESD Threshold Voltage                  |            |  |  |

|----------------------------------------|------------|--|--|

| Model                                  | Rating     |  |  |

| НВМ                                    | 2000       |  |  |

| CDM (corner pins) CDM (noncorner pins) | 500<br>500 |  |  |

## **Operating Ranges**

The W3011 operating ranges are shown in Table 3. Performance is not guaranteed over the full range of all conditions possible within this table. However, the table lists the ranges of external conditions in which the W3011 provides general functionality, which may be useful in specific applications, without risk of permanent damage. The conditions for guaranteed performance are described in Tables 4 and 5.

**Table 3. Operating Ranges**

| Parameter                                                                                       | Min | Max       | Unit  |

|-------------------------------------------------------------------------------------------------|-----|-----------|-------|

| Vcc                                                                                             | 2.7 | 3.6       | Vdc   |

| Ambient Operating Temperature                                                                   | -35 | 85        | °C    |

| fLO Direct Mode (pins 9 and 10)                                                                 | 800 | 1000      | MHz   |

| PLO Direct Mode (pins 9 and 10)                                                                 | 110 | 600       | mVp-p |

| Offset Local Oscillator (LOL) Frequency                                                         | 50  | 800       | MHz   |

| LOL Input Level                                                                                 | -15 | -3        | dBm   |

| UHF Local Oscillator (LOH) Frequency                                                            | 100 | 1300      | MHz   |

| LOH Input Level                                                                                 | -15 | -3        | dBm   |

| External dc Bias Voltage for I & Q Inputs with 0.282 Vrms ac Input Level: Differential ac Input | 1.2 | Vcc - 0.7 | Vdc   |

#### **Electrical Characteristics**

#### Table 4. dc and Digital Electrical Specifications

Conditions unless otherwise noted:  $2.7 \le Vcc \le 3.3 \text{ Vdc}$ ; TA =  $25 \text{ °C} \pm 3 \text{ °C}$ ; RL =  $50 \Omega$ , VAPC = 2.7 Vdc; fRF = 900 MHz, fLOL = 130 MHz, fLOH = 1030 MHz, -13 dBm < PLOL, PLOH < -5 dBm; I - I =  $0.4 \cos(2\pi t \cdot 80 \text{ kHz})$ , Q - Q =  $0.4 \cos(2\pi t \cdot 80 \text{ kHz} - \pi/2)$ , Vbias of I, I, Q, and Q = 1.22 Vdc.

| Parameter                                                                                                        | Symbol  | Min       | Тур      | Max       | Unit     |

|------------------------------------------------------------------------------------------------------------------|---------|-----------|----------|-----------|----------|

| Enable Input                                                                                                     | -       |           |          |           |          |

| Logic High Voltage                                                                                               | VIH     | 0.7 Vcc   | _        | Vcc + 0.4 | V        |

| Logic Low Voltage                                                                                                | VIL     | GND - 0.4 | _        | 0.3 Vcc   | V        |

| Logic High Current (VIH = 3.3 V)                                                                                 | lih     | _         | _        | 10        | μA       |

| Logic Low Current (VIL = 0.4 V)                                                                                  | lıL     | _         | _        | 10        | μA       |

| Powerup/down (after ENABLE change)                                                                               | _       | _         | _        | 4         | μs       |

| Power Supply Current                                                                                             |         |           |          |           |          |

| Powerdown (ENB = 0)                                                                                              | IPDN    | _         | 0.3      | 50        | μA       |

| Transmit (ENB = Vcc): (offset mixer on, APC @ max power) (offset mixer off, APC @ max power)                     | Icc(on) | _         | 52<br>50 | 66<br>64  | mA<br>mA |

| Transmit (ENB = Vcc): (offset mixer on, APC @ POUT < PMAX – 10 dB) (offset mixer off, APC @ POUT < PMAX – 10 dB) |         |           | 46<br>43 | _         | mA<br>mA |

## **Electrical Characteristics** (continued)

#### **Table 5. ac Specifications**

Conditions unless otherwise noted:  $2.7 \le VCC \le 3.3 \text{ Vdc}$ ; TA = 25 °C ± 3 °C; RL = 50  $\Omega$ , VAPC = 2.7 Vdc; fRF = 900 MHz, fLOL = 130 MHz, fLOH = 1030 MHz, -15 dBm < PLOL, PLOH < -5 dBm;  $I - I = 0.4 \cos(2\pi t \cdot 80 \text{ kHz})$ ,  $Q - \overline{Q} = 0.4 \cos(2\pi t \cdot 80 \text{ kHz} - \pi/2)$ , Vbias of I,  $\overline{I}$ ,  $\overline{Q}$ , and  $\overline{Q} = 1.22 \text{ Vdc}$ .

| Parameter                                                                                                                                                                                                                                                                          | Min    | Тур         | Max             | Unit       |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-------------|-----------------|------------|

| 1 & Q                                                                                                                                                                                                                                                                              |        |             |                 |            |

| I & Q Signal Path 0.5 dB Bandwidth                                                                                                                                                                                                                                                 | _      | 5           | _               | MHz        |

| I & Q Input Resistance                                                                                                                                                                                                                                                             | _      | 200         | _               | kΩ         |

| I & Q Input Capacitance to Ground                                                                                                                                                                                                                                                  | _      | 5           | _               | pF         |

| I & Q Input Differential Signal for Max Output                                                                                                                                                                                                                                     | _      | 0.8         | _               | Vp-p       |

| Offset Mixer                                                                                                                                                                                                                                                                       |        |             |                 |            |

| LOL Input Impedance                                                                                                                                                                                                                                                                | _      | 50          | _               | Ω          |

| LOH Input Impedance                                                                                                                                                                                                                                                                | _      | 50          | _               | Ω          |

| LO Input Impedance (pins LC1, LC2)                                                                                                                                                                                                                                                 | _      | 480//1      | _               | Ω//pF      |

| LOL Input IP3                                                                                                                                                                                                                                                                      | _      | 10          | _               | dBm        |

| Modulation Accuracy (Po∪T = −1 dBm)                                                                                                                                                                                                                                                |        |             |                 |            |

| Carrier Suppression (Pout = −1 dBm)                                                                                                                                                                                                                                                | _      | -35         | -28             | dBUSB      |

| Carrier Suppression (entire usable APC range)                                                                                                                                                                                                                                      | _      | _           | -26             | dBUSB      |

| Origin Offset (DQPSK inputs, all usable APC levels)                                                                                                                                                                                                                                | _      | _           | -23             | dBc        |

| Error Vector Magnitude (See Explanation of Error Vector Magnitude (EVM) Testing section.)                                                                                                                                                                                          | _      | 2.5         | 5               | %          |

| Lower Sideband (LSB) Suppression (See Figure 3.)                                                                                                                                                                                                                                   | _      | -43         | -34             | dBUSB      |

| RF Output                                                                                                                                                                                                                                                                          |        |             |                 |            |

| Output Power (0.8 Vp-p differential or single-ended 80 kHz sine-wave inputs to I and Q, with 90° between I and Q)                                                                                                                                                                  | -1     | 3           | _               | dBm        |

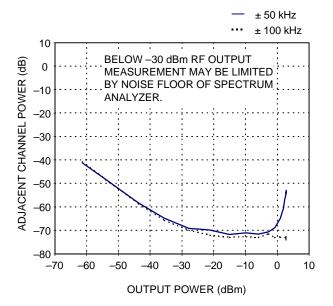

| Adjacent Channel Suppression (0.282 Vrms differential I and Q inputs, $\pi/4$ – DQPSK modulation, random data):                                                                                                                                                                    |        |             |                 |            |

| Per PDC (RCR STD-27):  ±50 kHz, All Usable APC Levels  ±100 kHz, All Usable APC Levels                                                                                                                                                                                             | _      | –65<br>—    | -55<br>-62      | dBc<br>dBc |

| ±100 kHz, Max RF Output (APC > 2.2) Per IS-136/IS-137 800 MHz Digital Mode:                                                                                                                                                                                                        | _      | <b>–</b> 75 | <del>-</del> 65 | dBc        |

| ±30 kHz, All Usable APC Levels<br>±60 kHz, All Usable APC Levels                                                                                                                                                                                                                   | _<br>_ | -45<br>-60  | -36<br>-50      | dBc<br>dBc |

| Noise Floor Suppression, Fc ± >100 kHz                                                                                                                                                                                                                                             | _      | -120        | -112            | dBc/Hz     |

| APC (Automatic Power Control) Function                                                                                                                                                                                                                                             |        |             |                 |            |

| Range of Usable Output Power Control for Japan PDC (RCR STD-27), from Max Power at APC = 2.7 V to Minimum APC Voltage Where Requirements for ACP and Carrier Suppression Are Still Met Using $\pi/4$ – DQPSK/ $\alpha$ = 0.5 Modulation at 0.282 Vrms Differential I and Q Inputs: |        |             |                 |            |

| Offset Mixer Not Used                                                                                                                                                                                                                                                              | 29     | 40          |                 | dB         |

| Offset Mixer Used                                                                                                                                                                                                                                                                  | 39     | 45          | _               | dB         |

| Output Power Variation Due to Temperature, within Usable Control Range                                                                                                                                                                                                             | _      | 4           | 6               | dB         |

| RF Power Change Time (after APC change)                                                                                                                                                                                                                                            | _      | _           | 2               | μs         |

| APC Voltage for Max Output Power                                                                                                                                                                                                                                                   | _      | 2.2         | _               | Vdc        |

| APC Voltage for Min Output Power                                                                                                                                                                                                                                                   |        | 0.8         | _               | Vdc        |

## **Explanation of Error Vector Magnitude (EVM) Testing**

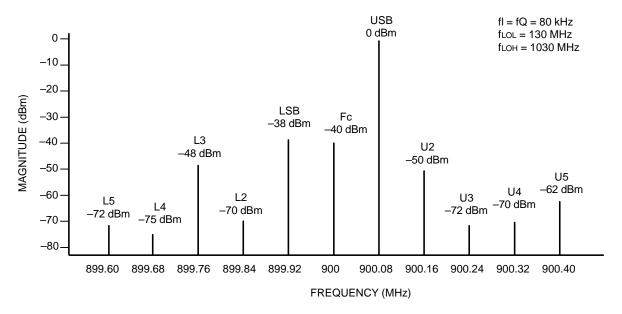

Error vector magnitude (EVM) is estimated by feeding signals to the W3011 as described above in Table 5. A typical narrowband, sine-wave modulation output spectrum appears in Figure 3.

Figure 3. W3011 Sine-Wave Modulation Output Spectrum

Data from this spectrum is used to estimate EVM by the formula:

EVM (%) =

$$100 \cdot [10^{P(L5)/20} + 10^{P(L4)/20} + 10^{P(L3)/20} + 10^{P(L2)/20} + 10^{P(LSB)/20} + 10^{P(U2)/20} + 10^{P(U2)/20} + 10^{P(U5)/20}]/10^{P(USB)/20}$$

The data presented in the spectrum above would yield:

This approximates worst-case digital modulation results, because the sine-wave modulation estimate assumes all spurious outputs are in phase and adds their magnitudes as scalars. In addition, this estimate includes full-amplitude measurements of spurious peaks that would appear in adjacent and alternate channels, where a receiver would otherwise provide attenuation. The L3 third-order intermodulation peak and LSB (lower sideband) are normally the unwanted output frequencies that dominate the EVM estimate.

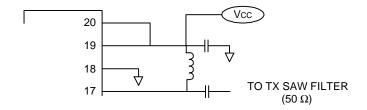

#### **RFOUT Matching: Basic Open Collector Termination**

The W3011 RF output uses an open collector output architecture. To operate properly, this requires that dc bias current be provided through the output pin (pin 17). Thus, the output matching network must always provide a shunt dc connection to the positive power supply. Examples of such a connection include a shunt-matching inductor or a shunt RF choke. Figure 4 illustrates a simple RFout matching configuration.

Figure 4. W3011 RF Output Diagram

#### **Offset Mixer**

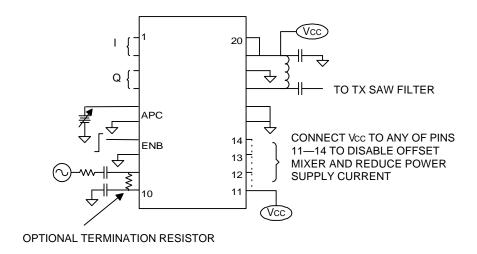

#### W3011 with Offset Mixer Disabled

If the offset mixer in the W3011 is not required for the frequency plan, the offset mixer may be turned off by connecting the positive supply (Vcc) to any or all of pins 11 (LOHN), 12 (LOHP), 13 (LOLN), or 14 (LOLP), as illustrated in Figure 5 below. Disabling the offset mixer reduces current consumption 2 mA to 3 mA. If pin 11 is connected to Vcc, pins 12, 13, and 14 must be connected to Vcc or no-connect (NC). Connect the RF VCO to either pin 9 or pin 10 through a low-impedance coupling capacitor, and connect the unused pin (10 or 9) through a similar capacitor to ground.

Figure 5. W3011 Application with Offset Mixer Disabled

#### Offset Mixer (continued)

#### **W3011 Using Offset Mixer**

If the W3011 offset mixer is required, two VCOs must be connected (see Figure 6). A low-frequency (VHF) oscillator may be dc-coupled to either pin 13 (LOLN) or pin 14 (LOLP) if the VCO contains a dc-blocking capacitor at its output. Otherwise, use a low-impedance series capacitor between the VCO output and the LOL input. The other LOL pin must be dc-grounded (no external capacitor for the grounded pin). As shown in Figure 1, there is a 50  $\Omega$  termination resistor on chip, connected between pins 13 and 14.

In the same way, as shown in Figure 6, one of the pins 11 (LOHN) or 12 (LOHP) must be connected to dc ground. The other pin is connected to a high-frequency (UHF) VCO, using either dc coupling (if the VCO contains a dc-blocking capacitor at its output) or a low-impedance series-coupling capacitor. There is also a 50  $\Omega$  termination resistor on chip connected between pins 11 and 12.

When the offset mixer is used, it is necessary to filter the offset mixer output signal with a parallel-tuned LC filter between pins 9 and 10. The resonant frequency of this filter should be approximately the center of the transmit RF band (for example, about 920 MHz for PDC 800). The filter should be adjusted for lowest EVM at RFOUT.

Figure 6. W3011 Application Using Offset Mixer

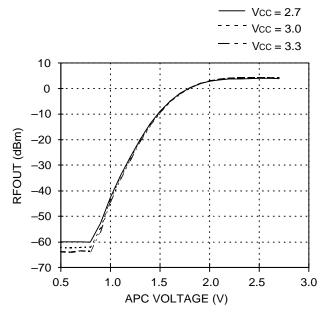

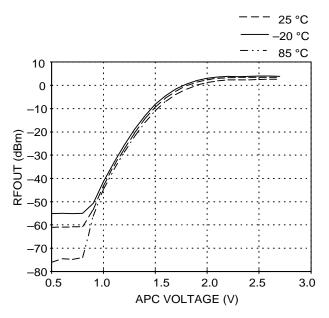

#### **Characteristic Curves**

Conditions unless otherwise noted: Vcc = 2.7; TA = 25 °C  $\pm$  3 °C; LOH = 755 MHz @ -12.5 dBm, LOL = 185 MHz @ -12.5 dBm; I/Q= 0.8 Vp-p  $\pi$ /4 - DQPSK;  $\alpha$  = 0.5 (random data); I/Q Vcm = 1.22 Vdc; LC filter = 10 nH//2.2 pF; RFOUT = 940 MHz.

Figure 7. Output Power vs. APC and Supply Voltage

Figure 8. Output Power vs. APC Voltage and Temperature

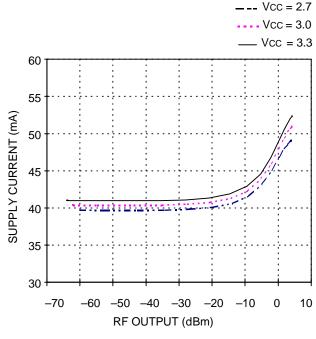

Figure 9. Supply Current vs. Output Power

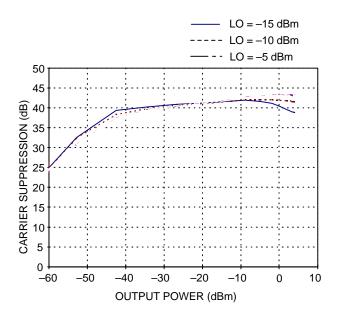

Figure 10. Carrier Suppression vs. Output Power and LO Level

## Characteristic Curves (continued)

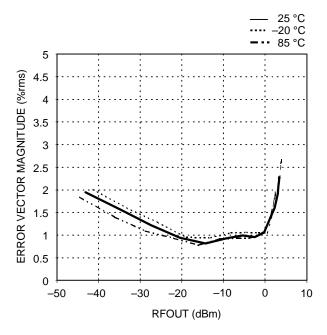

Figure 11. EVM vs. Output Power and Temperature

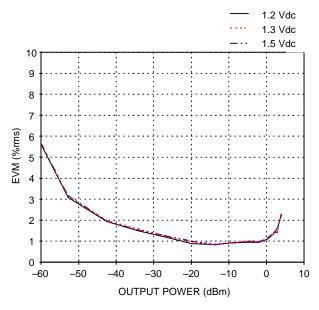

Figure 12. EVM vs. Output Power and I/Q Common-Mode Voltage

Figure 13. Adjacent Channel Power Suppression for PDC

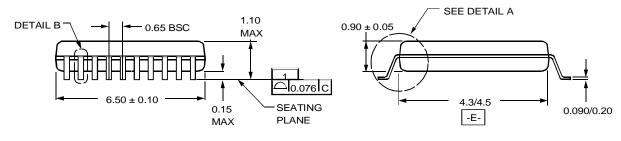

## **Package Outline**

#### 20-Pin TSSOP

Dimensions are in millimeters.

5-5499

## **Manufacturing Information**

This device may be assembled in any of the following locations: assembly codes P, M, or T.

#### **Ordering Information**

| Device Code     | Description                | Package                     | Comcode     |

|-----------------|----------------------------|-----------------------------|-------------|

| LUCW3011FCL     | 1 GHz Quadrature Modulator | 20-pin TSSOP                | 108 131 400 |

| LUCW3011FCL-TR* | 1 GHz Quadrature Modulator | 20-pin TSSOP, tape and reel | 108 131 426 |

| EVB3011         | Evaluation Board           | _                           | 108 131 913 |

Contact your Lucent Technologies Microelectronics Group Account Manager for minimum order requirements.

For additional information, contact your Microelectronics Group Account Manager or the following:

INTERNET: http://www.lucent.com/micro E-MAIL: docmaster@micro.lucent.com

Microelectronics Group, Lucent Technologies Inc., 555 Union Boulevard, Room 30L-15P-BA, Allentown, PA 18103 N. AMERICA

**1-800-372-2447**, FAX 610-712-4106 (In CANADA: **1-800-553-2448**, FAX 610-712-4106)

ASIA PACIFIC: Microelectronics Group, Lucent Technologies Singapore Pte. Ltd., 77 Science Park Drive, #03-18 Cintech III, Singapore 118256

Tel. (65) 778 8833, FAX (65) 777 7495

Microelectronics Group, Lucent Technologies (China) Co., Ltd., A-F2, 23/F, Zao Fong Universe Building, 1800 Zhong Shan Xi Road, Shanghai 200233 P.R. China Tel. (86) 21 6440 0468, ext. 316, FAX (86) 21 6440 0652 CHINA:

Microelectronics Group, Lucent Technologies Japan Ltd., 7-18, Higashi-Gotanda 2-chome, Shinagawa-ku, Tokyo 141, Japan

Tel. (81) 3 5421 1600, FAX (81) 3 5421 1700 **EUROPE:**

Data Requests: MICROELECTRONICS GROUP DATALINE: Tel. (44) 7000 582 368, FAX (44) 1189 328 148 Technical Inquiries: GERMANY: (49) 89 95086 0 (Munich), UNITED KINGDOM: (44) 1344 865 900 (Ascot),

FRANCE: (33) 1 40 83 68 00 (Paris), SWEDEN: (46) 8 594 607 00 (Stockholm), FINLAND: (358) 9 4354 2800 (Helsinki),

ITALY: (39) 02 6608131 (Milan), SPAIN: (34) 1 807 1441 (Madrid)

Lucent Technologies Inc. reserves the right to make changes to the product(s) or information contained herein without notice. No liability is assumed as a result of their use or application. No rights under any patent accompany the sale of any such product(s) or information

microelectronics group

JAPAN: